Fターム[5F033JJ30]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | シリサイド (585) | 高融点金属のシリサイド (433) | TaSi (63)

Fターム[5F033JJ30]に分類される特許

1 - 20 / 63

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

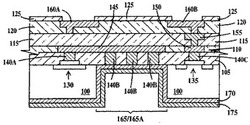

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体素子

【課題】熱(工程)に耐性のある配線構造を採用し、配線上の析出物の発生を抑制できる半導体素子を実現する。

【解決手段】半導体素子本体に接続する金材を含む配線パターンと、この配線パターンに一端側が接続され金材を含む接続端子と、前記半導体素子本体と前記配線パターンと前記接続端子とを覆う絶縁体と、を具備する半導体素子において、前記配線パターンあるいは接続端子の一方の面に一面が接し他面が前記絶縁体に接する面状のシリサイド体を具備したことを特徴とする半導体素子である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を提供する。またこのような半導体装置の作製方法を提供する。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110との間に、酸化しても導電性を有する導電材料(例えば金属)からなる導電層112を形成し、ここでは、導電プラグ110の下地膜を導電層112(Ag,Ni,Cu,Zn,In,Sn,Ir,Ru,Rh,Pd,Osから選ばれた少なくとも1種を材料として形成される。)とする。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

金属相互接続のための共形接着促進材ライナ

【課題】 金属相互接続のための共形接着促進材ライナを提供すること

【解決手段】 誘電体層を少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティを有するようにパターン化する。金属窒化物ライナをパターン化誘電体層の表面上に形成する。金属ライナを金属窒化物ライナの表面上に形成する。共形銅窒化物層を、原子層堆積(ALD)又は化学気相堆積(CVD)によって、金属ライナの直接上に形成する。Cuシード層を共形銅窒化物層の直接上に形成する。少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティは、電気めっき材料で充填される。共形銅窒化物層とCuシード層との間の直接接触は、強化された接着強度を与える。共形銅窒化物層をアニールして、露出した外側部分を連続的なCu層に変換することができ、このことはCuシード層の厚さを減すのに用いることができる。

(もっと読む)

貫通プラグ配線

【課題】半導体チップの基板を貫通するプラグにおいて、微細になるとプラグに接続する電極との接続抵抗が大きくなる、またリーク電流が大きくなる、あるいは絶縁破壊やストレスマイグレーションが生じる、という問題があった。これらの問題の生じにくい貫通プラグの製造方法を提供する。

【解決手段】半導体基板100の表面に設けられた電極パッド400と、基板裏面に設けられた接続電極380とを電気的に接続する貫通プラグ350の端部が、電極パッドおよび接続電極に部分的に食い込んだ構造とする。および、半導体基板から貫通プラグを絶縁する絶縁分離部210が、半導体基板表面側の絶縁膜205に部分的に食い込んだ構造とする。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

相互接続を作製するための方法

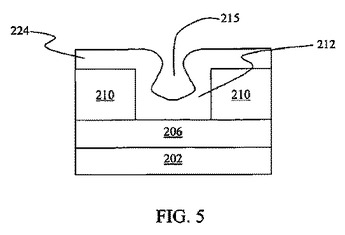

【課題】二重ダマシン構造を有する集積回路および余分な工程を削減し二重ダマシン構造を形成できる製造方法を提供する。

【解決手段】

二重ダマシン構造を製造する工程である。この工程は、スタックの上方に2個のマスクが形成される絶縁体層とストップ層を含むスタックを形成するものである。マスクのうちの1個は、絶縁体層のビアあるいはコンタクト開口を形成するのに用いられ、第ニのマスクは集積回路に相互接続のための凹部を形成するのに用いられる。

(もっと読む)

タングステン材料の原子層堆積法

【課題】ALDプロセスを使用して、均一性が良好で、ほとんどまたは全く汚染がなく、かつ導電率が高いつまり抵抗率が低いタングステン含有材料を堆積するための改良されたプロセスを提供する。

【解決手段】一実施形態では、プロセスチャンバ内に基板を位置決めするステップであって、該基板がこの上に配置されている下地層を含有するステップと、該基板をタングステン前駆体および還元ガスに順次曝してALDプロセス時に該下地層上にタングステン核形成層を堆積するステップであって、該還元ガスが約40:1、100:1、500:1、800:1、1,000:1以上の水素/ハイドライド流量比を含有するステップと、該タングステン核形成層上にタングステンバルク層を堆積するステップとを含む、基板上にタングステン含有材料を形成するための方法が提供される。該還元ガスはジボラン、シランまたはジシランなどのハイドライド化合物を含有している。

(もっと読む)

半導体装置およびその作製方法

【課題】無線信号から生成できる電流値及び電圧値の範囲内で駆動できるメモリを搭載した半導体装置を提供することを課題とする。また、半導体装置製造後にデータの書き込みを行える追記型のメモリを提供することも課題とする。

【解決手段】絶縁表面を有する基板上にアンテナと、アンチヒューズ型のROMと、駆動回路とを形成する。アンチヒューズ型のROMを構成する一対の電極の間に、シリコン膜とゲルマニウム膜との積層を設ける。この積層を有するアンチヒューズ型のROMは、書き込み電圧のバラツキを低減することができる。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】高温処理を行った場合でも素子の信頼性の劣化を抑制する。

【解決手段】磁気ランダムアクセスメモリは、磁化方向が固定された固定層11と磁化方向が反転可能な記録層13と固定層及び記録層の間に設けられた非磁性層12とを有する磁気抵抗効果素子MTJを具備するメモリセルアレイであって、磁気抵抗効果素子の下方に配置された前記メモリセルアレイ内の全ての導電層2、4、5は、W、Mo、Ta、Ti、Zr、Nb、Cr、Hf、V、Co、Niからなる群の中から選択された元素を含む材料で形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内に形成される銅プラグの接合リークの増加を抑制し、銅プラグの良好なコンタクトを達成できる半導体装置の製造方法を提供することである。

【解決手段】シリサイド層32を有する半導体基板1の上に絶縁膜38を形成し、さらに、シリサイド層32上の絶縁膜38にホール38fを形成し、ホール38f内とシリサイド層32の表面をクリーニングし、ホール38fの底面及び内周面に化学気相成長法によりチタン層41を形成し、銅拡散防止用のバリア層42をホール38f内のチタン層41上に形成し、銅層44をホール38f内に埋め込む工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を有している。層間絶縁膜1内に下部配線5を備えた第一層を準備する。第一層上にライナー膜11を設ける。層間絶縁膜12をライナー膜11上に設ける。層間絶縁膜12およびライナー膜11を貫通して下部配線5に達するトレンチ14を形成する。トレンチ14の側壁に沿った層間絶縁膜12上及びライナー膜11上と、下部配線5上に位置するトレンチ14の底部とにバリアメタル13を形成する。トレンチ14底部を物理エッチングすることにより、トレンチ14底部のバリアメタル13と下部配線5とを削り、円錐形状又は半球形状の孔6をトレンチ14の下側に設ける。トレンチ14の側壁上のバリアメタル13上及び孔6内に導電膜15を形成する。トレンチ14及び孔6内にCu膜19を埋め込む。

(もっと読む)

終端アルミニウム金属層のないメタライゼーション層積層体

最終メタライゼーション層のコンタクト領域(202A)上にアンダーバンプメタライゼーション層(211)を直接形成することによって、アルミニウムおよび対応する密着/バリア層などのほかの終端金属の形成を省略することができる。この結果、得られるバンプ構造(212)の熱的挙動および電気的挙動を向上させることができ、プロセスを大幅に簡略化することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】外部から曲げ等の物理的な力が加わり応力が生じた場合であってもトランジスタ等の素子の損傷を抑制する半導体装置を提供することを目的とする。

【解決手段】基板上に設けられ、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜を覆って設けられた第1の層間絶縁膜と、第1の層間絶縁膜上に、少なくとも不純物領域の一部と重なるように設けられた第2の導電膜と、第2の導電膜上に設けられた第2の層間絶縁膜と、第2の層間絶縁膜上に、開口部を介して不純物領域と電気的に接続するように設けられた第3の導電膜とを設ける。

(もっと読む)

炭素ナノチューブ配線の形成方法及びこれを用いる半導体素子配線の形成方法

【課題】界面破壊現象が発生しない炭素ナノチューブ配線の形成方法及びこれを利用した半導体素子配線の形成方法が開示されている。

【解決手段】基板上に酸化金属膜を形成した後、前記酸化金属膜上に前記酸化金属膜の表面を露出させる開口を含む絶縁膜パターンを形成する。前記開口に露出された前記酸化金属膜を炭素ナノチューブの成長が可能な触媒金属膜パターンに形成する。前記触媒金属膜パターンから炭素ナノチューブを成長させて炭素ナノチューブ配線を形成する。前述した炭素ナノチューブ配線の形成方法は、前記絶縁膜パターンと触媒金属膜パターンとの間で炭素ナノチューブが成長する現象を防止することができる。

(もっと読む)

1 - 20 / 63

[ Back to top ]