Fターム[5F033JJ34]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 窒化物 (3,695) | WN (404)

Fターム[5F033JJ34]に分類される特許

81 - 100 / 404

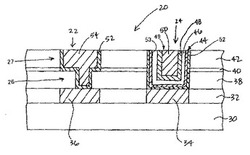

デュアル・ダマーシン相互接続構造および金属電極コンデンサを有する集積回路デバイスとその製造方法

【課題】本発明は、コンデンサを有する集積回路デバイスに関する。

【解決手段】集積回路デバイスおよびその製造方法は、相互接続構造およびコンデンサを含む。相互接続構造は、金属線および接点を含み、コンデンサは上部および下部金属電極を含む。この方法は、半導体基板に隣接する誘電体層を形成することと、第一誘電体層において相互接続構造の第一開口部およびコンデンサの第二開口部を同時に形成することとを含む。この方法は、相互接続構造を形成するために、第一導電層を選択的にデポジットさせて、第一開口部を充填することと、第二開口部にコンデンサを形成するために、その間にコンデンサ誘電体を有する上部および下部金属電極を形成することとを含む。集積回路デバイスは、金属電極を有し、デュアル・ダマシーン構造にも使用でき、統合される高密度コンデンサを提供する。この様に、コンデンサは、デュアル・ダマシーン相互接続構造と同一レベルに位置される。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

配線構造、及びそれを備えた液晶表示装置、並びに配線製造方法

【課題】配線を高精細化しても断線が生じ難い、信頼性の高い配線回路を実現する。

【解決手段】配線構造1は、ゲート電極17・17b・17cが配された基板9上に配される半導体層10と、ゲート電極17・17b・17c及び半導体層10が配された基板9上に配された第2層間絶縁膜13と、第2層間絶縁膜13上に配される配線18とを備え、第2層間絶縁膜13に形成されたコンタクトホール15内で、半導体層10と、配線18とが電気的に接続され、第2層間絶縁膜13は感光性樹脂材料からなり、さらに、コンタクトホール15内には導電性微粒子16が充填されており、導電性微粒子16によって、半導体層10と、配線18とが電気的に接続されている。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、Ru膜上にCVD法によりCu膜を成膜するにあたり、チャンバー1の壁部の温度を、副生成物であるCu(hfac)2の蒸気圧が成膜処理時のチャンバー1内の圧力と等しくなる温度以上で成膜原料であるCu(hfac)TMVSの分解温度未満に制御する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】表面性状が良好でかつ高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にウエハWを収容し、チャンバー1内にカルボン酸第1銅錯体、例えばCH3COOCuとこれを還元する還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】デポ物を充分除去することを可能とし、かつシリサイド層表面を酸化することが無い洗浄工程を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置100の製造方法は、Niを含むシリサイド層104の上面に形成された絶縁層をドライエッチングして、Niを含むシリサイド層104を露出させる工程と、Niを含むシリサイド層104を還元性を有する還元水で洗浄する工程と、を含むことを特徴とする。

(もっと読む)

半導体基板と半導体パッケージおよび半導体基板の製造方法

【課題】高信頼性の貫通電極を有する半導体基板を提供することを目的とする。

【解決手段】第1の開口部(4a)の内周と第2の開口部(4b)の間に位置する前記第1絶縁層(2)の面に凹部(6)が形成され、第2配線層(5)が、第1の開口部(4a)の内周面と凹部(6)および第2の開口部(4b)を経て第1の配線層(3)に電気接続されていることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】印加電界の履歴によって抵抗値が変化する抵抗変化層を有するスイッチ素子を多層配線中に形成し、かつ配線又は抵抗変化層の表面がダメージを受けることを抑制できるようにする。

【解決手段】この半導体装置は、第1配線層12、第2配線層16、及びスイッチビア35を備える。第1配線層12は第1配線32を有しており、第2配線層16は第2配線39を有している。スイッチビア35は、第1配線32と第2配線39を接続する。またスイッチビア35は、少なくとも底部に、抵抗変化層33を有しているスイッチ素子を有している。抵抗変化層33は、電界印加履歴に応じて抵抗値が変化する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液、無電解銅めっき方法、およびそのような無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】塩素イオンを1〜15ppm含む無電解銅めっき液を用いてめっきを行う。また、さらに例えばビス−(3−スルホプロピル)ジスルファイドのような、分子量50以上2000以下の硫黄系有機化合物を含有するめっき液を用いる。

(もっと読む)

半導体装置の製造方法

【課題】シード膜の酸化を抑制して、電気的信頼性の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有する基板100の少なくとも凹部1aの内面1b上に、シード膜5を形成する工程と、シード膜5上に、シード膜5の構成材料より酸化されやすい材料からなる保護膜6を形成する工程と、保護膜6に熱処理を施す工程と、熱処理が施された保護膜6の少なくとも一部を除去し、シード膜5の少なくとも一部を露出させる工程と、少なくとも一部が露出したシード膜5に電流を供給して、シード膜5上に凹部1aに埋め込まれるように電解めっきによりめっき膜7を形成する工程と、凹部1aに埋め込まれた部分以外のめっき膜7を除去する工程とを具備することを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】、配線層とその下層のプラグ層との配線抵抗を抑えながら下層のプラグの埋め込み性を向上させることが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Cu配線10と、Cu配線10の下層側でCu配線10と接触して接続されるCuプラグ20と、Cuプラグ20の底面側及び側面側に配置された、Cuに対してバリア性を有するBM膜240と、Cu配線10とCuプラグ20との内Cuプラグ20側に選択的に、かつCuプラグ20とBM膜240との間に介在するように配置された、BM膜240よりも前記導電性材料に対して濡れ性が高いRu膜242と、Cu配線10とCuプラグ20とが接触する箇所を少なくとも除くCu配線10の底面側と、Cu配線10の側面側とに配置された、Cuに対してバリア性を有するBM膜244と、を備えたことを特徴とする。

(もっと読む)

スカロップ状側壁を有するシリコン貫通ビア

【課題】 スカロップ状側壁を有するシリコン貫通ビアを提供する。

【解決手段】 基板、前記基板を覆う、1つ以上の誘電体層、及び前記基板を穿通して延伸し、スカロップ状の表面の側壁を有し、前記側壁に沿ったスカロップは約0.01μmより大きい深さを有するシリコン貫通ビア(TSV)を含む半導体デバイス。

(もっと読む)

発光装置の作製方法

【課題】平坦性の向上により、TFTの移動度を向上させ、TFTのオフ電流を低減する

。

【解決手段】基板上に非晶質構造の半導体膜を形成する工程と、前記半導体膜上に結晶化

を促進する金属元素を添加する工程と、加熱処理を行って、前記半導体膜を結晶構造の半

導体膜とする工程と、前記結晶構造の半導体膜に第1のレーザー光を照射する工程と、前

記結晶構造の半導体膜に第2のレーザー光を照射する工程とを有する。レーザー光を照射

する工程を2回設けることにより、結晶構造の半導体膜の平坦化を向上させることができ

る。その結果、TFTの移動度を向上させ、TFTのオフ電流を低減させることができる

。

(もっと読む)

エレクトロマイグレーション耐性を有するビア・ライン相互接続体

【課題】 エレクトロマイグレーション耐性を有するビア・ライン間相互接続構造体及びその製造方法を提供する。

【解決手段】 導電性ビアの上層金属ライナと、下方の金属ラインの下層金属ライナとの間に、ライナ・ライナ間接触を形成する。ライナ・ライナ間接触は、急激なエレクトロマイグレーションによる故障を抑制し、金属相互接続構造体のエレクトロマイグレーション耐性を強化する。少なくとも1つの誘電体材料部分は、上層金属ライナと下層金属ライナの間の直接接触を保証するように配置された複数の誘電体材料部分を含むことができる。代替的に、少なくとも1つの誘電体材料部分は、リソグラフィ・オーバーレイ変動の許容範囲内でライナ・ライナ間直接接触が形成されるのを保証するのに十分な、導電性ビア領域との横方向の重なりを有する領域の単一の誘電体部分を含むことができる。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

空隙を充填するべく低抵抗率のタングステン膜を堆積させる方法

【課題】抵抗率が低く、表面粗度が低く反射率が高いタングステンを、CVD法により基板上の間隙または凹状特徴部分に充填する方法を提供する。

【解決手段】基板に設けられた凹状部分を部分的に充填するタングステンバルクを堆積した後で、堆積されたタングステンの上部分を除去する。上部分の除去は、活性化されたフッ素種に基板を暴露することによって行われる。堆積されたタングステン粒子のうち急峻で突出している突起の頂点を選択的に除去することによって、除去処理は、凹状部分の側壁に沿ってタングステンを研磨することになる。堆積−除去のサイクルを複数回実行して、凹状部分を埋める。このようにして凹状部分が充填されると、CMPにおいてコアリング(coring)が発生しにくくなる。

(もっと読む)

半導体装置

【課題】ゲート電極の抵抗を低減しつつ、寄生容量やチップ面積の増大を抑制して、高周波特性を向上できる半導体装置を提供する。

【解決手段】実施形態の半導体装置は、ソース拡散層110とドレイン拡散層120とゲート電極100とにより構成された単位電界効果トランジスタを電気的に並列接続したマルチフィンガー構造の電界効果トランジスタと、この電界効果トランジスタの上部に電気的に接続した多層配線構造とを備え、ソース拡散層110の第2の配線(M1配線150)およびドレイン拡散層120の第3の配線(M1配線150)より上層にゲート電極100の第1の配線(M2配線160)を設けるものである。

(もっと読む)

半導体装置

【課題】製造ばらつきに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置は、基板(不図示)に形成された電気ヒューズ100を含む。電気ヒューズ100は、一端側に設けられた第1の配線112と、第1の配線112とは異なる層に形成された第2の配線122と、第1の配線112と第2の配線122と接触してこれらを接続する第1のビア130と、他端側に設けられ、第1の配線112と同層に第1の配線112から離間して形成された第3の配線142と、第3の配線142と第2の配線122と接触してこれらを接続し、第1のビア130よりも抵抗が低くなるよう構成された第2のビア132と、を含み、切断時に電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されて切断される。

(もっと読む)

めっき装置、めっき方法および半導体装置の製造方法

【課題】めっき膜における膜厚の均一性を向上させることができるめっき装置およびめっき方法、ならびに配線不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、基板Wの被めっき面W1が上向きとなるように基板Wを保持しつつ基板Wを回転させるホルダ3と、ホルダ3で保持された基板Wの周縁部W2に接触するカソード4と、ホルダ3で保持された基板Wの中央部W3に向けてめっき液Lを吐出し、かつアノードとしても機能するノズル6とを具備することを特徴とする、めっき装置1が提供される。

(もっと読む)

81 - 100 / 404

[ Back to top ]