Fターム[5F033JJ34]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 窒化物 (3,695) | WN (404)

Fターム[5F033JJ34]に分類される特許

101 - 120 / 404

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属配線部から、金属が層間絶縁膜に拡散することを抑制するためのシリコン窒化膜等から窒素や水素が拡散することによる影響を軽減した信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

(もっと読む)

半導体装置の製造方法

【課題】パターン内のボイドの発生を抑制する。

【解決手段】下層配線30に達するビアホール33を形成し、バリアメタル層34及びシード層35aを形成した後、電解めっき法により、ビアホール33内をめっき層で埋め込む。その際、シード層35a形成後に、ビアホール33の間口にオーバーハング101bが形成されることを想定し、例えば開口径70nm以下のビアホール33であれば、シード層35a形成後のビアホール33の開口径W2を20nm以上にする。これにより、そのシード層35aを用いた電解めっき時に、ビアホール33内がめっき層で埋まる前にその間口が塞がってボイドが発生するのを回避する。

(もっと読む)

半導体装置

【課題】製造バラツキに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置200は、基板(不図示)上に形成された上層ヒューズ配線112、下層ヒューズ配線122、および上層ヒューズ配線112の一端と接続され、上層ヒューズ配線112と下層ヒューズ配線122とを接続するビア130から構成される電気ヒューズ100を含む。上層ヒューズ配線112には、一端側で配線幅が狭くなった幅変動領域118が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

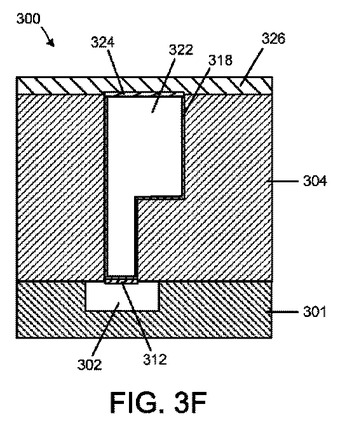

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置の製造装置

【課題】本願発明者らによると、VLSI(Very Large Scale Integration)のウエハ・プロセスにおいて、以下のような問題があることが明らかとなった。すなわち、プリ・メタル(Premetal)工程のタングステン・プラグ形成の準備工程としてのバリア・メタル・スパッタリング成膜時や第1層メタル配線層のスパッタリング成膜時に、ウエハからの脱ガスによる水分に起因する異物の発生がみられる。

【解決手段】本願発明は半導体集積回路装置の製造工程におけるプラズマ・プロセスで、プロセス・チャンバ外に設けられたアンテナにより、プラズマから発生する電磁波を受信することで、同チャンバ内の水分をインサイチュー・モニタ(In Situ Monitor)するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン法による配線パターン形成の際、低誘電率膜を層間絶縁膜に使った場合においてもビアホールや配線溝の側壁面における損傷や変形の発生を抑制し、同時に、下側配線パターンと上側配線パターンとのコンタクト抵抗を低減する半導体装置の提供。

【解決手段】活性素子を有する基板と、前記基板上において前記活性素子を覆う第1の層間絶縁膜と、前記第1の層間絶縁膜中に埋設された第1の配線層43Cuと、前記第1の層間絶縁膜上に形成された第2の層間絶縁膜52と、前記第2の層間絶縁膜中に埋設された第2の配線層と、を備え、前記第2の配線層は配線パターンと、前記配線パターンから延在し前記第1の配線層を構成する導体パターンの表面と直接に接触するビアプラグ50Vとを有し、前記配線パターンの底面および側壁面、および前記ビアプラグの側壁面は拡散バリア膜49A,49Bにより覆われることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線とバリア膜との密着性の低下、エレクトロマイグレーション耐性の低下、及び工程数の増加を抑制しつつ、めっき膜の膜厚がウェハ中心部とウェハ周辺部で異なることを抑制できる半導体装置の製造方法を提供する。

【解決手段】絶縁膜100に形成された溝102の側面及び底面に、添加元素を含む金属バリア膜120を形成する。次いで、金属バリア膜120上にシード膜142を形成し、さらにシード膜142をシードとしてめっき層(Cu膜144)を形成することにより、溝102内に金属膜140を埋め込む。次いで、金属バリア膜120及び金属膜140を熱処理することにより、金属バリア膜120と金属膜140の間に、金属バリア膜120を構成する金属、添加元素、及び金属膜140を構成する金属を含む合金層を形成し、かつ添加元素を金属膜140中に拡散させる工程とを備える。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアと電極パッドとの接合強度を増大させることにより、3次元配線構造を有する半導体装置の機械的強度を増大させる。

【解決手段】第1の半導体チップ100と第2の半導体チップ200とが貼り合わされている。第1の半導体チップ100の表面部に電極パッド104が形成されている。第2の半導体チップ200中に貫通ビア114が形成されている。電極パッド104には掘り込み部111が形成されており、当該掘り込み部111内に貫通ビア114の底部が埋め込まれている。

(もっと読む)

ルテニウム金属キャップ層を形成する方法

ルテニウム(Ru)金属の堆積を半導体デバイスの製造に統合することで、銅(Cu)金属のエレクトロマイグレーション及びストレスマイグレーションを改善する方法が供される。本発明の実施例は、NHx(x≦3)ラジカル及びHラジカルによって、金属層及びlow-k誘電材料を含むパターニングされた基板を処理することで、前記low-k誘電材料に対する前記金属層上でのRu金属キャップ層の選択形成を改善する方法を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグの配列ピッチが狭くなっても、隣接するコンタクトプラグ同士の短絡を防止し、コンタクトプラグ及びそれに接続する配線パターンを容易に形成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極11、ソース領域及びドレイン領域12を有するトランジスタと、トランジスタを覆う層間絶縁膜14と、層間絶縁膜14を貫通して設けられ、ソース領域及びドレイン領域12の一方に接続されたコンタクトプラグ15と、コンタクトプラグ15を覆う層間絶縁膜26と、層間絶縁膜26にゲート電極11の延在方向と同一方向に延在し、底部にコンタクトプラグ15の上面を露出する溝27と、コンタクトプラグ15に接続され溝27内に設けられたコンタクトプラグ28cと、コンタクトプラグ28cと一体化して層間絶縁膜26上に溝27を横切るように延在する配線パターン28wとを備える。

(もっと読む)

障壁表面上のコバルト堆積

本発明の実施形態は、障壁層上にコバルト層を堆積させた後、コバルト層上に銅または銅合金などの導電材料を堆積させるプロセスを提供する。一実施形態では、基板表面上に材料を堆積させる方法であって、基板上に障壁層を形成するステップと、気相成長プロセス(たとえば、CVDまたはALD)中に基板をジコバルトヘキサカルボニルブチルアセチレン(CCTBA)および水素に露出させて障壁層上にコバルト層を形成するステップと、コバルト層を覆うように導電材料を堆積させるステップとを含む方法が提供される。いくつかの例では、障壁層および/またはコバルト層は、熱プロセス、インサイチュプラズマプロセス、または遠隔プラズマプロセスなどの処理プロセス中にガスまたは試薬に露出させることができる。  (もっと読む)

(もっと読む)

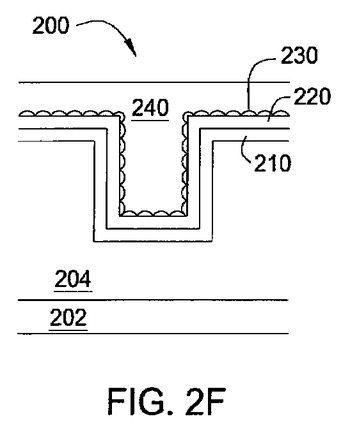

半導体装置の製造方法および半導体装置

【課題】本発明は、配線上面部からの金属拡散を抑制することができる、半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明では、半導体基板上の第一層間膜1内に形成された溝2内に、銅と第一金属元素とを含有する銅シード膜4を形成する。その後、銅メッキ処理を施す。その後、銅層の酸化が行われない第一雰囲気中にて第一熱処理を行う。そして、余分な銅合金金属層を除去し、溝2内に銅合金配線6を形成する。その後、酸素を含有する第二雰囲気中にて第二熱処理を行うことにより、銅合金配線6表面に、第一金属元素の酸化物である酸化物層7を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 Mnを含むバリア層を有するCu配線の高抵抗化を防止する半導体装置、および半導体装置の製造方法を提供する。

【解決手段】 半導体基板上方に形成された酸素を含有する絶縁層と、絶縁層中に形成された第1配線と、絶縁層中に形成され、第1配線と接続し、且つマンガン、酸素、及び銅からなる第2配線と、絶縁層内に形成され、第2配線と接続し、第1配線と離間して形成され、且つマンガン、酸素、及び銅によって埋め込まれた突起部と、を有し、突起部は、第2配線の下側に形成されており、突起部は、ビア形状および/または溝形状を有し、第2配線は、突起部よりも配線幅が太い。

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含む電気ヒューズ100であって、切断状態において、電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、上層配線110および下層配線120の一方と同層に上層配線110および下層配線120の一方の側方に形成されるとともに、上層配線110および下層配線120と電気的に接続された熱拡散用上層配線152aを含む熱拡散部150aとを含む。

(もっと読む)

金属相互接続のための共形接着促進材ライナ

【課題】 金属相互接続のための共形接着促進材ライナを提供すること

【解決手段】 誘電体層を少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティを有するようにパターン化する。金属窒化物ライナをパターン化誘電体層の表面上に形成する。金属ライナを金属窒化物ライナの表面上に形成する。共形銅窒化物層を、原子層堆積(ALD)又は化学気相堆積(CVD)によって、金属ライナの直接上に形成する。Cuシード層を共形銅窒化物層の直接上に形成する。少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティは、電気めっき材料で充填される。共形銅窒化物層とCuシード層との間の直接接触は、強化された接着強度を与える。共形銅窒化物層をアニールして、露出した外側部分を連続的なCu層に変換することができ、このことはCuシード層の厚さを減すのに用いることができる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

101 - 120 / 404

[ Back to top ]