Fターム[5F033JJ34]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 窒化物 (3,695) | WN (404)

Fターム[5F033JJ34]に分類される特許

41 - 60 / 404

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

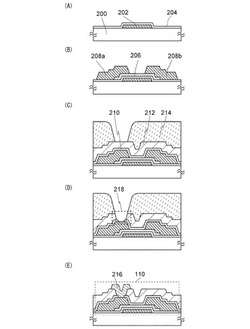

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

固体撮像素子とその製造方法

【課題】配線やコンタクトホールの寸法の微細化に際しても、コンタクト抵抗の低減を図ることが可能であり、且つ、暗電流の発生が少ない固体撮像素子およびその製造方法を提供する。

【解決手段】固体撮像素子1では、配線24と転送電極膜102とが、2層のコンタクトホールにより接続されている。下側のコンタクトホールAは、その底部にチタンシリサイド膜105が形成されている。そして、上側のコンタクトホールBは、チタンシリサイドを構成中に含まず、下側のコンタクトホールとの間が中間配線層としてのタングステン膜107により接続されている。ここで、上下の両コンタクトホールA,Bには、純粋なチタンは残っていない。また、撮像画素領域におけるフォトダイオード121の上方の層内レンズ膜127は、下方のコンタクトホールAに対して積層上方に選択的に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】Cuを主成分とする材料からなる最上層配線からのパッシベーション膜の剥離を防止することができる、半導体装置を提供する。

【解決手段】半導体装置1は、層間絶縁膜26と、絶縁材料からなり、層間絶縁膜26上に形成されたパッシベーション膜33と、銅を主成分とする材料からなり、層間絶縁膜26の表面とパッシベーション膜33との間に形成された最上層配線28と、アルミニウムを主成分とする材料からなり、パッシベーション膜33と最上層配線28の表面との間に介在され、最上層配線28の表面を被覆する配線被覆膜31とを含む。

(もっと読む)

半導体装置の製造方法及び成膜装置

【課題】バリアメタル膜の酸化を十分に抑制することができる半導体装置の製造方法及び成膜装置を提供する。

【解決手段】基板1の上方に導電膜5を形成し、導電膜5を覆う絶縁膜7を形成し、絶縁膜7のエッチングを行って、絶縁膜7に導電膜5の少なくとも一部を露出する開口部51を形成する。また、還元ガス雰囲気中で開口部51に紫外線を照射し、開口部51内に絶縁膜7及び導電膜5に接するバリアメタル膜9を形成し、バリアメタル膜9上に導電膜10を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】無機材料を用いてコストの低減を図りながら、応力集中によるクラックを回避しつつ、銅配線を覆うことができるパッシベーション膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10は、層間絶縁膜25と、層間絶縁膜25上に突出して形成され、銅を主成分とする材料からなる配線27と、配線27を覆うように形成されたパッシベーション膜30とを含む。パッシベーション膜30は、配線27側から順に第1窒化膜31、中間膜33および第2窒化膜32を積層した積層膜からなる。中間膜33は、第1および第2窒化膜31,32とは異なる絶縁材料(たとえば酸化物)からなる。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

半導体デバイス障壁層

【課題】本発明は、半導体デバイス要素のメタライゼーション及び誘電体材料の不活性化に使用される障壁層に関する。

【解決手段】半導体デバイスメタライゼーション要素用の障壁層は、要素くぼみ中に形成されたシリコン窒化物薄膜とシリコン窒化物薄膜上に形成された耐熱性金属薄膜を供する。デバイス要素は誘電体材料及び誘電体中に形成されたくぼみを含む。くぼみ内の誘電体材料の表面は、制御されたパラメータ下で窒素に露出される。くぼみの内部に隣接した誘電体材料の部分は、シリコン窒化物に変換される。

耐熱性金属は次に、くぼみの側壁に沿って、適合して堆積される。次に、耐熱性金属薄膜上にシード層が堆積され、次にくぼみ内に導電性金属が堆積される。次に、くぼみの外の過剰の金属を除去し、デバイスを平坦化するため、デバイスを研磨する。

(もっと読む)

絶縁膜および半導体装置

【課題】誘電率の低い絶縁膜であって、半導体装置の製造においてCMP法により当該絶縁膜上の膜を好適に除去することができるとともに、キャップ層を備えておらず、かつ、信頼性に優れた半導体装置の製造に好適に用いることができる絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成された絶縁膜であって、0.03〜20μmの膜厚を有し、ナノインデンターを用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする測定から求められる弾性率が、4.0GPa以上であることを特徴とする。

(もっと読む)

薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

(もっと読む)

基板貫通の相互接続部を形成する方法

【課題】表側と裏側とを有する基板を含むマイクロエレクトロニクス・デバイスに基板を貫通する相互接続部を形成する方法を提供する。

【解決手段】基板の表側に回路素子(134)を形成するステップと、回路素子(134)に達するトレンチ(138)を基板の裏側に形成するステップと、ポリマー絶縁材料からなる層(140)をトレンチ(138)内に形成するステップと、ポリマー絶縁材料からなる層(140)を基板の表側から露出させるために、回路素子(134)に開口(150)を形成するステップと、ポリマー絶縁材料からなる層(140)のうち開口(150)によって露出された部分を基板の表側から除去するステップと、回路素子(134)と電気的に通じている導電相互接続層(142)をトレンチ(138)内に形成するステップと、を有する。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

絶縁膜、積層体、半導体装置および半導体装置の製造方法

【課題】誘電率が低く、半導体装置の製造に適用した際に絶縁不良等の問題を生じにくい絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成されたものであって、フッ素系ガスでエッチングした際のエッチングレートが、SiO膜の0.75倍以下であることを特徴とする。前記重合性反応基は、芳香環と、当該芳香環に直接結合するエチニル基またはビニル基とを有するものであり、前記重合性化合物において、前記芳香環由来の炭素の数は、当該重合性化合物全体の炭素の数に対して、15%以上、38%以下であるのが好ましい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

41 - 60 / 404

[ Back to top ]