Fターム[5F033JJ35]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 酸化物 (221)

Fターム[5F033JJ35]に分類される特許

101 - 120 / 221

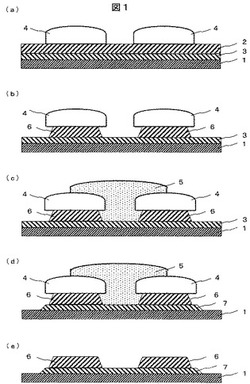

パターン形成方法及びそれを利用した表示装置の製造方法

【課題】

互いにパターン(平面形状)の異なる2種類以上の薄膜を積層した積層構造を形成する工程にて、1回のフォトリソグラフィ工程で夫々の薄膜形状を画定すること。

【解決手段】

基板1上に2層の薄膜3,2を順次成膜し、次に薄膜2の上面に形成された第1マスクパターン4を用いて薄膜2のエッチングを行い、第1の薄膜パターン6を形成する。その後、第1マスクパターン4を残した状態で第1マスクパターン4及び薄膜2の上に、有機材料のオフセット印刷、インクジェット印刷、又はディスペンサノズルによる追加塗布で第2マスクパターン5を形成する。最後に、薄膜3を第1マスクパターン4及び第2マスクパターン5を用いて第2の薄膜パターン7に成形し、続いて2つのマスクパターン4,5を除去する。以上の工程により、フォトリソグラフィが第1マスクパターン4を形成する1回のみに制限されるも、基板1の主面に所望の積層構造が形成される。

(もっと読む)

表示装置の作製方法

【課題】電気特性に優れ、信頼性の高い薄膜トランジスタを有する表示装置を生産性よく作製する方法を提案することを課題とする。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体膜を成膜し、微結晶半導体膜の表面からレーザビームを照射して微結晶半導体膜の結晶性を改善する。次に、結晶性が改善された微結晶半導体膜を用いて薄膜トランジスタを形成する。また当該薄膜トランジスタを有する表示装置を作製する。

(もっと読む)

半導体ウエハおよび半導体装置の製造方法

【課題】ウエハエッヂ部における膜はがれやパターン飛びを防止できる半導体ウエハおよび半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上には、トレンチ分離膜500により分離された活性領域にゲート構造400が形成されており、さらに、コンタクト層間膜103および、low−kビア層間膜すなわちV層とlow−k配線層間膜すなわちM層とが交互に成膜された多層配線構造が形成されている。第一の層間膜113から第五の層間膜153までのFineレイヤにおいては、M層のウエハエッヂ部は除去されているが、V層のウエハエッヂ部は除去されていない。また、コンタクト層間膜103のウエハエッヂ部は除去されていない。

(もっと読む)

Al合金膜を用いた低接触電気抵抗型電極およびその製造方法並びに表示装置

【課題】Al合金中の合金元素を少なくしても、透明酸化物導電膜との接触抵抗を低くすることのできる低接触電気抵抗型電極、およびこうした電極を製造するための有用な方法、並びにこうした電極を備えた表示装置を提供する。

【解決手段】本発明の低接触電気抵抗型電極は、酸化物透明導電膜と直接接触するAl合金薄膜からなる低接触電気抵抗型電極において、前記Al合金は、Alよりもイオン化傾向が小さい金属元素を0.1〜1.0原子%の割合で含有し、且つAl合金薄膜の酸化物透明電極と直接接触するAl合金薄膜表面は、最大高さ粗さRzで5nm以上の凹凸が形成されたものである。

(もっと読む)

表示装置の製造方法

【課題】フォト工程の低減を図った表示装置の製造方法。

【解決手段】第1導電型TFTと第2導電型TFTの各形成領域に、半導体層、第1絶縁膜、ゲート電極が形成され、前記半導体層のチャネル領域の各外側に第1導電型不純物領域が形成されている基板上に第2絶縁膜を形成し、前記第1導電型TFTの形成領域において当該ゲート電極を露出させることなく、前記第2導電型TFTの形成領域において当該ゲート電極のうち半導体層と交差する各辺の一部を露出させるようにして、ドレインおよびソースの各電極の接続用のコンタクトホールを形成し、多層導電層によって、前記第1導電型TFTの形成領域における前記各コンタクトホール、前記第2導電型TFTの形成領域において前記各コンタクトホールのゲート電極の一部を被うようにして、ドレインおよびソースの各電極を形成し、第2導電型不純物をドープして、半導体層に第2導電型不純物領域を形成する。

(もっと読む)

半導体装置

【課題】 Cu配線から低誘電率材料(Low−k材料)絶縁膜へのCuの拡散を防止することができるとともに、Cu配線の抵抗の増大を防止することができる半導体装置を提供すること。

【解決手段】 半導体装置1では、SiOCからなる層間絶縁膜5には、配線溝8が形成されている。配線溝8の内面(ビアホール6の側面6Bおよびトレンチ7の側面7B)には、SiO2からなる第1バリア膜9が形成されている。配線溝8の内面(第1バリア膜9の表面、トレンチ7の底面7Aおよび第1Cu配線2の露出面)には、第2バリア膜10が形成されている。配線溝8には、Cu配線部19が埋設されている。Cu配線部19の配線溝8との対向面(Cu配線11の底面11Aおよび側面11B、ならびに接続ビア18の底面18Aおよび側面18B)は、第2バリア膜10で被覆されている。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含有する配線層及びAlを含有するビアプラグ層を備える半導体装置に関し、配線層及びビアプラグ層の信頼性を向上させること。

【解決手段】Cuを含有する配線層と、前記配線層上に形成された層間絶縁膜と、前記配線層上の前記層間絶縁膜内に形成されたビアホールと、前記ビアホール内における前記配線層上に形成された第1のバリア層と、前記第1のバリア層上及び前記ビアホールの側壁に形成された第2のバリア層と、前記第2のバリア層上に形成され、Alを含有する導電層と、を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置、電気光学装置および半導体装置の製造方法

【課題】下地絶縁層の下層側に支持基板と別の材料からなる層を形成する場合でも、支持基板と半導体基板との貼り合わせ技術を好適に適用することのできる半導体装置、電気光学装置、および半導体装置の製造方法を提供する。

【解決手段】液晶装置などといった電気光学装置の素子基板などとして用いられる半導体層10xでは、支持基板10dの上に下地絶縁層12が形成されているとともに、下地絶縁層12の表面に電界効果型トランジスタ10yが形成されている。支持基板10eにおいて、電界効果型トランジスタ10yのチャネル領域1xに対向する位置には凹部10eが形成され、この凹部10eには埋め込みゲート電極4xが形成されている。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法、及び表示装置

【課題】蓄積容量素子の占有面積を小さくすることが可能な薄膜トランジスタアレイ基板、その製造方法、及び表示装置を提供すること

【解決手段】本発明にかかる薄膜トランジスタアレイ基板は、基板1上に形成され、ソース/ドレイン領域を有する半導体層3と、ゲート絶縁膜4と、ゲート電極5と、層間絶縁膜6aと、ソース/ドレイン領域に接続する配線電極71、72と、保護膜8と、配線電極72に接続する画素電極9と、半導体層3より延在して形成された下部容量電極3aと、ゲート電極5と同じ層によって形成され、ゲート絶縁膜4を介して下部容量電極3aの対面に配置された共通配線電極5aと、層間絶縁膜6aより膜厚の薄い誘電体膜(保護膜8)を介して共通配線電極5aの対面に配置された上部容量電極9aと、を備えるものである。

(もっと読む)

電気光学装置、及びその製造方法、電子機器

【課題】製造過程においてパーティクルの発生を防止し、表示性能を向上させることを可能とした電気光学装置、及びその製造方法、電子機器を提供する。

【解決手段】素子基板23上に設けられたTFT素子4と、TFT素子4を覆う有機絶縁層25上に設けられた画素電極26とが、有機絶縁層25に形成されたコンタクトホールを介して電気的に接続する構造を備えた有機EL装置10であって、少なくともTFT素子4のドレイン電極4b上のコンタクトホールが開口する領域に、導電性を有する金属酸化物膜24が設けられている。

(もっと読む)

アクティブマトリクス表示装置及びその製造方法

【課題】製造工程数を削減すると共に生産性を向上させる。

【解決手段】TFTアレイ基板11は、絶縁基板21を備えている。絶縁基板21上には、一部にポリシリコン層22が形成されている。このポリシリコン層22は、TFT素子14を構成する、チャネル領域22a、ソース領域22b及びドレイン領域22cを有している。ポリシリコン層22上には、ソース領域22b及びドレイン領域22cのそれぞれ一部を覆うように配線層23が形成されている。配線層23並びに配線層23が積層されていないポリシリコン層22には、両者の表面を覆うようにゲート絶縁膜24が形成されている。ゲート絶縁膜24上には、ゲート絶縁膜24を介してチャネル領域22aに対向する位置にゲート電極層25が形成されている。ゲート絶縁膜24表面の一部には、キャパシタ上部電極層26が形成されている。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法および液晶表示装置

【課題】TFTアレイ基板において、各配線間のクロストークを低減する。

【解決手段】TFTアレイ基板は、透明基板上に配置され、ゲート電極4aが分岐して延在するゲート配線1と、下部絶縁膜を介してゲート電極4aの上方を覆う半導体層3と、半導体層3を介してゲート電極4aの上側にそれぞれ一部が重なりかつゲート配線1とは交差しないようにそれぞれ別個に配置されたソース/ドレイン電極4b,4cと、ソース/ドレイン電極4b,4cを覆う上部絶縁膜と、この上部絶縁膜の上側においてゲート配線1と交差する方向に配置され、ソース電極4bに接続された上部ソース配線8と、ドレイン電極4cに電気的に接続された透明な画素電極11とを備え、少なくともゲート配線1と上部ソース配線8とが交差する交差部21では、ゲート配線1と上部ソース配線8との間に上記上部絶縁膜が配置されている。

(もっと読む)

半導体装置

【課題】金属抵抗素子の形成位置を画定するための写真製版技術における露光時にレジスト膜中に定在波が発生するのを防止して金属抵抗素子の寸法バラツキを低減する。

【解決手段】金属抵抗素子27の下地絶縁膜23は、金属抵抗素子27の長手方向において、金属抵抗素子27の接続孔25,25間における上面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27はその長手方向において下地絶縁膜23の曲面に起因して、コンタクト、コンタクト間における上面及び下面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27の形成位置を画定するための写真製版技術における露光時に、金属抵抗素子27を形成するための金属膜の上面及び下面で露光光の反射光は上記曲面により散乱されるので、反射光と入射光によるレジスト膜中での定在波の発生が防止される。

(もっと読む)

埋込配線の形成方法、表示装置用基板及び当該基板を有する表示装置

【課題】 埋込配線が形成される絶縁性基板の材料が耐熱性の高いものに限定されず、当該埋込配線の端子部の耐食性を向上でき、パターニングが少ない工程で且つ良好な膜厚精度で確実に行われる埋込配線の形成方法を提供する。

【解決手段】 絶縁性基板1の表面に形成したマスク17を用いて絶縁性基板1の表面を選択的に除去し、配線パターンに対応する平面形状を持つ溝18を形成する。マスク17を除去せずに絶縁性基板1の表面全体に金属ナノ粒子インクを塗布し、加熱により仮硬化させて金属ナノ粒子インク膜20を形成する。マスク17の剥離により膜20の当該マスク上にある部分を選択的に除去して溝18の内部に膜20を残す。加熱により溝18内の膜20を本硬化させ所望のゲート配線2を得る

(もっと読む)

電気光学装置製造方法

【課題】電気光学装置の端子部において界面抵抗の増加を抑制することである。

【解決手段】電気光学装置である液晶表示装置の下基板の画素部14において、画素用接続配線24、画素用透明導電膜28の導電積層膜が形成され、端子部20において、端子用接続配線124、端子用透明導電膜128の導電積層膜が形成される。ここで、画素用接続配線24と端子用接続配線124とは同一工程で形成され、下層側から上層側に向かって、チタン/アルミニウム/チタンがこの順に積層されて構成される。その後に平坦化膜64と保護絶縁膜62の開口部処理が行われ、表面エッチング液によって最上層のチタンの表面生成物が除去される。そして、画素用透明導電膜28と端子用透明導電膜128とが同一工程で形成される。

(もっと読む)

エッチング液組成物、基板上に所定のパターンを形成する方法及び前記基板上に所定のパターンを形成する方法により作成したアレイ基板

【課題】積層構造の金属膜を湿式エッチングする際に、テーパ角度が極端な低角度とならないようにして、断線が生じ難いパターンが得られるエッチング液組成物及びこのエッチング液組成物を使用した基板上に所定のパターンを形成する方法を提供する。

【解決手段】基板上に形成されたアルミニウム又はアルミニウム合金膜の表面にモリブデン膜が積層された積層構造の金属膜をエッチングして所定のパターンを形成するためのエッチング液組成物であって、リン酸濃度40〜70質量%、硝酸濃度0.5〜10質量%、酢酸濃度50〜15質量%、残部が水からなる。 (もっと読む)

(もっと読む)

表示装置及び表示装置の製造方法

【課題】基板の画素領域の外側のパッド領域に具備されたパッド電極が製造工程中に損傷するのを防止できる、表示装置及び表示装置の製造方法を提供する。

【解決手段】第1基板12上の画素領域A100に薄膜トランジスタを形成するとともに第1基板12上のパッド領域A110にパッド電極24を形成する段階と、薄膜トランジスタと連結する第1画素電極60及びパッド電極24を覆うパッド保護層62を同時に形成する段階と、パッド保護層62を除去し、パッド電極24を露出させる段階と、を含むことを特徴としており、パッド電極24上にパッド保護層62を形成することによって、第1画素電極60をパターニングする際のエッチング液によるパッド電極24の損傷を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの低抵抗化により配線抵抗の低抵抗化を図ると共に、バリアメタルのCuに対する拡散バリア性を高める。

【解決手段】層間絶縁膜10内に下層配線14が形成される。層間絶縁膜10及び下層配線14上にライナー膜20と層間絶縁膜22とが順次形成される。ライナー膜20と層間絶縁膜22内にビア28と上層配線30とが形成される。下層及び上層配線14,30とビア28とは、バリアメタル16,32とCu18,36とを有している。バリアメタル16,32は、RuxSinOy膜とRuxOy膜とRuxSin膜の少なくとも1つの膜17A,34Aと、RuxNy膜17B,34Bと、Ru膜17C,34Cとが積層されてなる。

(もっと読む)

エッチング液及びそれを用いたパターン形成方法とそれらを用いた液晶表示装置の製造方法

【課題】液晶表示装置の配線膜のエッチング加工において、溶け残り不良を抑制する。

【解決手段】酢酸濃度を5%以上含有する燐酸を主成分とするエッチング液、または、ヘキサン酸等の脂肪酸を含有するエッチング液により、レジスト上でのエッチング液の接触角を低減することができ、濡れ性を改善できる。このエッチング液を用いることによって、エッチング残りが生じ易いパターンにおいても、エッチング残りがないパターンを形成することができ、歩留まりよく液晶表示装置を製造できる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を有している。層間絶縁膜1内に下部配線5を備えた第一層を準備する。第一層上にライナー膜11を設ける。層間絶縁膜12をライナー膜11上に設ける。層間絶縁膜12およびライナー膜11を貫通して下部配線5に達するトレンチ14を形成する。トレンチ14の側壁に沿った層間絶縁膜12上及びライナー膜11上と、下部配線5上に位置するトレンチ14の底部とにバリアメタル13を形成する。トレンチ14底部を物理エッチングすることにより、トレンチ14底部のバリアメタル13と下部配線5とを削り、円錐形状又は半球形状の孔6をトレンチ14の下側に設ける。トレンチ14の側壁上のバリアメタル13上及び孔6内に導電膜15を形成する。トレンチ14及び孔6内にCu膜19を埋め込む。

(もっと読む)

101 - 120 / 221

[ Back to top ]