Fターム[5F033JJ35]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 酸化物 (221)

Fターム[5F033JJ35]に分類される特許

61 - 80 / 221

Cu膜の成膜方法および記憶媒体

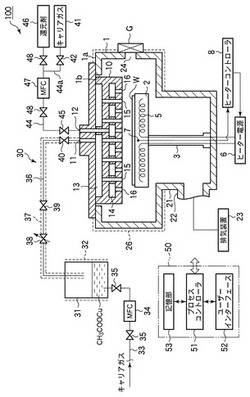

【課題】表面性状が良好でかつ高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にウエハWを収容し、チャンバー1内にカルボン酸第1銅錯体、例えばCH3COOCuとこれを還元する還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー内にウエハを搬入し、安定化させた後、ウエハを加熱しつつチャンバー内にCu錯体からなる成膜原料を気相状態で導入してウエハ上にCVD法によりCu膜を成膜し、成膜後、チャンバー内をパージして残留ガスを除去し、その後、チャンバーから基板を搬出するCu膜の成膜方法を実施するにあたり、パージの際に、ウエハへの入熱をCu膜成膜の際よりも低下させる。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供する。

【解決手段】ウエハW上の絶縁膜にビアホールとトレンチを形成し、この上にバリア層としてCVD−Ru膜を成膜する。チャンバー1内にウエハWを収容し、チャンバー1内に1価Cuβジケトン錯体であるCu(hfac)TMVSと、これを還元するアンモニア、還元性Si化合物、カルボン酸などの還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物

【課題】パターンの不良が減少した薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物を提供する。

【解決手段】基板上に導電性物質からなる導電膜を形成する段階と、導電膜上にネガティブフォトレジスト組成物からなるエッチングパターンを形成する段階と、エッチングパターンをエッチングマスクとして利用して導電膜をエッチングし、導電膜パターンを形成する段階とを含み、ネガティブフォトレジスト組成物は、アルカリ現像液に溶解性を有するヒドロキシル基を含有するノボラック樹脂10〜50重量部、第1光酸発生剤(特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、第2光酸発生剤(第1光酸発生剤とは構造の異なる特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、架橋結合剤1〜20重量部および溶媒10〜90重量部を含む。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

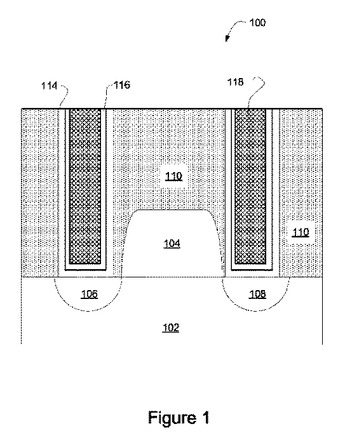

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】エアギャップ部を有し、かつ、高い機械的強度を有する半導体装置およびその製造方法を提供する。

【解決手段】酸素を含有する層間絶縁膜IL1の複数の溝部の側壁を被覆するバリア金属層ALが形成される。複数の溝部を充填するように配線金属層PCが形成される。層間絶縁膜IL1の酸素を熱拡散させることによってバリア金属層ALの少なくとも一部を酸化することで、酸化物バリア層BL1が形成される。配線金属層のうち複数の溝部の外側の部分を除去することによって、第1および第2の配線間領域IW1,IW2と第1〜第3の配線WR1〜WR3とが形成される。第1の配線間領域IW1を覆い、かつ第2の配線間領域IW2上に開口部OPを有するライナー膜LN1が形成される。開口部OPを介したエッチングが行なわれる。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】表示デバイスに用いられる薄膜トランジスタ基板の配線構造において、Al合金膜と透明画素電極を直接コンタクトさせることができるとともに、薄膜トランジスタの製造プロセス中に用いられるアミン系剥離液に対する腐食性を改善できるAl合金膜を開発し、それを備えた表示デバイスを提供する。

【解決手段】Geを0.2〜2.0原子%、および元素群X(Ag、In、Sn、Ni、Co、Cu)より選択される少なくとも1種の元素を含むと共に、希土類元素と高融点金属群(Ti、Ta、V、Nb、Mo、W、Cr、Zr、Hf)からなる元素群Qより選択される少なくとも1種の元素を0.02〜1原子%含み、かつ、粒径が100nmを超える析出物が10−6cm2あたり1個以下であるところに特徴を有するAl合金膜と、該Al合金膜を備えた表示装置。

(もっと読む)

電気的固体装置の製造方法、電気的固体装置、および電気光学装置

【課題】ウエットエッチングを採用した場合でも、未エッチング部分を発生させずに微細なパターンを形成することができる電気的固体装置の製造方法、電気的固体装置、および電気光学装置を提供すること。

【解決手段】電気光学装置の素子基板上に、スリット7bを備えた透光性の画素電極7aを形成するにあたって、透光性導電膜7の上にレジストマスク96を形成した後、ウエットエッチングを行なう。レジストマスク96において、マスク開口部96bを挟むマスク線状部96eの側面部96fは斜め上向きのテーパ面になっている。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

液晶表示装置

【課題】表示部周辺の引き回し線が多層構造となっている液晶表示装置において、走査線

とソース配線との繋ぎ換え配線部の配置を見直すことにより、より狭額縁化を達成するこ

とができる液晶表示装置を提供すること。

【解決手段】表示領域の周辺部の額縁領域PFに、ゲート絶縁膜の下部に形成された複数

のゲート配線41と、ゲート絶縁膜の上に形成された複数のソース配線42と、を備え、

前記ゲート配線41とソース配線42との間の電気的接続を行う繋ぎ換え配線部50を前

記コモン配線40に形成した切り欠き部54内に配置する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、配線上面部からの金属拡散を抑制することができる、半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明では、半導体基板上の第一層間膜1内に形成された溝2内に、銅と第一金属元素とを含有する銅シード膜4を形成する。その後、銅メッキ処理を施す。その後、銅層の酸化が行われない第一雰囲気中にて第一熱処理を行う。そして、余分な銅合金金属層を除去し、溝2内に銅合金配線6を形成する。その後、酸素を含有する第二雰囲気中にて第二熱処理を行うことにより、銅合金配線6表面に、第一金属元素の酸化物である酸化物層7を形成する。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成され、第2溝11と第1溝3とが対向する部分にビアホール12が貫通形成された後、スパッタ法により、CuMn合金からなる合金膜18が第2溝11およびビアホール12の側面および底面に被着される。そして、合金膜18における第2溝11の底面および第1配線5上に被着された部分が薄くされる。その後、合金膜18上に、Cuを主成分とする金属材料からなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスター中間体および薄膜トランジスターを提供する。

【解決手段】n−アモルファスSi半導体膜4の上に形成されたn+アモルファスSiオーミック膜4´と、n+アモルファスSiオーミック膜4´の上に形成されたバリア膜11と、バリア膜11の上に形成されたドレイン電極膜5およびソース電極膜6を有する薄膜トランジスター中間体であって、ドレイン電極膜およびソース電極膜は、バリア膜11に接して形成されているSr:0.2〜2モル%、酸素:1〜20モル%を含有し、残部がCuからなる酸素−ストロンチウム含有銅合金下地層12と、酸素−ストロンチウム含有銅合金下地層12の上に形成されたCu層13とからなる複合銅合金膜14が形成されている薄膜トランジスター中間体、並びにこの薄膜トランジスター中間体をプラズマ水素処理して得られた薄膜トランジスター。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面上における金属膜の膜剥がれの発生を防止することができながら、Cu配線中のMnの残留量を低減させることができる、半導体装置の製造方法を提供する。

【解決手段】第1配線5上に、SiおよびOを含む第2絶縁層6が形成された後、第2絶縁層6に、第2溝11およびビアホール12が形成される。次に、スパッタ法により、溝の内面およびビアホールの内面に、MnOからなる金属膜18が被着される。このとき、第2溝11の内面およびビアホール12の側面には、スパッタリングのエネルギーによって、金属膜18中のMnOが入り込み、MnSiOからなる第2バリア膜13が形成される。そして、金属膜18におけるビアホール12の底面に形成された部分が除去された後、ビアホール12にビア15が埋設されるとともに、第2溝11に第2配線14が埋設される。

(もっと読む)

成膜方法及び処理システム

【課題】例えばCu膜に対するバリヤ性及び密着性を高く維持することができる層構造を形成する成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器132内で、表面に凹部2を有する被処理体Wの表面に成膜処理を施す成膜方法において、遷移金属含有原料ガスを用いて熱処理により遷移金属含有膜210を形成する遷移金属含有膜形成工程と、元素周期表のVIII族の元素を含む金属膜212を形成する金属膜形成工程とを有するようにする。これにより、例えばCu膜に対するバリヤ性及び密着性を高く維持する。

(もっと読む)

銅めっきされた高アスペクト比のビア、及びその製造する方法

【課題】 最新のスケーリング技術の要件に適応することができ、適切に機能する実行可能なビアを一貫して生成できる、改善されたビア製造プロセスを提供すること。

【解決手段】 改善された高アスペクト比ビア及びそれを形成するための技術が提供される。1つの態様において、銅めっきされた高アスペクト比ビアを製造する方法が提供される。この方法は、以下のステップを含む。誘電体層内に高アスペクト比ビアをエッチングする。高アスペクト比ビア内及び誘電体層の1つ又は複数の表面の上に、拡散バリア領域を堆積させる。拡散バリア層の上に銅層を堆積させる。銅層の上にルテニウム層を堆積させる。高アスペクト比ビアを、ルテニウム層の上にめっきされた銅で充填する。この方法によって形成される銅めっきされた高アスペクト比ビアも提供される。

(もっと読む)

61 - 80 / 221

[ Back to top ]