Fターム[5F033KK17]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578)

Fターム[5F033KK17]の下位に属するFターム

Fターム[5F033KK17]に分類される特許

121 - 140 / 342

半導体装置の製造方法

【目的】膜切れの無い均一なシード膜を形成する半導体装置の製造方法を提供することを目的とする。

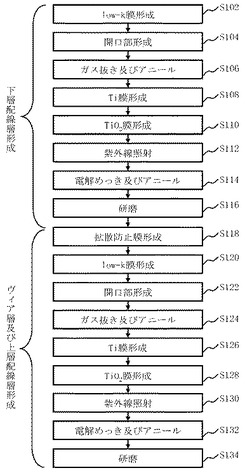

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S102)と、絶縁膜に開口部を形成する工程(S104)と、開口部内に光触媒膜を形成する工程(S110)と、Cuを含有する溶液に光触媒膜を浸漬させた状態で光触媒膜に紫外線を照射する工程(S112)と、開口部内に電解めっき法によりCuを埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置又はその製造方法を提供する。また、消費電力の低い半導体装置又はその製造方法を提供する。

【解決手段】ゲート電極として機能する透光性を有する導電層と、該透光性を有する導電層上に形成されるゲート絶縁膜と、ゲート電極として機能する透光性を有する導電層上にゲート絶縁膜を介して半導体層と、半導体層に電気的に接続されたソース電極又はドレイン電極として機能する透光性を有する導電層とで構成されている。

(もっと読む)

半導体装置及び回路基板

【課題】小型の半導体装置においても静電容量の大きなキャパシタを配置することが可能な構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、半導体素子8が形成された半導体基板2と、半導体基板2のパッシベーション膜12を介して配置され1方向に長く形成された開口部4aを有する平面型のスロットアンテナ4と、スロットアンテナ4と並列接続する共振用キャパシタ15とを備え、共振用キャパシタ15はチップ型素子となっている。

(もっと読む)

電気光学パネル、電気光学装置およびこれを搭載した電子機器

【課題】確実に検査工程の不良流出を防止し、かつ信頼性に影響を与えない。

【解決手段】実装端子と検査端子の間にアルミニウムを含まない配線を挟む。また、検査端子はCOGで実装するドライバICの下に配置する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】特性が向上した半導体装置の製造方法及び半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置の製造方法では、まず、絶縁性基板1上にゲート電極2を形成し、ゲート電極2上にゲート絶縁膜3を成膜する。そして、ゲート絶縁膜3上に非晶質半導体膜14を成膜し、非晶質半導体膜14に対して、レーザーアニールを行い、非晶質半導体膜14を微結晶半導体膜4に変換する。その後、微結晶半導体膜4に対してフッ酸処理を施し、フッ酸処理が施された微結晶半導体膜4上に、パターン端が微結晶半導体膜4のパターン端より外側に配置され、パターン端近傍においてゲート絶縁膜3と接するように非晶質半導体膜14を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗上昇や表面の電極パッドの突き抜けを防止できる構造を備えた固体撮像装置を提供する。

【解決手段】 半導体装置は、半導体基板6を貫通して形成された貫通電極5と、貫通電極5の上に形成され、貫通電極5と電気的に接続する導電体からなる導電体パッド14と、半導体基板6の表面に形成され、導電体パッド14と電気的に接続する配線層3とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含む配線について、配線抵抗を低く維持しつつ、しかも、ストレスマイグレーション耐性の劣化を伴うことなく、エレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜36と、層間絶縁膜36内に形成されたCuより成る配線50と、層間絶縁膜36と配線50の間に形成され、Ti膜42とTa膜44との積層膜より成るバリアメタル膜46とを有し、配線50表面に、TiとSiとを含む界面層54が形成されている。

(もっと読む)

半導体装置、通信モジュールおよび電子機器

【課題】安定した利得が得られるアンテナ素子を備えた半導体装置、通信モジュールおよび電子機器を提供すること。

【解決手段】半導体装置10は、能動素子が形成された能動面1aを有する半導体基板1と、能動面1a上に少なくとも1層以上の絶縁性樹脂層を介して設けられた第1の配線層8と、第1の配線層8に形成されたスロットアンテナ11と、スロットアンテナ11に接続された共振用キャパシタ13とを備え、スロットアンテナ11は、矩形状の開口部11bを有する平面型のアンテナ素子である。

(もっと読む)

薄膜トランジスタアレイ基板および薄膜トランジスタアレイ基板の修正方法

【課題】ゲート配線に断線等の不具合が発生しても、容易に修正することができる薄膜トランジスタアレイ基板を提供すること。

【解決手段】 ゲート配線とソース配線とが交差するように形成され、ゲート配線とソース配線とで囲まれた領域に画素電極が形成され、ゲート配線とソース配線の交差部近傍に薄膜トランジスタが形成されてなる薄膜トランジスタアレイ基板において、ゲート配線が断線した場合やゲート配線上に導電性の異物が存在する場合に該ゲート配線を迂回接続させるための修正用配線が、ゲート配線とソース配線との交差部近傍を除いた該ゲート配線に絶縁層を介して重畳形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の配線構造の信頼性を高める。

【解決手段】半導体装置は、素子103a,103bが形成された半導体基板101と、半導体基板101上に設けられた、少なくとも1層の金属層118及び水素含有ガスを原料ガスとしたプラズマCVD法により形成された第1の膜123を有する配線構造と、前記金属層118と非接触に前記半導体基板101上に形成されたTiNx(但し、0≦x)からなる第2の膜120とを具備する。

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ウエハレベルCSPにおいて、傾斜面を有する樹脂ポストが存在する場合であっても、樹脂ポスト近辺に微細な再配線を設計どおりに高密度に形成することができ、チップの小型化及び端子数の増加に対応することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、少なくとも一面に電極3を備えた基板2上の所定位置に、面状をなす第一頂部4aを備えた突起状の第一樹脂ポスト4を形成する工程αと、前記第一樹脂ポストの第一頂部上に、該第一頂部の一部を少なくとも露出させるように、該第一頂部よりも小さい面状をなす第二頂部5aを備えた突起状の第二樹脂ポスト5を形成する工程βと、を少なくとも備えたことを特徴とする。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

半導体装置の製造方法

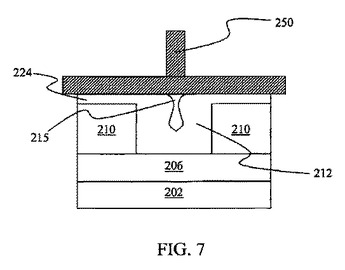

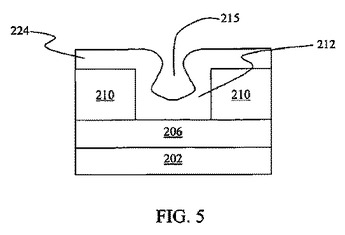

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】バリア膜を薄くする場合であっても良好なバリア性を確保し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の導電体32と、半導体基板上及び第1の導電体上に形成され、第1の導電体に達するコンタクトホール52と、コンタクトホールの上部に接続された溝54とが形成された、酸素を含む絶縁膜48と、コンタクトホールの側面並びに溝の側面及び底面に形成された酸化ジルコニウム膜62と、コンタクトホール内及び溝内における酸化ジルコニウム膜上に形成されたジルコニウム膜64と、コンタクトホール内及び溝内に埋め込まれたCuより第2の導電体70とを有している。

(もっと読む)

液晶表示装置及びその製造方法

【課題】データ線から発生する電気力線が画素電極に進入することを防止し、開口率を大きくすることができる液晶表示装置を提供する。

【解決手段】第1基板100Aは、データ線12を覆う無機絶縁膜15と、データ線12の上方において無機絶縁膜15上に設けられた突起状の有機絶縁膜21と、有機絶縁膜21を覆い、かつ、上方から見たときにデータ線12を覆うシールド共通電極26と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu膜からなる配線層と封止樹脂層との密着性を向上させ、両層間での剥離を防止し信頼性の高い半導体装置を提供する。

【解決手段】本発明に係る半導体装置1A(1)は、一面に電極3を配してなる半導体基板2と、前記半導体基板の一面を覆うように配され、前記電極と整合する位置に電極用の開口部αを有する絶縁樹脂層4と、前記絶縁樹脂層の一部を覆うように配され、前記開口部αを通して前記電極と電気的に接続される配線層5と、を少なくとも備える半導体装置であって、前記配線層は、Cu膜からなり、該配線層の表面が10nm〜300nmの凹凸形状を有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高融点金属元素を含むバリアメタル膜と組みあわせてCu配線パターンのバリアメタル構造を形成するCu−Mn合金層において、ストレスマイグレーション耐性を向上させると同時に、Cu配線パターンの抵抗を低減する。また、さらには配線中のボイド欠陥を低減する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上方に形成された酸素を含む絶縁膜と、前記絶縁膜に形成された凹部と、前記凹部の内壁に形成された銅を含む第1の膜と、前記第1の膜上方であって、前記凹部に埋め込まれた銅を含む第2の膜と、前記第1の膜と前記第2の膜の間にマンガンを含む酸化層と、を有する。さらに、前記構造に対し、電解メッキ法で銅配線を形成し、引き続き80℃〜120℃の温度で短時間の熱処理を行う。

(もっと読む)

121 - 140 / 342

[ Back to top ]