Fターム[5F033KK17]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578)

Fターム[5F033KK17]の下位に属するFターム

Fターム[5F033KK17]に分類される特許

61 - 80 / 342

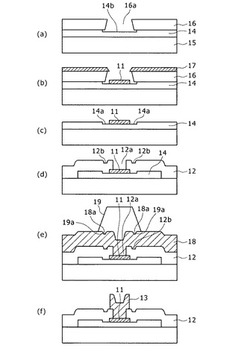

半導体素子およびその製造方法

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】駆動安定性を高め、積層工程での歩留まりを向上させ、実装形態での長期信頼性を向上させた薄型半導体チップの積層パッケージを実現する。

【解決手段】チップ表面に半導体素子110と、半導体素子110に信号を供給する配線と信号用電極と電源用電極とグランド用電極を有し、チップ裏面に信号用電極と電源用電極とグランド用電極を有し、チップ表面の電極とチップ裏面の電極とを電気的に接続する貫通配線を有し、チップの裏面を覆い、グランド用電極と接続した導体層120が形成されている複数の半導体チップ500、501とインターポーザ502とが積層されている半導体パッケージ。

(もっと読む)

有機発光表示装置及びその製造方法

【課題】酸化物半導体層と多結晶シリコン半導体層を共に用い得る有機発光表示装置及びその製造方法を提供する。

【解決手段】基板本体と、基板本体上に形成された第1ゲート電極及び第2半導体層と、第1ゲート電極及び第2半導体層の上に形成されたゲート絶縁膜と、ゲート絶縁膜を介在して第1ゲート電極及び第2半導体層上にそれぞれ形成された第1半導体層及び第2ゲート電極と、第1半導体層と少なくとも一部が相接して重畳した複数のエッチングストッパ層と、複数のエッチングストッパ層をそれぞれ露出する複数のコンタクトホールを有し、第1半導体層及び第2ゲート電極上に形成された層間絶縁膜と、層間絶縁膜上に形成され、複数のエッチングストッパ層を通じて第1半導体層とそれぞれ直接的/間接的に接続された第1ソース電極及び第1ドレイン電極と、層間絶縁膜上に形成され、第2半導体層と接続された第2ソース電極及び第2ドレイン電極とを含む。

(もっと読む)

薄膜トランジスタアレイの製造方法

【課題】凹凸のあるスルーホール部分であっても、層間絶縁膜の上下の導電層間で良好な電気的な接続が得られる、版を用いた印刷法による薄膜トランジスタアレイの製造方法を提供すること。

【解決手段】版に形成された画素電極パターンのスルーホールに対向する位置に保持されたインクの量を、画素電極パターンのスルーホールに対向する位置以外の部分に保持されたインクの量よりも多くすることによって、凹凸のあるスルーホール部分であっても、層間絶縁膜の上下の導電層間で良好な電気的な接続が得られる、版を用いた印刷法による薄膜トランジスタアレイの製造方法を提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuバンプを形成可能とする半導体装置を提供する。

【解決手段】半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上に形成されるCuから成るスタッドバンプ26とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ14とを有し、前記Cuワイヤ14と前記Cu配線層9との間には合金層13が配置されることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体デバイスのための電力グリッド構造体及びその製造方法

【課題】 半導体デバイスに電力を提供する電力グリッド構造体及びその製造方法を提供する。

【解決手段】 本発明の一実施形態は、誘電体層の内部に形成された第1の導電性材料のスタッドと、底部及び側壁を有する第2の導電性材料のビアであって、底部及び側壁は導電性ライナで覆われ、底部はスタッドの直接上に形成され、かつ、導電性ライナを通してビアと接触した状態にある、ビアと、ビアの側壁において導電性ライナを通してビアに接続する第3の導電性材料の1つ又は複数の導電性パスとを含むことができる半導体構造体を提供する。半導体構造体を製造する方法も提供される。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

半導体素子の接触部及びその製造方法並びに表示装置用薄膜トランジスタ表示板及びその製造方法

【課題】比抵抗が低いながらも接触特性が良い接触部を含み、優れた接触特性を有する接触部を含む薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板と、ゲート線と、ゲート絶縁層と、半導体層と、データ線と、前記データ線と分離されているドレーン電極と、前記半導体層を覆っていて前記ドレーン電極を露出する第1接触孔、前記ゲート線の一部を露出する第2接触孔、前記データ線の一部を露出する第3接触孔を有する保護膜と、前記第1接触孔を通じて前記ドレーン電極と連結される画素電極と、前記第2接触孔を通じて前記ゲート線と連結されているゲート接触補助部材と、前記第3接触孔を通じて前記データ線に連結されるデータ接触補助部材とを含み、前記データ接触補助部材は凹凸を有することを特徴とする薄膜トランジスタ表示板を提供する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

集積回路構造

【課題】銅ピラーを有するウェハ裏面構造を提供する。

【解決手段】集積回路構造は、前面および背面を有する半導体基板と、半導体基板を貫通する導電ビアとを含む。導電ビアは、半導体基板の背面に延伸する後端を含む。再分配線(RDL)が半導体基板の背面上にあり、導電ビアの後端に電気的に接続される。パッシベーション層がRDL上にあり、パッシベーション層には開口があり、RDLの一部が開口を通して露出される。銅ピラーは開口内に一部を有し、RDLに電気的に接続される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

61 - 80 / 342

[ Back to top ]