Fターム[5F033KK21]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578) | Ta (904)

Fターム[5F033KK21]に分類される特許

81 - 100 / 904

半導体装置の製造方法

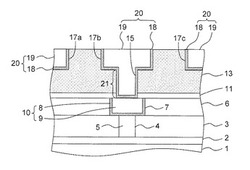

【課題】 半導体装置の多層配線において配線間隔を低減させても所定の低比誘電率を維持できるとともに、電気的特性の劣化などを抑制できる多孔性の層間絶縁膜の形成方法を提供する。

【解決手段】 半導体基板1上に形成される配線構造を構成し、空孔を有する多孔性絶縁膜13を得るための母体となる母体絶縁膜を気相成長法を用いて堆積する。この際、多孔性絶縁膜13の比誘電率、配線20間の間隔や絶縁耐圧のような、配線構造を決める因子に要求される設計値に応じて、多孔性絶縁膜13の分子骨格形成材料の流量に対する多孔性絶縁膜13の空孔形成材料の流量の比の、少なくとも範囲をまず決定する。この後、決定した流量比の範囲で母体絶縁膜を堆積し、この母体絶縁膜に熱や紫外線などのエネルギーを与えて空孔を有する多孔性絶縁膜13にする。

(もっと読む)

半導体装置

【課題】pn接合ダイオードの接合面積を大きくし、かつコストダウンを可能とすること。

【解決手段】半導体基板10とpn接合を形成する第1拡散領域32を含む第1pnダイオード33を含み、前記半導体基板上に形成された電子回路20と、前記電子回路とスクライブライン26との間の前記半導体基板内に設けられ前記電子回路を囲み前記第1拡散領域と同じ導電型であり前記半導体基板とpn接合を形成する第2拡散領域24を、含む第2pnダイオード23と、前記電子回路と前記スクライブラインとの間の前記半導体基板上に、前記第2拡散領域と重なるように設けられ、前記電子回路を囲む金属層18と、を具備する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】プローブ針の先端を研磨する時間を短縮することと接触抵抗を低く安定させること。

【解決手段】半導体基板上に形成された電子回路と、前記半導体基板上に形成され、前記電子回路と電気的に接続し、金属膜34と前記金属膜より硬い材料の層36とを備え、上視した場合前記層と前記金属膜とが配置された第1領域40と、前記金属膜が配置され前記層が形成されない第2領域42とを備えるパッド16と、を具備する半導体装置。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

半導体装置の製造方法

【課題】微細で良好な形状のコンタクトホールを有する半導体装置の製造方法を提供する。

【解決手段】絶縁膜36上にフォトレジスト膜42を形成する工程と、フォトレジスト膜42に開口部44を形成する工程と、開口部44が形成されたフォトレジスト膜42をマスクとして絶縁膜36をエッチングすることによりコンタクトホール48を形成する工程とを有し、コンタクトホール48を形成する工程は、開口部44が形成されたフォトレジスト膜42上に保護膜46を堆積しながら絶縁膜36をプラズマエッチングする第1の工程と、フォトレジスト膜42上に堆積された保護膜46を一旦除去する第2の工程と、保護膜46が一旦除去されたフォトレジスト膜42上に他の保護膜を新たに堆積しながら絶縁膜36を更にプラズマエッチングする第3の工程とを含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

半導体装置、及び、その製造方法

【課題】微細配線を有する半導体装置の信頼性を向上させる。

【解決手段】本発明に係る半導体装置は、第1のCu配線102と、第1のCu配線102の上に設けられ、第1のCu配線102からCuの拡散を防ぐ第1のバリア絶縁膜103とを備える。また、第1のバリア絶縁膜103の上には、第2のCu配線105と、第1のCu配線105の上に設けられ、第2のCu配線105からCuの拡散を防ぐ第2のバリア絶縁膜106と、を備える。第1、第2のバリア絶縁膜103、106は、分枝アルキル基、及び、炭素−炭素二重結合を有するシリコン系絶縁膜からなる。

(もっと読む)

半導体ウエハ装置およびその製造方法

【課題】 所望の配線構造を形成することができ、かつウエハ有効領域の欠陥率の増加を防止することのできる半導体ウエハ装置の製造方法を提供する。

【解決手段】 半導体ウエハ装置の製造方法は、(a)回路領域に半導体素子を形成した半導体ウエハ上に半導体素子に接続された下層配線パターンを形成する工程と、(b)下層配線パターンを覆って半導体ウエハ上に層間絶縁膜を形成する工程と、(c)回路領域上で下層配線パターンに接続されたビア導電体とその上に配置された配線パターンとを、回路領域外の周辺領域上で配線パターンに対応する導電体パターンを、層間絶縁膜に埋め込んで形成する工程とを含む。導電体パターンは電気的に分離された状態で形成される。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

化合物半導体デバイス

【課題】高温にさらされても、Au配線表面に析出物が発生することを抑制できる半導体デバイスの製造方法を提供する。

【解決手段】化合物半導体基板1上の、Auからなる下部配線層3aと上部配線層3bの上部を覆って、Auより薄膜応力が小さく高融点を有する金属であるタンタルあるいはチタンからなる配線被覆層5と5’をスパッタにより形成する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】プラズマCVD法を用いてCu配線上に良好な拡散バリア膜を形成する技術を提供する。

【解決手段】ダマシン法を用いて形成したCu配線19上にCuの拡散を防止する窒化シリコン膜21を形成する工程は、Cu配線19が形成された基板1をプラズマCVD装置のチャンバ内に搬入し、基板1を所定の温度に加熱する工程と、チャンバ内にアンモニアを供給し、第1のRFパワーでアンモニアをプラズマ分解することによって、Cu配線19の表面を還元処理する工程と、RFパワーが印加された状態で、チャンバ内にアンモニアとモノシランとを含む原料ガスを供給し、第2のRFパワーでアンモニアとシラン系ガスとをプラズマ分解することによって、Cu配線19上に窒化シリコン膜21を形成する工程とを含んでいる。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

半導体装置の製造方法

【課題】異方性エッチングを利用して、1つの銅膜に配線パターンとビアパターンとを同時に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】バリア膜100上に、銅膜101を形成する工程と、銅膜101上に、第1のマスク材を形成する工程と、第1のマスク材をマスクに用いて、銅膜101をバリア膜100が露出するまで異方的にエッチングする工程と、第1のマスク材を除去した後、異方的にエッチングされた銅膜101上に、第2のマスク材を形成する工程と、第2のマスク材をマスクに用いて、銅膜101をその途中まで異方的にエッチングする工程と、前記第2のマスク材を除去した後、異方的にエッチングされた銅膜101上に、絶縁物を堆積させ、異方的にエッチングされた銅膜101周囲に、層間絶縁膜106を形成する工程と、を具備する。

(もっと読む)

81 - 100 / 904

[ Back to top ]