Fターム[5F033KK25]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | シリサイド (1,324)

Fターム[5F033KK25]の下位に属するFターム

高融点金属のシリサイド (608)

Fターム[5F033KK25]に分類される特許

101 - 120 / 716

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

半導体装置及びその製造方法

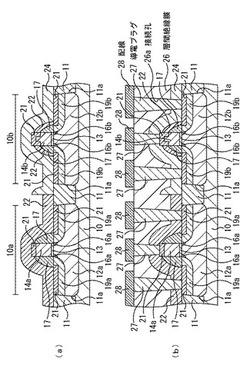

【課題】N型トランジスタ及びP型トランジスタの双方で可及的に製造工程を共通にして、工程数の可及的な削減を図るも、N型トランジスタ及びP型トランジスタの夫々に適合した応力を適宜印加し、トランジスタ性能の大幅な向上を実現する。

【解決手段】N型トランジスタでは、ゲート電極14a及びサイドウォール絶縁膜17を覆うようにN型領域10aの全面に引張応力膜22を形成し、P型トランジスタでは、サイドウォール17絶縁膜上のみに引張応力膜22を形成し、更にゲート電極14b及び引張応力膜22を覆うようにP型領域10bの全面に圧縮応力膜24を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20と、シリコン基板20の上方に形成された層間絶縁膜38と、層間絶縁膜38の上に互いに間隔をおいて複数形成されたヒューズ41a、41bと、層間絶縁膜38の上であって、隣接するヒューズ41a、41bの間に形成されたダミーパターン41xと、ヒューズ41a、41bのうちの少なくとも一部とダミーパターン41xとを覆うと共に、下から順に塗布型絶縁膜46と窒化シリコン膜47とを備えたパシベーション膜48と有する半導体装置による。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置の製造方法

【課題】貫通孔となるべきアスペクト比が20以上の深孔を埋め込む貫通電極金属としては、埋め込み特性が良好なタングステンが使用されることが多いが、通常のドライエッチングによる深孔は、ボッシュプロセスによるものに比べて寸法の大きなものとなる。この比較的大きな深孔を埋め込むためには、必然的にウエハの表面に成膜すべきタングステン膜の膜厚も厚くなり、その結果、ウエハの反りが、プロセスを正常に実行できる限界を超える程度にまで増加する。また、このような問題が許容できる限度内である場合にも、タングステン膜を堆積する際に、ウエハの周辺で下地膜の剥がれが発生する等の問題がある。

【解決手段】本願発明は、貫通ビアを形成するための非貫通孔をタングステン部材で埋め込むに当たり、ウエハの周辺部において、下地のバリアメタル膜の外延部より内側に、タングステン部材の外延部を位置させるように成膜を実行するものである。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置とその製造方法、及び半導体ウエハ

【課題】半導体装置とその製造方法、及び半導体ウエハにおいて、個片化後の半導体チップがもとの半導体ウエハのどこに位置していたかを容易に特定すること。

【解決手段】複数のチップ領域Rcとスクライブ領域Rsとを有するシリコン基板20と、複数のチップ領域Rcの各々に対応する複数のモニタ素子Mと、スクライブ領域Rsに形成され、複数のモニタ素子Mの各々を電気的に接続する配線2とを有し、スクライブ領域RsにおけるダイシングラインX1〜X7、Y1〜Y7の位置をずらしたときに、配線2の異なる部分がダイシングされるようにして、配線2と複数のモニタ素子Mとの結線状態をダイシングラインX1〜X7、Y1〜Y7の位置に応じて可変にした半導体ウエハWによる。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

101 - 120 / 716

[ Back to top ]