Fターム[5F033KK25]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | シリサイド (1,324)

Fターム[5F033KK25]の下位に属するFターム

高融点金属のシリサイド (608)

Fターム[5F033KK25]に分類される特許

141 - 160 / 716

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

AlCuプロセスのCMOSイメージセンサーの大ビアボンディングパッドのアプリケーション

【課題】AlCuプロセスのCMOSイメージセンサーの大ビアボンディングパッドのアプリケーションを提供する。

【解決手段】集積回路は、ボンディングパッド領域と非ボンディングパッド領域とを有する基板からなる。“大ビア”と称される相対して大きいビアが、ボンディング領域の基板上に形成される。大ビアは、基板向きの上面図にて、第一寸法を有する。集積回路は、非ボンディング領域の基板上に形成された複数のビアも有する。複数のビアは、それぞれ、上面図にて、第二寸法を有し、第二寸法は、第一寸法より相当小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグの上面の形状を工夫することにより、半導体装置の電気的特性において、信頼性の向上を図ることができる技術を提供する。

【解決手段】本願発明におけるプラグPLGは、上面がコンタクト層間絶縁膜CILの表面(上面)よりも突出した上に凸のドーム形状をしている。つまり、プラグPLGは、上面が上に凸のドーム形状となっており、コンタクト層間絶縁膜CILの上面の高さよりもバリア導体膜BF1の上端部の高さが高く、かつ、タングステン膜WFの上端部の高さはバリア導体膜BF1の上端部の高さよりも高くなっている。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細トランジスタのシリサイド形成工程において、ゲート間容量の増大がなく且つL字状スペーサの端部がエッチングされず接合リーク等の不良を防止できるようにする。

【解決手段】 半導体基板101上にゲート絶縁膜103を介して形成されたゲート電極104及びその側面上に形成された第1のサイドウォール108及びソースドレイン拡散層111を有する第1のトランジスタと、半導体基板上にゲート絶縁膜103を介して形成されたゲート電極104、その側面上に形成された第1のサイドウォール108、及びその外側に形成された第2のサイドウォール109を有する第2のトランジスタとを備えている。シリサイド形成領域Aにおけるゲート電極の上部及びソースドレイン拡散層の上部にはニッケルシリサイド層114が形成されており、第1のサイドウォール108は、第2のサイドウォール109をエッチングする際のエッチング材に対して耐性を有している。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】多層配線を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に第1配線用絶縁膜IM1を形成し、第1配線用絶縁膜IM1に配線溝TM1を形成する。その後、配線溝TM1に銅を主体とする導体膜を埋め込むことで配線MW1を形成する。続いて、配線MW1上にキャップ導体膜MC1を形成した後、キャップ導体膜MC1に表面研磨を施す。特に、キャップ導体膜MC1はALD法によって配線MW1上に選択的に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

半導体装置

【課題】デジタル領域とアナログ領域とが混載された半導体装置におけるデジタル領域からアナログ領域へのノイズ伝搬を効果的に抑制する。

【解決手段】デジタル領域120とアナログ領域130とが混載された半導体装置100は、平面視でデジタル領域120およびアナログ領域130の外周を取り囲む環状のシールリング140と、シールリング140で囲まれた領域内で、デジタル領域120とアナログ領域130との間に設けられ、アナログ領域130をデジタル領域120から隔離するとともに、シールリング140に電気的に接続されたガードリング150と、ガードリング150と当該ガードリング近傍で電気的に接続された電極パッド160aとを含む。電極パッド160aは、外部の接地端子(180a)に接続されて接地電位とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】実用上十分なエレクトロマイグレーション耐性及び動作速度を有する半導体装置を得られるようにする。

【解決手段】半導体基板1の上に第1の絶縁膜2を形成し、第1の絶縁膜2に配線溝3を形成し、配線溝3の内部に金属膜5を埋め込んで第1の配線6を形成し、第1の絶縁膜2及び第1の配線6の上に保護膜7を形成し、第1の配線6と保護膜7との界面に反応層8を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板と、半導体基板の第1面側に形成された半導体素子と、半導体基板の第1面側に形成されて半導体素子と電気的に接続された配線を有する配線層と、半導体基板の第1面側に形成された電極パッド部と、半導体基板の第1面からその反対側の第2面まで貫通する貫通孔内に形成された貫通電極とを備え、前記電極パッド部は、半導体基板の第1面に部分的に積層された単一導電層と、単一導電層に積層された混成導電層とを有し、前記単一導電層は、貫通電極と電気的に接続する導電領域部からなり、前記混成導電層は、単一導電層と前記配線とを電気的に接続する導電領域部と、単一導電層と配線とを電気的に絶縁する絶縁領域部とが混成されてなる半導体装置。

(もっと読む)

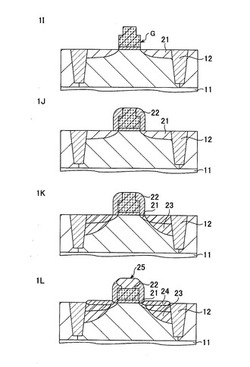

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

半導体装置

【課題】電極部と貫通電極層の間の抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供する。

【解決手段】半導体基板表面2aの第1絶縁膜8の中に、外部接続端子を有する電極部18が形成され、基板をビアホール10が貫通し、ビアホール側壁10a及び基板裏面の第2絶縁膜12とビアホール底面の第1絶縁膜とに貫通電極層11が形成され、電極部と貫通電極層との間にシリサイド層9を接続形成し、ビアホール中心軸を含む平面で切断された断面において、シリサイド層の幅A≦ビアホール底部の幅Bである。

(もっと読む)

141 - 160 / 716

[ Back to top ]