Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

561 - 580 / 2,960

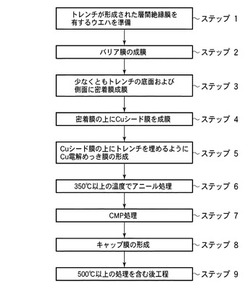

Cu配線の形成方法

【課題】配線形成後に500℃以上の高温プロセスが存在する場合に適用可能なCu配線を形成すること。

【解決手段】500℃以上の温度の処理をともなう後工程が施されるCu配線の形成方法は、表面にトレンチおよび/またはホールを有する基板上の少なくともトレンチおよび/またはホールの底面と側面に、Cuの格子面間隔との差が10%以内の格子面間隔を有する金属からなる密着膜を形成する工程と、密着膜の上に前記トレンチおよび/またはホールを埋めるようにCu膜を形成する工程と、 Cu膜形成後の基板に350℃以上のアニール処理を行う工程と、Cu膜を研磨してCu膜のトレンチおよび/またはホールに対応する部分のみを残存させる工程と、研磨後のCu膜にキャップを形成してCu配線とする工程とを有する。

(もっと読む)

電子モジュールの製造方法、および、電子モジュール

半導体基板に集積された回路と、基板と、ヒートシンクとしての支持体と、基板および支持体をはんだ付けにより接続する熱伝導性接続部とを備えた電子モジュールを提案する。ここでは、基板で用いられる後面金属化部として、まず第1の厚いAu層(23)、ついでバリア層(24)、最後に第2の薄いAu層(25)が堆積される。バリア層の材料は、はんだ付け過程において、第2のAu層の領域のAuSn液相のSnないしAuSnが第1のAu層(23)へ浸入することを阻止するように選定される。また、基板の貫通孔にも、後面金属化部の積層体が堆積される。ここで、第2のAu層の表面は、バリア層から拡散する材料によって、はんだ付け材料に対する低減された濡れ性を有する。  (もっと読む)

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

Cu系配線材料前駆体、Cu系配線材料およびこれらの形成方法

【課題】Cu-Ti系スパッタ膜を従来よりも低い温度で熱処理しても、配線表面にTi系自己拡散バリア膜を形成できるようにする。

【解決手段】極薄のTi系膜を第一の膜2として基材1上に形成した後、Ti系材料のTi系材料とCu系材料との傾斜構造を持つ複合膜を第二の膜3として形成し、その上にCu系電極となる第三の膜4を形成することにより、3層構造の前駆体を形成する。この前駆体を450℃以下で熱処理することで、Ti系バリア膜を有するCu系電極を形成することが可能となる。

(もっと読む)

ハイブリッド誘電体を備えた高信頼低誘電率相互接続構造

【課題】ハイブリッド誘電体を有する拡張型バック・エンド・オブ・ライン(BEOL)相互接続構造を提供すること。

【解決手段】ビア・レベルでの層間誘電体(ILD)は、ライン・レベルでのILDとは異なることが好ましい。好ましい実施形態では、ビア・レベルのILDを低k SiCOH材料で形成し、ライン・レベルのILDを低kポリマー熱硬化性材料で形成する。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスク膜による焦点深度のマージンの低下及びアライメントマークの視認性の低下を防ぎ、且つ、セルフアラインドビアの形成を可能とすることにより、配線同士のショートによる歩留まりの低下を防止すると共に、配線同士の絶縁性を高め、その信頼性を向上させるようにする。

【解決手段】半導体装置の製造方法は、基板10の上に、少なくとも1層の絶縁膜を含む層間絶縁膜12を形成し、層間絶縁膜12の上部に第1のマスク膜16を埋め込むように形成し、層間絶縁膜12及び第1のマスク膜16の上に第2のマスク膜17を形成し、第2のマスク膜17を用いて、層間絶縁膜12にビアホール19を形成し、第1のマスク膜16を用いて、層間絶縁膜12に配線溝20を形成し、ビアホール19及び配線溝20に導電性材料を埋め込むことにより、ビア及び配線を形成する。

(もっと読む)

電子デバイス

【課題】製造工程数や面積の増大を招くことなく、金属薄膜抵抗の抵抗率を異ならせる素子構造を提案する。

【解決手段】基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜5が配置されている。また、抵抗膜5の厚さ方向の少なくとも一方の他の導電膜配置階層に、水素吸蔵金属3が、抵抗膜5と絶縁された状態で、かつ金属抵抗膜の少なくともコンタクトエッジ間の領域の全域と平面視で重なる位置と大きさで配置されている。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

半導体基板表面を活性化するための溶液及びプロセス

【課題】半導体基板表面を活性化するための溶液及びプロセスの提供。

【解決手段】本発明は、その後の工程で無電解法により金属層を堆積させて被覆できるように、ポリマーから形成される少なくとも1つの領域を含む基板表面を活性化するための溶液及びプロセスに関する。また、本発明によれば、この組成物は、A)1以上のパラジウム錯体から形成される活性化剤と;B)少なくとも2つのグリシジル官能基及び少なくとも2つのイソシアネート官能基を含む各化合物から選択される1以上の有機化合物から形成される結合剤と;C)上記活性化剤及び上記結合剤を溶解可能な1以上の溶媒から形成される溶媒系とを含有する。用途:特に集積回路、とりわけ3次元集積回路、などの電子デバイスの製造。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、基板裏面側のプラズマ処理により、基板表面側の電極が変色し、SiN膜がプラズマ処理されてしまう問題があった。

【解決手段】本発明の半導体装置では、シリコン基板2の裏面側に裏面電極13を配置し、その裏面電極13を構成するAl層14は、シリコン基板2上に直接配置される。そして、Al層14は、シリコン基板2とAlスパイクを形成することで、シリコン基板2と裏面電極13との接着性が向上される。この構造により、シリコン基板2へのプラズマ処理が不要となり、シリコン基板2の表面側のパッド電極12が変色し、ジャケット膜10がプラズマ処理されることを防止できる。

(もっと読む)

埋め込み配線を有する半導体装置及び埋め込み配線の製造方法

【課題】ディッシングを抑制できる太幅の埋め込み配線を有する半導体装置、及びディッシングを抑制できる太幅の埋め込み配線の簡易な製造方法を提供する。

【解決手段】金属製埋め込み配線を有する半導体装置であって、該埋め込み配線の表面の長さ方向に、所定値以下の間隔で、該金属よりも硬度の高い金属材料からなるバリア線6が配設されていることを特徴とする半導体装置及びその埋め込み配線の製造方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】異なる基板に形成された電極同士を接合する場合、合わせずれが発生しても、電極抵抗の上昇や電流リーク等の発生を、層間容量を大きくせず防止する。

【解決手段】第1基板11上の第1層間絶縁膜12に形成された第1溝13内に第1金属電極15が埋め込まれた第1基板11と、第2基板上の第2層間絶縁膜に形成された第2溝内に第2金属電極が埋め込まれた第2基板を用意し、第1層間絶縁膜12、第2層間絶縁膜、側のそれぞれに第1拡散防止層16、第2拡散防止層、を形成する工程と、第1金属電極15、第2金属電極、を対向して接合する際に、第1金属電極15、第2金属電極、のそれぞれの形成領域内の第1拡散防止層16、第2拡散防止層、のそれぞれに第1開口部17、第2開口部、を形成する工程と、第1開口部17、第2開口部、を対向させて熱処理を行い、第1金属電極15、第2金属電極、を熱膨張によって接合させる工程を有する。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセスの工程数を少なくし得ると同時に低い接続抵抗を実現し得る構造を持つ半導体装置の製造方法を提供する。

【解決手段】この製造方法は、セルトランジスタの拡散領域206A,206C,206D,206Fに達する第1のコンタクトホールと、セルトランジスタの拡散領域206B,206Eに達するビット線コンタクトホールと、このビット線コンタクトホールに連通する配線溝とを第1の絶縁膜208Pに埋め込み形成する。また、これら第1のコンタクトホール、ビット線コンタクトホールおよび配線溝に導電性材料を埋め込むことでそれぞれ第1のコンタクトプラグ210A〜210Dとビット線コンタクト211B,211Fとを形成し、第1のコンタクトプラグ210A〜210Dを、第2の絶縁膜212に形成された開口部を介して、第3の絶縁膜214Pに形成されたキャパシタと電気的に接続する。

(もっと読む)

561 - 580 / 2,960

[ Back to top ]