Fターム[5F033NN37]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | 配線層が3層以上に跨がるコンタクトホール (478)

Fターム[5F033NN37]の下位に属するFターム

中継パッドの利用 (80)

3層以上を同時接続 (82)

中間層を電気的に絶縁 (227)

Fターム[5F033NN37]に分類される特許

21 - 40 / 89

半導体装置

【課題】小型化が可能な半導体装置を提供する。

【解決手段】半導体装置において、第1の導電性材料からなる第1のコンタクトと、第2の導電性材料からなり、下端部が第1のコンタクトの上端部に接続された第2のコンタクトと、第3の導電性材料からなり、下面が第1のコンタクトの下面よりも上方に位置し、上面が第2のコンタクトの上面よりも下方に位置し、第1及び第2のコンタクトから離隔した中間配線と、を設ける。そして、第2の導電性材料に対する第1の導電性材料の拡散係数は、第2の導電性材料に対する第3の導電性材料の拡散係数よりも小さい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

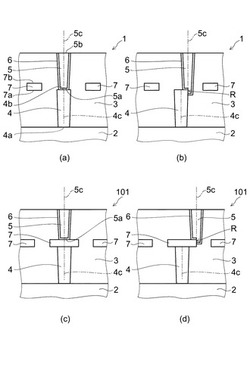

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、配線層の平坦性を保つためのダミーパターンを有する半導体装置とその製造方法を提供することを目的とする。

【解決手段】半導体装置の機能を実現するうえで必要な機能パターンと、半導体装置の所定の層に、前記機能パターンと共に複数のダミーパターンとを備え、第一の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンが配置されない領域に、第二の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンと前記機能パターンとの間に前記第二の大きさの複数のダミーパターンが配置され、第一所定方向に配置された前記第一の大きさの複数のダミーパターンと、第二所定方向に配置された前記第二の大きさの複数のダミーパターンとは隣り合い、前記第一の大きさのダミーパターン間の幅は、前記第二の大きさのダミーパターン間の幅よりも大きい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】上層の配線が導電体や不純物拡散層からずれていても、上層の配線を導電体や不純物拡散層に接続することができるようにする。

【解決手段】第1プラグ210は第1絶縁層200に埋め込まれており、不純物拡散層110に接続している。第2プラグ310は第2絶縁層300に埋め込まれており、第1プラグ210に接続している。第3プラグ410は第3絶縁層400に埋め込まれており、第2プラグ310に接続している。第1配線510は第3絶縁層400の表面に位置しており、第3プラグ410に接続している。平面視において、第2プラグ310は、上面及び底面の幅が第1プラグ210及び第3プラグ410の上面及び底面の幅がより大きく、かつ中心が、第1プラグ210の中心及び第3プラグ410の中心の少なくとも一方からずれている。そして第1プラグ210の中心は第3プラグ410の中心からずれている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置の製造方法

【課題】スタックされるプラグ同士の接続を良好に行う。

【解決手段】半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜に第1のホールを形成し、第1のホール内にバリア膜を形成し、第1のホール内に導電材を充填して第1のプラグを形成し、第1の層間絶縁膜上に第2の層間絶縁膜を形成し、第2の層間絶縁膜に第1のプラグに達する第2のホールを形成し、第2のホール内で前記バリア膜上端部を選択エッチングし、第2のホール内に、第1のプラグに接続する第2のプラグを形成する、半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】写真製版プロセスのマージンを大幅に拡大でき、かつマイクロローディング効果を低減することによって「開口不良」を抑制できるとともに「ショート」のプロセス裕度を確保しやすくし、かつコンタクト抵抗を低減できる半導体装置の製造方法を提供する。

【解決手段】活性領域に対して傾斜して延びるようにゲート電極層50と窒素を含む絶縁膜2とが積層される。シリコン酸化膜5が形成される。活性領域の幅より大きくかつ互いに隣り合う活性領域のピッチより小さい帯状の開口パターンが絶縁膜2に形成され、開口パターンから1対の不純物拡散領域の各々が露出させられる。開口パターンが導電層23で埋め込まれる。導電層23から1対の不純物拡散領域の各々に電気的に接続されたプラグ導電層23a、23bが形成されるとともに、プラグ導電層23a、23bの各上面と絶縁膜2の上面とが同一平面とされる。

(もっと読む)

磁気トンネル接合デバイスおよび製作

磁気トンネル接合(MTJ)デバイスおよび製作方法が、開示される。特定の実施形態では、底部キャップ層および垂直軸を有する底部金属充填トレンチを含む構造体上に磁気トンネル接合(MTJ)デバイスを形成するステップを含む方法が、開示され、磁気トンネル接合デバイスは、底部電極、磁気トンネル接合層、磁気トンネル接合シール層、上部電極、およびロジックキャップ層を含み、磁気トンネル接合デバイスは、垂直軸からオフセットしているMTJ軸を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は多層配線構造を有する半導体装置の製造方法に関し、高い集積度が要求される場合に優れた歩留まりと高い信頼性とを確保することを目的とする。

【解決手段】トランジスタのソースドレイン領域の上層にシリコン酸化膜7を形成する。一端面がソースドレイン領域6に導通し、他端面がシリコン酸化膜7の表面に露出するように、シリコン酸化膜7の内部に導電性のパッド10を設ける。シリコン酸化膜7およびパッド10の上層にシリコン酸化膜11を形成する。一端面がパッド10に接触し、他端面が配線層14と導通するようにシリコン酸化膜11の内部にプラグとして機能する導電層を設ける。シリコン酸化膜7の表面と、パッド10の他端面は平滑な同一平面を形成する。プラグとして機能する導電層は、パッド10に比して小さく、かつ、パッド10の中央部近傍に接触するように形成する。

(もっと読む)

半導体装置

【課題】小型化及び利得等の高周波性能の向上を図ることができる半導体装置として、実用的な高周波増幅器を実現する。

【解決手段】トランジスタ101の入力端に配線層103がコプレーナ線路で接続されており、配線層103には、開放端を有する配線層104が二つの方向に分岐されて終端され、配線層103上の位置から、高周波信号が入出力される。

(もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

半導体装置の製造方法及び電気泳動表示装置の製造方法

【課題】半導体装置を構成する膜質によらず製造可能であり、製造過程に要する時間を短縮させることが可能な半導体装置の製造方法及び電気泳動表示装置の製造方法を提供すること。

【解決手段】プラズマ曝露によって第1レジスト層を除去し、剥離によって第2レジスト層及び第3レジスト層をそれぞれ除去することとしたので、エッチング工程を要することなく第1導電層及び第2導電層を形成することができる。これにより、第1絶縁層及び第2絶縁層の膜質によらず製造可能となる。加えて、エッチングを行う際に必要な耐性評価を行わずに済むため、製造過程に要する時間を短縮させることができる。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

フォトセンサ及び表示装置

【課題】マトリクス状に配置した光電変換素子が捉える光の強度分布を、再現よく電気信号に変換して取り出せる大型のエリアセンサおよび、エリアセンサを搭載した書き込み速度が速く、表示ムラが少ない表示装置を提供する。

【解決手段】インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタは、大面積基板にマトリクス状に配置することが容易であり、また特性にバラツキが少ない。インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタで構成した特性にバラツキが少ない増幅回路と表示素子の駆動回路を用いて、マトリクス状に配置したフォトダイオードが捉える光の強度分布を再現よく電気信号に変換して取り出し、マトリクス状に配置した表示素子をムラなく駆動する。

(もっと読む)

半導体装置とその製造方法

【課題】キャパシタを備えた半導体装置とその製造方法において、キャパシタの品質を向上させること。

【解決手段】第1の導電膜19、誘電体膜20、及び第2の導電膜21をこの順に形成する工程と、第2の導電膜21をパターニングして、複数の上部電極21aを形成する工程と、レジストパターン27の側面27bが後退するエッチング条件を用いて、該レジストパターン27をマスクにしながら誘電体膜20をエッチングし、キャパシタ誘電体膜20aを形成する工程と、第1の導電膜19をパターニングして下部電極19aを形成する工程と、上部電極19aの上の層間絶縁膜33にホール33aを形成する工程と、ホール33aに導体プラグ37を埋め込む工程とを有し、端部の上部電極21a上のホール37の形成予定領域が、側面27bが後退した後のレジストパターン27により覆われる半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

21 - 40 / 89

[ Back to top ]