Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

401 - 420 / 898

半導体装置および半導体装置の製造方法

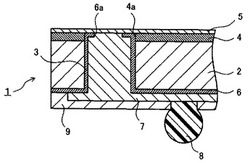

【課題】半導体基板の貫通配線部において、貫通孔底部での絶縁層の被覆性が向上され、電気的絶縁性の低下や接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が開口4aを覆い形成されている。また、貫通孔3内および半導体基板2の裏面に第2の絶縁層6が被覆されている。第2の絶縁層6は、第1の配線層5と内接するように形成され、内接部に第1の絶縁層4の開口4aよりも小径の開口6aを有している。さらに、貫通孔3内に第2の配線層7が充填・形成され、この第2の配線層7は第2の絶縁層6の開口6aを介して第1の配線層5に内接している。

(もっと読む)

半導体デバイスのエッチング量判定方法

【課題】時間を費やさない簡便な手順でエッチング量を正確に確定することのできる半導体デバイスのエッチング量判定方法を提供する。

【解決手段】エッチング量判定方法は基板上にステップ状の複数の区域を有するモニター部を備えた擬似電極を形成する。次いで、試料の電極と同時にモニター部の第1区域および第2区域をエッチングし、このとき現われる基板の露出面積に基づいてエッチング量を確定する(1次判定)。次いで、電極と同時にモニター部の第2区域をエッチングし、このとき現われる基板の露出面積に基づいてエッチング量を確定する(最終判定)。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、界面活性剤を含んだ洗浄液による洗浄後の低誘電率膜のk値の変動を回復する。

【解決手段】 基板上にk値が3.0以下の低誘電率膜1を成膜したのち、低誘電率膜1に凹部を形成し、次いで、凹部及び低誘電率膜1上に導電体膜を堆積したのち、低誘電率膜1が露出するまで導電体膜を研磨し、次いで、低誘電率膜1の表面を界面活性剤3を含む洗浄剤で洗浄したのち、低誘電率膜1の表面に残存する界面活性剤3を、界面活性剤3が表面に残存した状態における低誘電率膜1の比誘電率の増大分を60%以下に低減できる界面活性剤除去方法で除去する。

(もっと読む)

水蒸気及び希釈ガスにより改善された水素アッシング

【課題】水素化シリコンオキシカーバイド材料に基づく低−k誘電体材料に特に有用な酸素フリーの水素プラズマアッシングプロセスを提供する。

【解決手段】メインアッシング工程は、水素(50)及び任意の窒素(54)、大量の水蒸気(60)、更に大量のアルゴン(80)又はヘリウムのプラズマ(48)に、予めエッチングしておいた誘電体層を露出することを含む。ポーラス低−k誘電体については特に、メインアッシングプラズマは、更に、メタン等の炭化水素ガス(84)を含有する。メインアッシングは、水素及び任意の窒素等の水素含有還元ガスのプラズマにより、短い表面処理を施しておいてもよい。

(もっと読む)

半導体装置及び半導体装置内に空洞を形成する方法(核化防止層を使用する選択的なピンチ・オフを有する空隙)

【課題】配線用の導電体相互間のクロストークを減少した半導体装置を提供する。

【解決手段】半導体装置内に空洞を形成する方法が開示される。本発明の方法は、半導体装置のILD層内の空洞の内面上に核化防止層を付着することを含む。この核化防止層は、後に付着される誘電体層が空洞内に付着することを防止する。誘電体層が空洞内に付着することを防止することにより、キャパシタンスが減少され、これにより、改善された半導体動作特性を実現する。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】工程数を増やすことなく、安価に微細パターンを形成する方法を提供する。

【解決手段】半導体基板上にエッチング対象膜102、ハードマスク膜104及び第1の補助パターンを形成し、第1の補助パターンにシリレーション工程を行う。シリレーションされた第1の補助パターン106aを含む上記ハードマスク膜上に絶縁膜108を形成し、上記シリレーションされた第1の補助パターンの間の絶縁膜108上に第2の補助パターンを形成する。上記絶縁膜が上記第2の補助パターンの下部にのみ残留するようにエッチング工程を行い、上記シリレーションされた第1の補助パターン及び第2の補助パターンをエッチングマスクとして用いるエッチング工程で上記ハードマスク膜をエッチングしてハードマスクパターンを形成する。ハードマスクパターンを用いて上記エッチング対象膜をエッチングする。

(もっと読む)

半導体装置

【課題】フローティングしている下層金属配線に通じるホール形成のためのプラズマエッチング工程において、高抵抗などのビア不良の発生を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】上層配線201とビア301で接続されている下層配線101上にダミービア1を形成し、上層配線201とビア302で接続されている下層配線102上にダミービア2を形成する。これらダミービアの上面が露出しないように上層配線のダミー配線1A、2Aによりビアの上面を覆う。これらダミービアによりプラズマエッチングを行う時に下層配線に蓄積される電荷の影響を分散させる。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁層の剥離を抑制し、製品の歩留まりが向上するとともに製品信頼性が向上した半導体装置を得ることができる製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に形成された第1配線膜15と、反射防止膜17および第1レジスト膜18からなる積層体から、第1レジスト膜18を除去する工程と、前記工程において反射防止膜17表層に形成された変質膜22を除去する工程と、前記工程後に第1配線膜15に電気的に接続するビアプラグと、前記ビアプラグに電気的に接続する第2配線膜とを形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】エアブリッジ配線の機械的強度を向上させた高周波半導体装置を提供する。

【解決手段】半導体基板11上に形成された第1の配線層12と、この第1の配線層12の両側において、この第1の配線層12と交差する方向に配置される第2、第3の配線層13−1、13−2と、これらの第2、第3の配線層13−1、13−2間を、前記第1の配線層12上の空気層を介して相互に接続するエアブリッジ配線層14とを備え、このエアブリッジ配線層14の全体形状は上に凸のアーチ型をなしており、且つ、エアブリッジ配線14の横断面形状は下に凸状に湾曲している半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、樹脂層を平坦化して多層配線を形成することを目的とする。

【解決手段】 集積回路12及び集積回路12に電気的に接続された電極14を有する半導体基板10に形成された絶縁膜16にスペーサ18を形成する。電極14に電気的に接続するように、絶縁膜16上からスペーサ18上に配線を形成する。絶縁膜16及びスペーサ18の段差に対応して上面が凹凸になるように、配線を覆う第1の樹脂層22を形成する。第1の樹脂層22の凹凸を埋めて、上面が平坦な第2の樹脂層24を形成する。エッチングを、第2の樹脂層24の上面に対して開始し、第2の樹脂層24から第1の樹脂層22の凸部が露出し、配線のスペーサ18上の部分が第1の樹脂層22から露出するまで行う。

(もっと読む)

三次元半導体デバイスの製造方法、基板生産物の製造方法、基板生産物、及び三次元半導体デバイス

【課題】金属からなる層間配線を容易に形成できる三次元半導体デバイスの製造方法、基板生産物の製造方法、基板生産物、及び三次元半導体デバイスを提供する。

【解決手段】この製造方法は、シリコン基板80の表面80aに有底の穴82を形成する穴形成工程と、犠牲材料85により穴82を埋め込む埋込工程と、集積回路層90をシリコン基板80の表面80aに形成する集積回路形成工程と、シリコン基板80の裏面80bよりシリコン基板80を薄化することにより、穴82を貫通させると共にシリコン基板80の裏面80bから犠牲材料85の一部を露出させる薄化工程と、犠牲材料85を除去して金属材料を埋め込むことにより層間配線を形成する配線形成工程と、シリコン基板80を他の基板上に積み重ね、集積回路層90の回路と他の基板上の回路とを層間配線を介して電気的に接続する積層工程とを備える。

(もっと読む)

エッチング方法、エッチングシステムおよびエッチング装置

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFを含むガスによるドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

ナノワイヤトランジスタおよびその製造方法

【課題】ナノワイヤトランジスタ(NWT)の製造において、凹状ストリンガを除去する方法を提供する。

【解決手段】

本方法は、軸の外部表面が基板表面に接している円筒状のナノ構造体を準備する。ナノ構造体は、絶縁性半導体コアを含んでいる。導電性薄膜が、ナノ構造体上に堆積され、ゲートストラップ、またはゲートとゲートストラップとの組み合わせとして機能する。ハードマスク絶縁体が、導電性薄膜上に堆積され、ハードマスクの選択領域が異方性プラズマエッチングされる。結果として、ナノ構造体の円筒状部分を実質的に囲む導電性薄膜ゲート電極が形成される。

(もっと読む)

半導体デバイス構造

【課題】 スタティック・ランダム・アクセス・メモリ(SRAM)デバイスで使用するための半導体デバイス構造およびこのような半導体デバイス構造を形成するための方法を提供することにある。

【解決手段】 この半導体デバイス構造は、第1の半導体領域と第2の半導体領域との間に配置された誘電体領域と、第1の半導体領域と第2の半導体領域との間に伸びるゲート導体構造とを含む。ゲート導体構造は、第1の半導体領域の上に重なる第1の側壁を有する。このデバイス構造は、第1の半導体領域の全域に伸びる電気的接続ブリッジをさらに含む。電気的接続ブリッジは、第1の半導体領域内の不純物ドープ領域をゲート導体構造の第1の側壁に電気的に接続する一部分を有する。

(もっと読む)

電子デバイス及びその製造方法

【課題】カーボンナノチューブを用いた配線構造を備える電子デバイスの製造方法について、炭素元素円筒型構造体からなるビアを歩留まり良く形成すること。

【解決手段】基板1上の第1絶縁膜2上に導電パターン5を形成する工程と、第1絶縁膜2と導電パターン5を覆う第2絶縁膜7を形成する工程と、第2絶縁膜7のうち導電パターン5の上にホール7aを形成する工程と、少なくともホール7a内の底面と第2絶縁膜7の上面に金属膜9を形成する工程と、金属膜9の表面に触媒粒子又は触媒膜からなる触媒面10を形成する工程と、触媒面10から炭素元素円筒型構造体11の束を成長する工程と、炭素元素円筒型構造体の束10の間隙に埋込膜12を形成する工程と、炭素元素円筒型構造体の束11及び埋込膜12及び金属膜9を研磨して第2絶縁膜7の上面から除去するとともに、埋込膜12及び炭素元素円筒型構造体の束11をホール7a内に残してビア13を形成する工程とを含む。

(もっと読む)

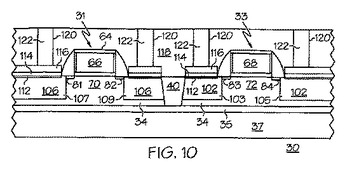

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】金属層の損傷を抑制した半導体装置の製造方法を提供すること。

【解決手段】Cu配線2上に酸化膜3を堆積する工程と、前記酸化膜3をドライエッチングして、前記Cu配線2に通達するビアホールHを形成する工程と、前記ビアホールH内にDIWを供給する工程と、前記DIWを供給した後に、前記ビアホールH内に燐酸アンモニウムを供給する工程と、前記燐酸アンモニウムを供給した後に、前記ビアホールH内に導電材料5を埋め込む工程とを含む。

(もっと読む)

半導体装置

【課題】金属抵抗素子の形成位置を画定するための写真製版技術における露光時にレジスト膜中に定在波が発生するのを防止して金属抵抗素子の寸法バラツキを低減する。

【解決手段】金属抵抗素子27の下地絶縁膜23は、金属抵抗素子27の長手方向において、金属抵抗素子27の接続孔25,25間における上面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27はその長手方向において下地絶縁膜23の曲面に起因して、コンタクト、コンタクト間における上面及び下面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27の形成位置を画定するための写真製版技術における露光時に、金属抵抗素子27を形成するための金属膜の上面及び下面で露光光の反射光は上記曲面により散乱されるので、反射光と入射光によるレジスト膜中での定在波の発生が防止される。

(もっと読む)

ダメージの入った多孔性誘電体の処理方法

【課題】処理工程で変化した多孔質誘電体層の初期特性を回復させ保持する方法を提供する。

【解決手段】処理された多孔質誘電層であって少なくとも部分的に露出した多孔質誘電層10を上部に有する基板を提供する工程と、処理された多孔質誘電層10の少なくとも露出した部分に薄い水性膜を形成する工程と、表面に水性膜を有する露出した多孔質誘電体膜10を、少なくとも1のシリル化剤と濃縮CO2を含む混合物を含む雰囲気に接触させる工程とを含み、これにより多孔質誘電体10の初期特性を回復させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、ゲート電極のトリミングを良好に実施できるように、また、レジストトリミングを行ってもレジスト倒れやレジスト変形が発生しないように、更に、従来のトリミングがプラズマエッチングで実施されていることに起因する問題を解消し、更にまた、ゲート電極のトリミングに関連してサイドウォールの形成時にSTI部が過剰に損傷されないようにしようとする。

【解決手段】金属を含む材料である金属シリサイド或いは金属単体から成るゲート電極をもつ半導体装置を作製する工程に於いて、ゲート電極14Gのエッチング後にゲート部の表面を酸化させ、ゲート部を有機酸を含むガス状物質に曝露すると共に加熱して金属と有機酸との反応生成物を揮発させてゲート電極14Gのトリミングを行う。

(もっと読む)

401 - 420 / 898

[ Back to top ]