Fターム[5F033QQ19]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ウェットエッチング (1,982)

Fターム[5F033QQ19]の下位に属するFターム

エッチング液 (265)

Fターム[5F033QQ19]に分類される特許

21 - 40 / 1,717

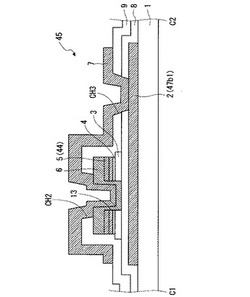

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】第2の金属膜を形成するためのめっき液が電極と反応することを抑制することができる半導体装置と、その製造方法を提供する。

【解決手段】半導体基板12の表面の一部に形成されている表面電極14の外周縁部の表面を被覆する保護膜16を形成する。保護膜16の内周端面30に複数個の凹部32を形成する。表面電極14のうち保護膜16で被覆されていない部分の表面に第1の金属膜18を形成する。第1の金属膜18は、その一部が凹部32の間に入り込んで形成される。次いで、第1の金属膜18の表面に、第1の金属膜18と異なる金属で第2の金属膜20を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性のBSV方式のTSVを実現する。

【解決手段】実施形態に係わる半導体装置は、表面及び裏面を有し、表面側にLSIが形成される半導体基板11と、表面側において半導体基板11内に形成され、開口部を有する絶縁層12と、表面側において開口部上に形成され、LSIに接続される導電層13と、裏面側から開口部を介して導電層13に接続されるビア17とを備える。ビア17のサイズは、裏面から半導体基板11と絶縁層12の界面までの範囲内において開口部のサイズよりも大きく、開口部内において開口部のサイズに等しい。

(もっと読む)

配線構造及びその製造方法

【課題】配線間の絶縁性に優れ信頼性の高い配線構造及びその製造方法を提供する。

【解決手段】スピンコート法により、ベースポリマーがポリイミド樹脂である非感光性樹脂のワニスを塗布後、ベーク、キュアしてポリイミド樹脂を硬化、膜を形成する。これを第1絶縁膜12とする。次いで、めっきシード層18形成、フォトレジスト溝パターン22形成、めっき、フォトレジスト溝パターン22除去、配線下以外のめっきシード層18除去に依り、第1の絶縁膜上に配線26を形成する。そして、第1絶縁膜の表面上にシリカ粒子30を分散し、散したシリカ粒子30をマスクとして、CF4及びO2を混合したガスで、第1絶縁膜12をドライエッチングすることに依り、段差が100nm以上の凹凸32を形成する。最後に前述と同様にして、スピンコート法により、第2絶縁膜としてのポリイミド樹脂膜34を形成する。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

配線構造およびその製造方法

【課題】複雑な配線構造であっても、電極パターン同士を簡単な構造で接続できると共に、配線パターンの強度をも確保できるような配線構造、およびこうした配線構造を製造するための有用な方法を提供する。

【解決手段】本発明の配線構造は、基板上に形成された少なくとも第1の配線パターンと第2の配線パターンを有する配線構造であって、前記第1の配線パターンと第2の配線パターンとの間は、金属ワイヤーによる空中配線部によって接続されると共に、少なくとも金属ワイヤー表面には、金属ワイヤーと同じ若しくは異なる素材からなる金属めっきが施されたものである。

(もっと読む)

表示装置およびその製造方法、並びに電子機器

【課題】互いに電気的に接続された薄膜トランジスタの第2電極と配線層との間の電食の発生を防止して、安定した電気特性を得ることできる表示装置およびその製造方法、並びに電子機器を提供する。

【解決手段】薄膜トランジスタおよび配線層を備え、前記薄膜トランジスタは、制御電極

と、前記制御電極と対向する半導体層と、前記半導体層に電気的に接続され、光透過性材

料からなる第1電極と、前記光透過性材料よりも低抵抗の金属膜を含むと共に、前記半導

体層および前記配線層にそれぞれ電気的に接続された第2電極とを備え、前記金属膜の構

成材料と前記配線層の少なくとも一部を構成する導電材料とのイオン化傾向の差は、前記

光透過性材料と前記導電材料とのイオン化傾向の差よりも小さい表示装置。

(もっと読む)

液晶表示装置の製造方法及びレジスト剥離装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】エッチングによってAl合金層11、キャップ層12で形成される走査線10をパターニングした後、レジスト200をMEA(モノエタノールアミン)によって剥離する。MEAを剥離したあと、第1水洗槽において、基板に付着しているMEAを水によって洗浄する。この時、洗浄液である水に所定の量以上のMEAが含まれていると、Al合金が溶解し、キャップ層12であるMoCrの庇が発生する。これを防止するために、第1水洗槽における洗浄液のMEAの濃度を10PPM以下、好ましくは5PPM以下に管理する。これによって、Al合金の溶解を防止し、キャップ層12の庇が発生することを防止する。

(もっと読む)

半導体装置の製造方法

【課題】配線幅が異なる第1及び第2の配線を有する配線パターンの上に形成された絶縁層を、十分に平坦化すること。

【解決手段】基板上に、第1の配線及び第1の配線よりも配線幅が小さい第2の配線を有する配線パターンを形成する配線形成工程S10と、配線パターンの上から、第1の絶縁層及び第2の絶縁層をこの順に形成する絶縁層形成工程S20と、第2の絶縁層の上に、配線パターンの反転パターンを有するレジストパターンを形成するレジスト形成工程S30と、第2の絶縁層の方が第1の絶縁層よりもエッチングされやすい条件で等方性エッチングするエッチング工程S40と、レジストパターンを除去するレジスト除去工程S50と、を有する半導体装置の製造方法。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

21 - 40 / 1,717

[ Back to top ]