Fターム[5F033QQ27]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 導電膜 (467)

Fターム[5F033QQ27]に分類される特許

81 - 100 / 467

半導体装置の製造方法

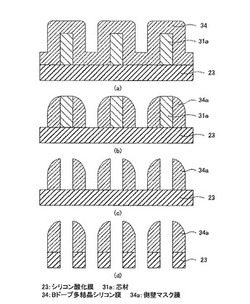

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板上にポリイミドなどからなる保護膜が形成された半導体装置の製造中に、保護膜の上面層が変質しても、この変質による悪影響が生じないようにする。

【解決手段】 ポリイミドなどからなる保護膜5に開口部6を形成したとき、保護膜5の開口部6を介して露出された接続パッド2の上面にポリイミドなどからなる残渣が残存する場合がある。そこで、次に、この残渣を酸素プラズマアッシングにより除去する。この場合、保護膜5の上面側に凸凹構造の変質層Aが形成される。次に、開口部4、6を介して露出された接続パッド2の上面に形成された自然酸化膜をアルゴンプラズマエッチングにより除去する。この場合、変質層Aがさらに変質して網目構造の変質層Cが形成される。次に、チタンなどからなる第1の下地金属層7を成膜する。この場合、第1の下地金属層7は網目構造の変質層Cの上面に成膜されるため、その界面の密着力は高い。

(もっと読む)

プラズマエッチング方法

【課題】従来技術ではデュアルダマシン構造Via工程のLow−K膜エッチング後の孔底部のエッチングにおいて、ストッパ膜のエッチングが進行しない課題があった。

【解決手段】本発明はプラズマエッチングするデュアルダマシンプロセスにおいて、デュアルダマシンプロセスのVia加工方法は、Viaパターニングされた上層レジスト膜をマスクとして反射防止膜をエッチングする第1ステップと、上層レジスト膜及び反射防止膜をマスクとして下層レジスト膜をエッチングする第2ステップと、下層レジスト膜をマスクとして前記Low−K膜をエッチングする第3ステップと、ストッパ膜のエッチング前にプラズマ処理を行う第4ステップと、ストッパ膜をエッチングする第5ステップとを有することである。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】窒化シリコン層3上に形成されたポリシリコン層をパターニングすることによってメモリセルアレイ領域1aにスリミングされたサイドウォールコア4を形成する。次に、サイドウォールコア4の少なくとも側面を覆う酸化シリコン層6、ポリシリコン層を順に成膜し、ポリシリコン層をエッチバックすることによって埋込ハードマスク7を形成する。その後、酸化シリコン層6をエッチングすることにより、サイドウォールコア4又は埋込ハードマスク7と重ならないメモリセルアレイ領域1a内の窒化シリコン層3と、目合わせモニタマーク8bと重なる周辺回路領域1b内の窒化シリコン層3を露出させ、被エッチング部材としての窒化シリコン層3をパターニングする。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写によるマスクパターンの倒れ、マスクパターンの接触を抑制する。

【解決手段】シリコン基板1上に、第1のTEOS酸化膜2、シリコン窒化膜3、第1のアモルファスシリコン膜4、第2のTEOS酸化膜5を積層形成する。レジストによるパターニングでTEOS酸化膜5を第1幅D1の中間パターン5aに加工し、スリミング処理をして第2幅D2の芯材パターン5bを形成する。第2のアモルファスシリコン膜6を形成してスペーサ処理をすることで側壁膜6aを形成し、芯材パターン5bを除去して孤立したマスクパターン6bを得る。下地に同じアモルファスシリコン膜4を用いるので、マスクパターン6bの倒れや接触の発生を抑制できる。

(もっと読む)

パターン形成方法およびパターン形成体

【課題】複数の段差を備えた微細な3次元構造パターンの形成に好適なパターン形成方法を提供することを目的とする。

【解決手段】本発明によれば、ハードマスク層は基板に対してエッチング選択比が高い材料であるため、形成する3次元構造パターンに対応するハードマスク層の段差は、所望する3次元構造パターンよりも、深さを小さくすることが出来る。また、ハードマスク層に段差を形成するにあたり、ハードマスク層を基板表面を覆うように残存させることにより、複数段のパターン形成において、基板の帯電(チャージアップ)を抑制することが出来る。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】ビア等となる開口内への金属の埋設において、ボイドの発生を抑制することを課題とする。

【解決手段】基板上に形成された第2のp−SiCOH膜204の直上に、ハードマスクとしてTiN膜205を形成する工程と、フォトリソグラフィーとエッチングにより、TiN膜205および第2のp−SiCOH膜204を貫く開口を形成する工程と、前記開口内を洗浄する工程と、前記洗浄工程の後、TiN膜205を除去する工程と、TiN膜205を除去後、第2のp−SiCOH膜204の直上に、前記開口を埋める第2の金属膜214を形成する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の銅配線の信頼性をTDDB寿命とEM寿命との双方に関して向上させる。

【解決手段】 半導体装置の配線層30は、配線溝が形成された絶縁膜32、35と、配線溝の内面に形成されたバリアメタル層41と、バリアメタル層41を介して配線溝内に形成された銅配線膜43とを有する。バリアメタル層41は、配線溝の内壁面側から順に形成された第1乃至第3のバリアメタル膜41−1、2、3を有する。第2のバリアメタル膜41−2は、第3のバリアメタル膜41−3側の表面部分において、クラスタイオン照射によって形成された、その他の部分より高い密度の緻密層41−2aを有する。第3のバリアメタル膜41−3は、例えばルテニウム等、銅配線膜43との密着性に優れた材料を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜内の水分などによるバリアメタルの腐食を防止し、銅配線の信頼性の低下及び抵抗値の上昇を抑制し得る半導体装置、及びその製造方法を提供する。

【解決手段】 メチル基を含有する層間絶縁膜32内に配線溝37を形成する。配線溝37が形成された絶縁膜32に紫外線又は電子線を照射した後に、メチル基を有するガスを用いて絶縁膜の露出面を疎水化する。配線溝37の疎水化された内面に沿ってバリアメタル層41を形成し、該バリアメタル層41を介して配線溝37を銅配線43で充填する。一実施形態において、配線溝37はメタルハードマスク47を用いて絶縁膜32をエッチングすることにより形成され、絶縁膜32への紫外線又は電子線の照射は、メタルハードマスク47を残存させた状態で行われる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ダマシン配線形成時に、シード膜を配線用溝の側壁に確実に形成する。

【解決手段】下地絶縁膜1の上にプラズマシリコン窒化膜2、プラズマTEOS酸化膜3を形成する。プラズマTEOS酸化膜3は、高周波電源および低周波電源を用いる2周波励起プラズマCVD装置により、膜密度が上部に行くほど小さくなるように形成される。配線用溝をRIE法により形成した後、ウェットエッチングで膜密度が小さい部分を速くエッチングすることでテーパ形状の配線用溝3aを形成する。スパッタでバリアメタル膜4を形成する際に配線用溝3aの側壁にも確実に形成でき、銅膜5のメッキをボイドなしに形成できる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の良好な半導体装置及びその製造方法を提供することにある。

【解決手段】一方の主面に於ける半導体素子領域2内に複数の機能素子が配設された半導体基板1と、半導体基板1の一方の主面上に配設され、複数の配線層3と複数の絶縁層4とを含む多層配線層2と、多層配線層2上に形成された第1の有機絶縁物層6と、第1の有機絶縁物層上に形成され、配線層に電気的に接続された他の配線層と、第1の有機絶縁物層6上に、他の配線層を覆うように形成された第2の有機絶縁物層10とを具備し、半導体素子領域を囲む半導体基板領域に、多層配線層を貫く溝が半導体素子領域を囲繞して配設されており、溝内には、前記有機絶縁物層6、有機絶縁物層10のいずれからも分離された有機絶縁物が配設されている。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置のビアホールにおける残渣物の残留を抑制することができ、かつ、半導体装置のデバイス特性不良、信頼性不良等を抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、GaN系半導体層(11)が設けられたSiC基板(10)の第1主面の反対側の第2主面上にCuあるいはCu合金からなり部分的に開口を有するエッチングマスク(50)を形成する工程と、エッチングマスク(50)を利用したドライエッチングを実施し、底部の厚さ方向にGaN系半導体層(11)が残存したビアホールを形成する第1エッチング工程と、第1エッチング工程の後にエッチングマスク(50)を除去する除去工程と、除去工程の後に残存したGaN系半導体層(11)に対してドライエッチングを実施する第2エッチング工程と、を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

81 - 100 / 467

[ Back to top ]