Fターム[5F033QQ27]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 導電膜 (467)

Fターム[5F033QQ27]に分類される特許

101 - 120 / 467

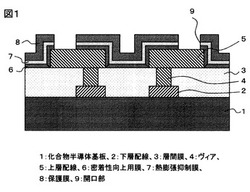

半導体装置およびその製造方法

【課題】保護膜の亀裂や膜剥がれを防止する。

【解決手段】化合物半導体基板1上に少なくとも一層からなる下層配線2を形成し、化合物半導体基板1上に有機材料からなる層間膜3を堆積し、層間膜3上に金からなる上層配線5を形成し、層間膜3中に下層配線2と上層配線5とを接続するヴィア4を形成し、上層配線5の表面および層間膜3の表面の上にシリコン窒化膜からなる密着性向上用膜6を形成し、密着性向上用膜6上にシリコン酸化膜からなる熱膨張抑制膜7を形成し、熱膨張抑制膜7上にシリコン窒化膜からなる保護膜8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスク膜による焦点深度のマージンの低下及びアライメントマークの視認性の低下を防ぎ、且つ、セルフアラインドビアの形成を可能とすることにより、配線同士のショートによる歩留まりの低下を防止すると共に、配線同士の絶縁性を高め、その信頼性を向上させるようにする。

【解決手段】半導体装置の製造方法は、基板10の上に、少なくとも1層の絶縁膜を含む層間絶縁膜12を形成し、層間絶縁膜12の上部に第1のマスク膜16を埋め込むように形成し、層間絶縁膜12及び第1のマスク膜16の上に第2のマスク膜17を形成し、第2のマスク膜17を用いて、層間絶縁膜12にビアホール19を形成し、第1のマスク膜16を用いて、層間絶縁膜12に配線溝20を形成し、ビアホール19及び配線溝20に導電性材料を埋め込むことにより、ビア及び配線を形成する。

(もっと読む)

半導体装置

【課題】駆動安定性を高め、積層工程での歩留まりを向上させ、実装形態での長期信頼性を向上させた薄型半導体チップの積層パッケージを実現する。

【解決手段】チップ表面に半導体素子110と、半導体素子110に信号を供給する配線と信号用電極と電源用電極とグランド用電極を有し、チップ裏面に信号用電極と電源用電極とグランド用電極を有し、チップ表面の電極とチップ裏面の電極とを電気的に接続する貫通配線を有し、チップの裏面を覆い、グランド用電極と接続した導体層120が形成されている複数の半導体チップ500、501とインターポーザ502とが積層されている半導体パッケージ。

(もっと読む)

半導体装置の製造方法

【課題】成膜性及びエッチング耐性に優れる膜を形成し、微細加工技術に適する半導体装置の製造方法を提供する。

【解決手段】ウエハ18上にSiN膜2を形成する工程と、前記SiN膜2上にハードマスク膜を形成する工程と、前記ハードマスク膜をエッチングマスクとして前記SiN膜2をエッチングする工程と、を有し、前記ハードマスク膜は、窒化アルミニウム膜(AlN膜7)または窒化アルミニウムシリコン膜のうち少なくともいずれかを含むことを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置において、配線間距離が近接してもイオンマイグレーションを防止し、大幅に遅延化させる。

【解決手段】一端12aが半導体基板11の電極11cと導通され、他端にランド部13が設けられた再配線層12と、ランド部13の下面13bにおいて半導体基板11の一方の主面11aとの間に形成された絶縁樹脂ポスト部14と、一方の主面11aを覆い、かつランド部13の少なくとも一部が露呈されるように設けられた封止絶縁膜15とを有する半導体装置10において、再配線層12は、一方の主面11aから所定の距離をおいて一方の主面11aに平行に延在される配線部12bを有し、ランド部13の径が配線部12bの幅wよりも大きく、配線部12bは、その長手方向に垂直な断面において周囲が全周にわたって、連続体からなる同一の前記封止絶縁膜によって覆われている。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法を使用して配線を形成する半導体装置の製造技術において、信頼性の高い配線を形成する技術を提供する。

【解決手段】ハードマスク膜HM1上にハードマスク膜HM2が形成され、このハードマスク膜HM2上に有機樹脂膜ORFが形成された状態で、レジストCMPを実施する。これにより、ハードマスク膜HM2上に形成されている有機樹脂膜ORFが除去されるとともに、ハードマスク膜HM2の膜厚が膜減りする。その後、膜減りしたハードマスク膜HM2を除去し、露出したハードマスク膜HM1をマスクにしてトレンチを加工する。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造等を含む半導体装置の製造工程を簡略化する。

【解決手段】半導体装置の製造方法は、基板101上に絶縁膜102を形成する工程(a)と、絶縁膜102上にハードマスク膜103を形成する工程(b)と、ハードマスク膜103上に第1のモールド108を接触させて、陽極酸化により第1の酸化領域110を形成する工程(c)と、ハードマスク膜103上に第2のモールド111を接触させて、陽極酸化により第2の酸化領域112を形成する工程(d)と、第1の酸化領域110及び第2の酸化領域112を除去してハードマスク103aを形成する工程(e)と、ハードマスク103aをマスクとするエッチングにより、絶縁膜103中に接続孔104及び配線溝105を形成する工程(f)とを備える。第1の酸化領域110と第2の酸化領域112とは面積及び深さが異なる。

(もっと読む)

ウェットエッチング方法

【課題】作業効率がよく、エッチングされる基板の材料の選択範囲も大きい、ウェットエッチング方法を提供する。

【解決手段】パターニングされたクロム層2及びレジスト層3を表面に有するガラス基板1をエッチング液4に浸しウェットエッチングする。その際、アルミニウム又は鉄からなる金属棒6がタンク5内のエッチング液4に浸され、所望のタイミングで、クロム層2の露出面2aと金属棒6の端部とが接触される。金属棒6と接触されたクロム層2は電気化学反応等により徐々にエッチングされ小さくなり、ガラス基板1のエッチング液4にさらされる部分が徐々に増え、その部分がウェットエッチングされる。これによりガラス基板1のアンダーカット形状が調節され、ガラス基板1にテーパ面7が形成される。ガラス基板1としては、例えば、石英、白板ガラス、青板ガラス、ホウケイ酸ガラス、無アルカリガラス、又は鉛ガラス等が適用可能である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いドレインコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】第1ドレインコンタクト14を形成する工程と、第1ドレインコンタクト14に接続された第2ドレインコンタクト15を形成する工程と、第2ドレインコンタクト15に接続された配線16を形成する工程と、配線16をマスクとして自己整合的に、少なくとも第2ドレインコンタクト15の近傍の第2層間絶縁膜33に、第1層間絶縁膜13と第2層間絶縁膜33との界面34より深い位置まで不純物イオンを注入し、界面34に残置されている異物32をアモルファス化する工程と、不純物イオンが注入された第1および第2層間絶縁膜13、33をエッチングして異物32を露出させ、異物32を除去する工程と、第1絶縁膜13上に配線16を覆うように第3層間絶縁膜36を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部をマスク層又は中間層に形成することができる制御性に優れた基板処理方法を提供する。

【解決手段】アモルファスカーボン膜51、SiON膜52,BARC膜53及びフォトレジスト膜54が順に積層されたウエハWを処理する基板処理方法であって、CHF3ガスと、CF3Iガスと、H2ガス及びN2ガスの混合ガスから生成されたプラズマによって、フォトレジスト膜54の開口部55のCD値を縮小しつつ開口部底部のSiON膜をエッチングするシュリンクエッチングステップと、開口部55の側壁面へのデポの堆積を促進させて各CD値のばらつきを吸収するばらつき吸収ステップと、開口部の内面に薄膜を形成して各開口部の開口幅を縮小させる開口幅縮小ステップとを1ステップで行う。

(もっと読む)

薄膜のパターニング方法、デバイス及びその製造方法

【課題】本発明は、表面エネルギーの低い薄膜に、ダメージなくパターニングを行う薄膜のパターニング方法、デバイス及びその製造方法を提供することを目的とする。

【解決手段】薄膜20上に、蒸着膜30を積層する工程と、

前記蒸着膜上に、フォトレジスト層40を積層する工程と、

フォトリソグラフィにより、前記フォトレジスト層をパターニングし、パターニングされた前記フォトレジスト層を用いて前記蒸着膜をエッチングしてパターニングする工程と、

パターニングされた前記蒸着膜をパターンマスクとして、前記薄膜をエッチングしてパターニングを行う工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属層30aを形成する工程と、素子ZDの接続部に到達するコンタクトホールCH1を形成する工程と、コンタクトホールCH1内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属層30aを利用して、貫通電極20に接続される第1配線層40と、コンタクトホールCH1を通して素子ZDの接続部に接続される第2配線層40aとを形成する工程とを含む。

(もっと読む)

離間された導電配線に電気的接続を提供する方法

集積回路及び形成方法は、少なくとも1つの直線的に延在する導電配線の斜端に形成されたコンタクト領域を提供する。実施形態では、コンタクトランディングパッドを有する導電配線は、マスク材料に配線をパターン化することと、材料配線の延在方向に対して角度を形成するために少なくとも1つの材料配線を切断することと、マスク材料の斜端面から拡張部を形成することと、前記材料配線及び拡張部をマスクとして用いてエッチングすることによって基本的な半導体をパターン化することとによって形成される。他の実施形態では、少なくとも1つの導電配線は、斜端面を作るように導電配線の延在方向に対して角度を付けて切断されるとともに、電気的コンタクトランディングパッドは、斜端面にコンタクトして形成される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通配線が断線しにくい信頼性の高い半導体装置1および半導体装置1の製造方法を提供する。

【解決手段】第1の主面10Aと第2の主面10Bとを貫通する基板貫通孔10Hが形成された半導体基板と、第1の主面10Aから離れるにしたがい開口が段階的に小さくなる層間膜貫通孔13Hが形成された層間絶縁膜13とデバイス11と接続された再配線層14とを有する多層配線層15と、再配線層14と接続され層間膜貫通孔13Hの開口部を覆う電極パッド16と、電極パッド16から層間膜貫通孔13Hの側壁および基板貫通孔10Hの側壁を介して第2の主面10B側まで配設された貫通配線19と、第2の主面10B側の貫通配線19上に配設されたバンプ21と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】配線構造における強度の向上と層間絶縁膜の低誘電率化との両立を図れるようにする。

【解決手段】半導体基板100の上に絶縁膜104を形成し、該絶縁膜104の上に金属からなる犠牲膜105を形成する。その後、犠牲膜105を選択的にエッチングすることにより犠牲膜105にトレンチパターン105aを形成する。続いて、トレンチパターン105aが形成された犠牲膜105をマスクとして、絶縁膜104に対して紫外線又は電子線を照射する。その後、トレンチパターン105aが形成された犠牲膜105をマスクとして、絶縁膜104に配線形成溝104aを形成し、該配線形成溝104aに金属膜106bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ法の露光解像限界を超えた寸法を有するパターンの形成において、工程数を削減し、製造コストを抑えることができる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様は、被加工膜2上に、被加工膜2を加工する際のマスク材となる膜をCVD法によって形成するに当って、第1の温度条件でマスクとして機能する第1の領域3を形成し、第1の領域3上に、同一チャンバー内にて第1の温度条件を変えた第2の温度条件で反射防止膜として機能する第2の領域4を形成し、第1および第2の領域3、4からなる第1のマスク材膜5を形成する工程を含む半導体装置の製造方法を提供する。

(もっと読む)

101 - 120 / 467

[ Back to top ]