Fターム[5F033QQ47]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | 機械的研磨 (214)

Fターム[5F033QQ47]に分類される特許

101 - 120 / 214

半導体基板上のスルーインターコネクトを製造する方法

半導体基板のスルーインターコネクトを製造する方法は、基板の第1側部上に基板を部分的に通るビアを形成するステップと、第1側部上及びビア内に電気絶縁層を形成するステップと、絶縁層上にビアを少なくとも部分的にライニングする導電層を形成するステップと、ビア内の導電層上に第1コンタクトを形成するステップと、ビア内の、少なくとも絶縁層まで基板の第2側部から基板を薄層化するステップとを含む。また、本方法は、第1コンタクトと電気接続状態にある第2コンタクトを基板の第2側部に形成するステップをも含み得る。本方法は、ウエハスケールのインターコネクト要素を形成するように半導体ウエハ上で実行可能である。さらに、インターコネクト要素を、発光ダイオード(LED)システムのような半導体システムを構築するのに使用可能である。 (もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置において貫通電極の信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコン基板10の第1主面上に形成された絶縁膜25と、第1主面上の絶縁膜25内に形成され、導電膜からなりその導電膜の少なくとも1部に導電膜が存在しない空き領域を有する電極パッド26Bと、第1主面に対向する第2主面上に形成されたハンダボール18と、シリコン基板10の第2主面側から空けられ電極パッド26Bまで達した貫通孔内に形成され、電極パッド26Bとハンダボール18とを電気的に接続する貫通電極とを備える。電極パッド26Bが有する空き領域には絶縁膜25が存在し、空き領域に存在する絶縁膜25と電極パッド26Bとの貫通電極側の段差が電極パッド26Bの厚さ以下である。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

銅要素の結晶構造を修正する方法

平坦面を伴う銅要素(II’)の結晶構造を修正する方法であって、a)大粒子を有し、且つ平坦面を含む銅標準(I’)を作る段階と、b)前記平坦面(14、16)の粗さを1nm未満の粗さまで低減する段階と、c)前記平坦面(14、16)を洗浄する段階と、d)前記2つの平坦面(14、16)を接触させる段階と、e)アニーリングする段階と、を含む。前記粗さは0.5nm以下である。この方法は更に、前記標準(I’)と前記要素(II’)とを分ける追加段階f)を含む。  (もっと読む)

(もっと読む)

貫通電極工程性能の試験ウエハ

【課題】ウエハを張り合わせて高集積デバイスを製造するためにウエハを貫通する電極を形成する。その製造工程を広い性能水準で評価するために共通に使用できるウエハ、即ちテストウエハが必要であった。

【解決手段】工程の広い性能水準を評価できるように、孔の形や深さ、底面の形、設計仕様を表す文字の入れ方を貫通電極の工程の特徴を踏まえて設計した。そのために、トレンチのパターンと孔の混在、丸から多角形・四角までの平面形状、異なる深さ、丸い底面を持つテストウエハを発明した。

(もっと読む)

半導体装置、半導体ウェハおよびその製造方法

【課題】バンプ電極を各チップ領域に形成した半導体ウェハを個々の半導体チップに個片化する際、個片化された半導体チップにクラックが発生することを抑制できる技術を提供する。

【解決手段】半導体ウェハWFの主面に接着テープATを貼り付けた状態で、半導体ウェハWFの裏面に溝DTを形成する。半導体ウェハWFの裏面に溝DTを形成するには、半導体ウェハWFの裏面にレジスト膜を塗布した後、フォトリソグラフィ技術を使用することにより、レジスト膜をパターニングする。レジスト膜のパターニングは、溝DTを形成する領域にレジスト膜が残らないように行なわれる。そして、パターニングしたレジスト膜をマスクにしたドライエッチング技術により、半導体ウェハWFの所定領域に溝DTを形成する。具体的に、ダイシングラインDLの近傍領域に溝DTを形成する。

(もっと読む)

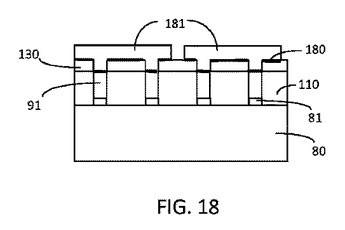

金属/有機誘電体界面でのクラックの低減

有機誘電体材料(110)中に埋め込まれた第2構造(91)への金属相互接続(181)を提供する方法であって、有機誘電体材料(110)中に埋め込まれた、例えば金属ピラー(91)のような第2構造を有する第1構造を得る工程と、少なくとも第1構造のいくつかの位置で、有機誘電体材料(110)の上に硬い層(130)を提供する工程であって、硬い層(130)は有機誘電体材料(110)の剛性より高い剛性を有する工程とを含む方法。この方法は、第1構造(91)と有機誘電体材料(110)との間の界面でクラックの無い相互接続構造を提供する。  (もっと読む)

(もっと読む)

配線パターンの形成方法

【課題】インプリントモールドの凹部への感光性配線ペースト層の充填不良や、ウェットエッチング(現像)工程での配線パターンの倒壊や剥がれの発生を抑制,防止して、効率よく精度の高い配線パターンを形成する。

【解決手段】感光性配線ペースト層2を形成する工程と、凹凸パターン17を有するインプリントモールド3を感光性配線ペースト層2に押し付けて光照射する工程と、感光性配線ペースト層2の未感光部をウェットエッチングにより除去して、インプリントモールドの凹凸パターンに対応する配線パターンを形成する工程とを備えた配線パターンの形成方法において、感光性配線ペースト層2の厚みtpを下記の式(1)の範囲で規定する。

6μm+(V/S)<tp<20μm+(V/S)……(1)

ただし、

tp:感光性配線ペースト層の厚み、

S:ペースト転写領域の面積、

V:前記凹凸パターンの、前記感光性配線ペースト層と接する領域における凹部の体積

(もっと読む)

基板の表面に樹脂絶縁膜のパターンを形成する方法及び半導体装置

【課題】基板の表面に樹脂絶縁膜のパターンを切削加工で形成する方法及び半導体装置を提供する。

【解決手段】半導体装置の製造方法において、接続用の電極(2)が一主面に形成された半導体基板(1)において、前記接続用の電極(2)を覆うように前記一主面側に樹脂絶縁膜(3)を形成する第1工程と、すくい角をゼロ又は負とした、バイト(4)による切削加工により、前記接続用の電極(2)の接続部位(21)を露出させるように、テーパ部(10)と前記接続部位(21)とからなる開孔(31)を形成する第2工程とを具備することを特徴とする。

(もっと読む)

半導体装置、及びその製造方法

【課題】貫通電極を備える半導体装置、及びその製造方法が提供される。

【解決手段】本発明は、パッド408が含まれた基板402sの一部を除去してビアホール420を形成する。前記基板の上に絶縁膜410を形成する。前記絶縁膜の一部を除去して前記パッドの一部を露出させる複数の開口を含む開口部435a,435bを形成する。前記ビアホールを満たして前記複数の開口のうちの何れか1つを通じて前記パッドと電気的に連結する貫通電極440を形成する。前記複数の開口の中の他の1つを通じて前記パッドの一部を開放する。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板の側面を封止膜で覆い、下面を下層保護膜で覆った構造の半導体装置の製造に際し、シリコン基板の厚さをより一層薄くする。

【解決手段】 封止膜11を形成した後に、半導体ウエハ21の周辺部を除く底面側を回転研削砥石部30を用いて研削して凹部31を形成し、半導体ウエハ21の周辺部を除く部分を薄くする。この場合、封止膜11の存在および半導体ウエハ21の周辺部の残存により、半導体ウエハ21の厚さをより一層薄くしても、半導体ウエハ21が割れにくいようにすることができ、ひいてはシリコン基板1の厚さをより一層薄くすることができる。例えば、シリコン基板1の厚さは20〜30μmとかなり薄くすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドよりも径の小さな貫通孔を半導体基板自体に設けることなく、上下に積層された半導体チップ間の電気的な接続を行う。

【解決手段】半導体基板S1の横にはみ出すように電極パッドP1を配置し、半導体基板S1の周囲を取り囲むように配置された樹脂層J1上にて支持し、電極パッドP1が上下に重なるように半導体チップC1を積層し、貫通孔T1内に導電体D1を埋め込むことで、上下の電極パッドP1を電気的に接続し、上下に積層された半導体チップC1間の電気的な接続を行う。

(もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】オンチップアンテナからの出力信号が集積回路にノイズとして侵入することを防止するとともに、出力信号の効率を上げることの出来る半導体装置を提供する。

【解決手段】能動素子10が形成された素子形成領域Rpと、アンテナ形成領域Raに形成されたオンチップアンテナATと設けた半導体装置において、アンテナ形成領域Raを囲むように設けたシールド層形成領域Rs1に積層された導電層で形成され、不純物拡散層ID5、ID6の直上の層からオンチップアンテナATと同一の層に至るまで順次に形成されてパッドPを介してGND接続されるシールド層SL1を設ける。

(もっと読む)

半導体装置とその製造方法

【課題】集積回路の信号用の端子との干渉を避けつつ、半導体装置のシールリングを介したノイズの影響を低減する。

【解決手段】半導体装置は、基板上に形成された集積回路と、その集積回路を取り囲むシールリングとを有する。シールリングの第一部分は基板の裏面に到達し、その裏面側において電位が一定の端子に接続されている。裏面側から一定電位の端子に接続することにより、表面側の信号用端子と干渉することなくシールリングによるノイズ伝搬を防ぐことができる。

(もっと読む)

半導体装置

【課題】電極パッドの異常を容易に発見することが可能である。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板の第1領域における第1表面から前記第1表面に対向する第2表面まで空けられた第1貫通孔80内に形成された第1貫通電極25と、前記半導体基板の前記第1表面において、前記第1貫通電極に接して形成された第1電極パッド28と、前記第1電極パッドと離間して形成され、前記第1電極パッドと対向する第2電極パッド29と、前記半導体基板の前記第2表面上に形成され、前記第1貫通電極と電気的に接続された外部端子27と、前記半導体基板の前記第1表面において、前記半導体基板の前記第1領域と異なる第2領域における前記第1表面から前記第2表面まで空けられた第2貫通孔80上に形成され、電気的に浮遊した第3電極パッド28と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】ウェハ面内の再配線層の厚みのばらつきを低減し、所望の電気的特性を得ることのできる多層再配線構造を有するWCSP型の半導体装置及びその製造方法を提供する。

【解決手段】第1の再配線層を形成する工程において、第1の導電材料をめっき法により成長させて第1の再配線層より厚い第1の導電材料層を形成し、第1のレジスト膜及び第1の導電材料層を主面側から研磨して表面を平坦化して、第1の再配線層を形成する処理、及び、第2の再配線層を形成する工程において、第2の導電材料をめっき法により成長させて第2の再配線層より厚い第2の導電材料層を形成し、第2のレジスト膜及び第2の導電材料層を主面側から研磨して表面を平坦化して、第2の再配線層を形成する処理の少なくとも一方の処理を行う。

(もっと読む)

低k誘電体ライナーを有するシリコン貫通ビア

【課題】 シリコン貫通ビアを有する半導体デバイスを提供する。

【解決手段】 回路面と前記回路面とは逆の背面を有する半導体基板、前記半導体基板を穿通して延伸するシリコン貫通ビア、及び前記シリコン貫通ビアと前記半導体基板の間に設置され、前記半導体基板の前記背面の表面の少なくとも一部の上に延伸する誘電体層を含む半導体デバイス。

(もっと読む)

ヒューズ式スルー・シリコン・ビアを有する3Dチップ・スタック

【課題】シリコン・チップ中のプログラム可能ヒューズ式スルーシリコン・ビア(TSV)を、同一のチップ中の非プログラム型TSVと併せ提供する。

【解決手段】該プログラム可能ヒューズ式TSVには、該TSV構造内に、チップ表面コンタクト・パッドに隣接するTSVの導電路の断面を限定する側壁スペーサを有する部域を用いることができる。プログラミング回路による十分な電流の印加により、金属のエレクトロマイグレーションが生じ、コンタクト・パッド中にボイド、しかしてオープン回路、が生成される。プログラミングは、多階層チップ・スタック中の2つの隣接するチップ上の相補的回路によって実行することができる。

(もっと読む)

シリコン貫通電極(TSV)を露出させ接触させる高歩留まりの方法

【課題】 シリコン貫通電極を露出させ接触させるための高歩留まりの技法を提供する。

【解決手段】 前側および裏側を有する本体を有する主ウェハを含むアセンブリを取得する。主ウェハは、裏側より上で終端する複数のブラインド電気バイアを有する。ブラインド電気バイアは、導電コアを有し、コアの隣接する側方領域および端部領域に周囲絶縁体を有する。ハンドラ・ウェハは、主ウェハの本体の前側に固定されている。追加のステップは、裏側でブラインド電気バイアを露出させることを含む。ブラインド電気バイアは、裏側全体で様々な高さに露出される。別のステップは、裏側に第1の化学機械研磨プロセスを適用して、露出ステップの後に残っているコアの端部領域に隣接した周囲絶縁体を開放すると共に、バイア導電コア、コアの側方領域に隣接した周囲絶縁体、および主ウェハの本体を同一平面にすることを含む。更に別のステップは、裏側をエッチングして、裏側全体でバイアの各々の均一なスタンドオフ高さを与えることを含む。更に、裏側全体に誘電体を堆積し、裏側に第2の化学機械研磨プロセスを適用して、バイアの導電コアに隣接した誘電体のみを開放する。

(もっと読む)

101 - 120 / 214

[ Back to top ]