Fターム[5F033QQ47]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | 機械的研磨 (214)

Fターム[5F033QQ47]に分類される特許

121 - 140 / 214

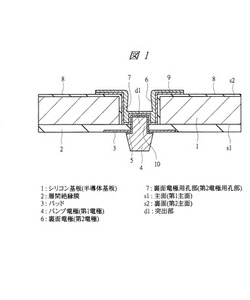

半導体装置およびその製造方法

【課題】複数の半導体チップを多数積層した半導体装置において、生産性を損なうことなく高性能化する。

【解決手段】シリコン基板1の主面s1上に順に形成された複数の素子、層間絶縁膜2およびパッド3と、パッド3に電気的に接続するバンプ電極4と、シリコン基板1の裏面s2に形成され、バンプ電極4に電気的に接続する裏面電極6とを有する半導体装置である。バンプ電極4は、パッド3を貫通し、シリコン基板1側に向かって突出するような突出部d1を有する。また、裏面電極6は、シリコン基板1の裏面s2側から主面s1側に向かって、バンプ電極4の突出部d1に達し、パッド3には達しないような裏面電極用孔部7の内側を覆うようにして形成されていることで、バンプ電極4と電気的に接続されている。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含む。また、導通部106は、結晶粒径が29μm以上の金属材料を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極のショート不良を引き起こすことなく、貫通電極とパッド電極との密着性を向上させる。

【解決手段】開口部22が設けられたパッド電極21b上にエッチストッパ膜23を積層し、半導体基板11に形成された貫通孔41に貫通電極45を埋め込む際に、貫通電極45の先端が、開口部22を介してパッド電極21bの一部を突き抜け、エッチストッパ膜23で止められるように構成する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電流損失を低減した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の金属材料は、結晶粒径が29μm以上の結晶粒を含む。また、導通部106の金属材料は、面積重み付けした平均結晶粒径が13μm以上である。

(もっと読む)

一体型ビア及びビア端子を有する半導体回路基板、並びに関連するシステム及び方法

一体型ビア及びビア端子を有する半導体回路基板と、関連のシステム及び方法とが開示されている。特定の実施例に従う代表的な方法は、半導体回路基板に非貫通ビア(140)を形成することと、ビアの側壁面に保護層(122)を塗布することと、保護層が塗布された回路基板材料の除去から保護している間に、ビアの端面から回路基板材料を選択的に除去することにより端子穴(111)を形成することと、を含む。この方法は、ビア内の導電性材料が単一である導電性端子を形成するためにビア及び端子穴の双方に導電性材料を配置することをさらに含むことができる。端子に隣接する回路基板材料は、その後、回路基板の外部の導電性構造体に接続することができる端子を露出させるために除去することができる。 (もっと読む)

半導体素子および半導体素子の製造方法

【課題】基板表面上に半導体素子構造を形成した後に、基板を裏面側から研削した場合に生じる基板の反りを防止でき、容易にダイシング処理を行うことができ、高集積でパッケージングされる半導体素子として好適な厚みの薄い半導体素子を提供する。

【解決手段】基板1表面上に形成された半導体素子構造と、前記半導体素子構造内に形成され、基板1を裏面側から研削することにより発生する前記基板1を反らせるストレスを補償する補償ストレス膜6とを備えている半導体素子とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 配線の引き回しに制約を受けにくいようにする。

【解決手段】 第1の保護膜5上には複数の配線7が設けられている。配線7を含む第1の保護膜5上には、配線7の接続パッド部7cに対応する部分に開口部11を有する第2の保護膜10が設けられている。第2の保護膜10の開口部11を介して露出された配線7の接続パッド部7c上面およびその周囲における第2の保護膜10上には柱状電極13が設けられている。これにより、配線7の接続パッド部7cの平面サイズが柱状電極13の平面サイズよりも小さくなり、配線7の接続パッド部7c間の間隔を広くすることができ、ひいては配線7の引き回しに制約を受けにくいようにすることができる。

(もっと読む)

3−D積層型デバイスのESD保護を可能にするシステム及び方法

【解決手段】静電気放電(ESD)保護デバイスが、積層型半導体ダイのアクティブレイヤ間の縦型の空間に形成され、これにより、そうでなければ通信目的のためにしか使用されないであろう空間を利用する。シリコン貫通ビア(TSV:through silicon via)の縦型の表面領域は、ESDイベントに起因する大電圧を緩和するために使用される。一実施形態では、ESDダイオードは、積層型デバイスの半導体ダイのアクティブレイヤ間の縦型TSV内に形成される。このESDダイオードは、積層の半導体ダイの両方の上の回路によって共有され、これによって空間を節約し、そしてESD保護回路によって必要とされるダイ面積を低減し得る。 (もっと読む)

積層チップパッケージおよびその製造方法

【課題】正常に動作しないチップに接続された配線に起因する問題を低減しながら、正常に動作しないチップを使用不能にする。

【解決手段】積層チップパッケージ1は、複数の階層部分11〜18を含む本体2と、本体2の側面に配置された配線3A,3Bとを備えている。複数の階層部分は、第1の種類の階層部分11〜16,18と、第2の種類の階層部分17とを含んでいる。第1の種類の階層部分と第2の種類の階層部分は、いずれも、半導体チップを含んでいる。第1の種類の階層部分は、それぞれ半導体チップに接続され、配線3A,3Bが配置された本体2の側面に配置された端面を有する複数の電極を含むが、第2の種類の階層部分は、半導体チップに接続されると共に配線3A,3Bが配置された本体2の側面に配置される端面を有する電極を含んでいない。配線3A,3Bは、複数の電極の端面に接続されている。

(もっと読む)

3次元集積回路の製造方法及び記録媒体(インターフェース・ウエハを永久的キャリアとして使用する3次元集積回路デバイスの製造方法)

【課題】 3次元集積回路構造を製造する方法を提供する。

【解決手段】 第1配線層及びスルー・シリコン・ビアを含むインターフェース・ウエハ並びに能動回路を含む第1の能動回路層ウエハを準備する。第1の能動回路層ウエハはインターフェース・ウエハにボンディングされる。次いで、第1の能動回路層ウエハの第2部分がインターフェース・ウエハに取り付けられたままになるように、第1の能動回路層ウエハの第1部分が除去される。インターフェース・ウエハ及び第1の能動回路層ウエハの第2部分を含む積層構造がベース・ウエハにボンディングされる。次に、インターフェース・ウエハはインターフェース層を形成するように薄くされ、そしてインターフェース・ウエハのスルー・シリコン・ビアを介して第1配線層に結合される金属がインターフェース・ウエハ上に形成される。

(もっと読む)

導電性保護膜を有する貫通電極構造体及びその形成方法

【課題】半導体基板の歪みを抑制することができ、低い接触抵抗を有する貫通電極構造体及びその形成方法を提供する。

【解決手段】貫通電極(Through−Silicon−Via:TSV)構造体は、基板の上部表面から該上部表面に対向する基板の下部表面に延長されて基板を貫通する導電性ビアと、導電性ビアの底部に形成されてNi及びCoのうちのすくなくともいずれかを有する導電性保護膜と、導電性保護膜に接触して基板の下部表面に形成される分離ポリマー絶縁膜と、を備える。

(もっと読む)

半導体装置の製造方法、半導体装置及び半導体装置の製造装置

【課題】製造工程数を増加させることなく配線上にキャップメタル膜を選択的に形成することにより、配線間リーク電流の増大及び配線間ショートを抑制する。

【解決手段】絶縁膜に埋め込まれた配線を有する半導体装置の製造方法において、基板上に形成された絶縁膜に溝を形成する工程と、前記溝に導電膜を埋め込む工程と、それぞれに電解液が注入された複数の貫通孔を有する基体を前記導電膜の表面に接触させながら、前記電解液と電気的に接続されたアノードと前記基体表面に露出したカソードとの間に電位差を付与することで、前記導電膜が埋め込まれた前記絶縁膜を表面処理する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ビットコンタクトと容量コンタクトとの接触を防止する。

【解決手段】拡散層領域121,122を有するトランジスタ111と、層間絶縁膜151に埋め込まれ、それぞれ拡散層領域121,122に接続されたセルコンタクト131,141と、層間絶縁膜152に埋め込まれ、セルコンタクト131に接続されたビットコンタクト132と、層間絶縁膜153に埋め込まれ、ビットコンタクトと接続されたビット線130と、層間絶縁膜152,153に埋め込まれ、セルコンタクト141と接続された容量コンタクト142とを備える。ビット線130の側面130aは、ビット線130の延在方向に沿ったビットコンタクト132の側面132aと一致している。これにより、ビットコンタクトと容量コンタクトが直接短絡することがなくなるため、容量コンタクトの形成マージンが拡大する。

(もっと読む)

基板、特に半導体ウェハの加工

【課題】切削速度、アライメント時間及び歩留りを改善しスループットを高める。

【解決手段】基板の第1の面側から、基板の全深さには満たない所定の深さまで、紫外または可視放射レーザによって溝を掘る。次に、第1の面の反対側である第2の面側から、前記溝が貫通するように基板の材料を除去する。この材料の除去は、例えば、ラッピング及び研磨、化学的エッチング、プラズマエッチングまたはレーザアブレーションによって行う。

(もっと読む)

導体または半導体基板上に堆積させたカーボンナノチューブマットの製造方法

【課題】酸化層の前堆積を行うことなく、導体または半導体材料上に高密度のカーボンナノチューブマットを製造する方法を提供する。

【解決手段】拡散バリア520、拡散バリア上にアモルファスシリコン層530、アモルファスシリコン層上に金属層を含む触媒複合体を導体または半導体基板510上に堆積させる。次いで前記金属層に酸化処理を行い、最後に、酸化処理された金属層からカーボンナノチューブマット580を成長させる。

(もっと読む)

半導体装置の製造方法並びに研削装置及び研削方法

【課題】樹脂により形成された層を研削する工程を有する半導体装置の製造方法において、研削用砥石又は研磨紙の目詰まりを容易に解消し、半導体装置の製造コストを低減する。

【解決手段】被処理物20(例えば、樹脂層を有する半導体基板)は回転台21の上に保持される。この被処理物20の表面を、ホイール23に保持されたリング状の砥石22により研削する。砥石22にはレーザ光源24からレーザ光が照射される。このレーザ光により、砥石22に付着した付着物(樹脂)がアブレーションして、砥石22から除去される。樹脂以外の付着物も、アブレーションにより発生したガスにより砥石22の面から吹き飛ばされて除去される。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体ウェーハおよびそれを生成する方法

薄化中央部分(2)をもつ半導体ウェーハ(12)は、第1の側(3)および第2の側(4)、ならびに半導体ウェーハ(12)の半径方向屈曲耐性を増大させるための少なくとも1つの補強構造体を有する。補強構造体は、前記1つの補強構造体の内面(9)から補強構造体の外面(8)に向かう流体流れのための少なくとも1つの通路(10)を備える。通路(10)は、半導体ウェーハ(12)の上方から来るz方向で、半導体ウェーハ(12)の表面、例えば第1の側(3)に本質的に垂直である方向で製造される。  (もっと読む)

(もっと読む)

半導体装置の製法

【課題】研削時の半導体ウェーハの高温加熱及びクラックの発生を防止し、且つ保護樹脂を損傷させずに半導体チップの各側面に形成する。

【解決手段】半導体ウェーハ(1)の一方の主面(1a)に格子状の複数の第1の溝(4)を形成し、半導体ウェーハ(1)の他方の主面(1b)に向かって第1の溝(4)より幅細の第2の溝(30)を第1の溝(4)の底部(4a)に形成する。その後、第1の溝(4)内に粘性のある保護樹脂(6)を充填して、保護樹脂(6)により第2の溝(30)を覆って空洞部(7)を形成する。半導体ウェーハ(1)を加熱して、保護樹脂(6)を硬化させ、第1の溝(4)と第2の溝(30)との境界面又は境界面に到達する手前まで半導体ウェーハ(1)の他方の主面(1b)を研削し、分割線(D)に沿って保護樹脂(6)を切断することにより、複数の半導体チップ(3)が得られる。

(もっと読む)

121 - 140 / 214

[ Back to top ]