Fターム[5F033QQ47]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | 機械的研磨 (214)

Fターム[5F033QQ47]に分類される特許

81 - 100 / 214

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

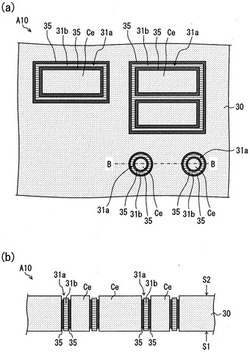

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体ウエハの裏面側を研削する工程において、主面側が汚染されることを抑制する。

【解決手段】裏面2b側を研削する半導体ウエハ20のスクライブ領域1bの交差部に、デバイス領域1aに積層される配線層5を構成する絶縁層(第1絶縁層)3と同様に主面2a上に複数の絶縁層3を積層する。また、デバイス領域1aに形成される複数の配線層5のうち最上層に配置される配線層(最上層配線層)5cに形成された配線(最上層配線)と同層に金属パターン10を形成する。さらに、この最上層配線を覆う絶縁層(第2絶縁層)9を、金属パターン10の上面にもこれを覆うように形成する。

(もっと読む)

ウエハレベルCSPの製造方法

【課題】 ウエハレベルで組立て可能な薄型CSPを提供する。

【解決手段】 ウエハ裏面側に、スクライブライン上の特定箇所に形成したスルーホールの側面を利用して,ウエハ表裏間の電気接合を取り、基板実装用の電極を配置する。そしてスルーホールは半導体基板のスクライブライン上をハーフエッチングした凹部を、バックグラインドを用いて裏面研磨することで形成する。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

電子装置の切断方法

【課題】半導体装置を含む電子装置の製造コストの増大を抑制可能であり、かつ、低誘電体膜の損傷を防止可能な電子装置の切断方法を提供すること。

【解決手段】本電子装置の切断方法は、基板上に複数の絶縁層及び複数の配線層が積層されている電子装置を準備する第1工程と、ブラスト処理を含む工程により、前記電子装置の切断可能領域に存在する全配線層及び全絶縁層を除去して前記基板を露出させる第2工程と、前記切断可能領域に露出する前記基板をブレードにより切断する第3工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】内部接続端子にクラックを生じさせない、信頼性を高めたパッケージの製造方法を提供する。

【解決手段】電極パッドを有する半導体集積回路を含む半導体チップが複数配置された半導体基板と、半導体基板上の再配線層とを有する半導体装置の製造方法であって、半導体集積回路の領域の間に位置するスクライブ領域の中に溝部を加工するため、溝部以外の領域を保護する保護マスクを半導体基板に張り付ける、保護マスク張り付け工程(S101)と、溝部を加工する溝部加工工程(S102)と、保護マスクを第1絶縁層の形成のためのスクリーンマスクとして使用して、溝部を覆うように第1絶縁層を形成する、第1絶縁層形成工程(S103)とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面とを有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記貫通孔の内壁に設けられ、平面視において前記貫通孔と重なる位置に接続孔を有する樹脂膜と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に第1凹部を有する配線層と、前記配線層に接続され、前記第1凹部内と前記樹脂膜を介して前記貫通孔内とに設けられた貫通電極とを含む半導体装置。

(もっと読む)

貫通電極基板及び貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板は、表裏を貫通する貫通孔を有する基板と、前記貫通孔内に充填され、金属材料を含む導通部と、を備え、前記導通部は、結晶粒径が29μm以上の金属材料を少なくとも含み、前記導通部の一端は、前記導通部の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部は、面積重み付けした平均結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パッケージ端部の樹脂層の一部が剥離し、耐湿性が悪化するという問題があった。

【解決手段】本発明の半導体装置では、シリコン基板2の一主面側に再配線層5、5Aと剥離防止層6が配置され、それらを被覆するように樹脂層3が形成される。剥離防止層6は、再配線層5、5Aの無配置領域であり、半導体装置1の外周端部近傍に配置されることで、樹脂層3の樹脂量が低減される。この構造により、樹脂層3の熱収縮力に起因する樹脂の反り上がりが防止し、樹脂層3が、シリコン基板2上から剥離することが防止され、半導体装置1の耐湿性が向上される。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

クラックストップを備えたデバイス

基板上のデバイスと基板内のクラックストップとを備える装置である。デバイスを形成する方法も開示される。これらの方法は、半導体デバイスのようなデバイスを第1の厚さを有する基板上に設けることと、基板の厚さを第2の厚さまで低減することと、クラックストップを基板内に設けることとを含み得る。基板の厚さを低減することは、この基板を支持用の担体基板に取り付けることと、その後、この担体基板を取り外すこととを含み得る。クラックストップは、クラックがデバイスに到達することを妨げ得る。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極およびこれと一体的に形成された裏面電極を有する半導体装置において、貫通電極の膜厚と裏面電極の膜厚とを独立に制御することにより、貫通電極の剥離の問題と裏面配線の剥離の問題を同時に解消することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板の上方に形成された少なくとも1層からなる配線層13と、半導体基板の裏面から配線に達する貫通電極30と、半導体基板の裏面に設けられて貫通電極に接続された裏面配線40と、裏面配線に接続された外部端子50と、を含む半導体装置であり、裏面配線は、少なくとも外部端子との接続部を含む部分の膜厚が、貫通電極の膜厚よりも厚く形成されている。

(もっと読む)

半導体装置の金属電極形成方法及び金属電極形成装置

【課題】切削量の要求精度(±1μm以内)を満たしつつコストを低減できる半導体装置の金属電極形成方法及び金属電極形成装置を提供する。

【解決手段】裏面11bの形状を反映して表面部11aの凹凸差が増大した半導体基板11の凹凸差を低減すべく、表面部の表面形状データを取得し、このデータに基づいて変形手段により半導体基板に変位を与え、切削面Pと半導体基板の表面部との距離が切削量の要求精度の範囲内になるように変形させる。変形手段として、変位をそれぞれ制御可能な複数個のアクチュエータ24aを用い、各アクチュエータを、吸着ステージの裏面に当接してそれぞれ設けるとともに、その配置間隔を半導体基板の厚さ分布の空間周波数の最小波長に対し、1/2よりも大きく1以下とする。そして、変形させた半導体基板を吸着ステージに吸着固定したまま、切削面において切削加工を行い、金属膜をパターニングして金属電極15を形成する。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

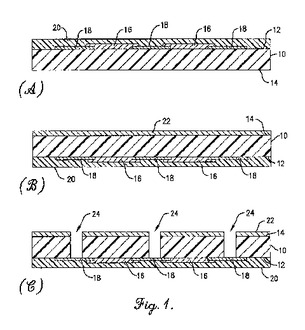

半導体装置の製造方法、半導体装置

【課題】ダイシング時で半導体チップに発生するチッピング、割れ、或いは欠けを低減する。

【解決手段】半導体装置80は、半導体チップ50がガラス基板60にFace Downして載置され、接着層10で半導体チップ50とガラス基板60が接着される。半導体チップ50には、シリコン基板1、集積回路部2、受光部3、層間絶縁膜4、樹脂層5、表面電極6、貫通電極8、裏面電極9、裏面保護膜12、ボール端子13が設けられる。樹脂層5は、シリコン基板1上に層間絶縁膜4と接するように半導体チップ50の端部に設けられる。樹脂層5は、層間絶縁膜4をエッチングした開口領域に設けられる。半導体装置80は、接着層10により固着されたシリコンウェハ100とガラス基板60をブレードダイシングにより個片化されたものである。

(もっと読む)

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液および無電解銅めっき方法を提供する。また、該無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】チオール基又はジスルフィド結合を有するポリエチレングリコール化合物、及び銅イオンを含有することを特徴とする無電解銅めっき液、さらに、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6を形成することを特徴とする無電解銅めっき方法、及び、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6からなる埋め込み配線を形成することを特徴とする埋め込み配線の形成方法。

(もっと読む)

半導体基板の製造方法

【課題】半導体基板が厚い場合においても貫通電極を高生産性、高品質で低コストで実現できる半導体基板の製造方法を提供することを目的とする。

【解決手段】半導体基板(101)にアクティブ面が露出する開口部(104)を有する電極パッド(102)を形成し、開口部(104)からアクティブ面の反対側の面に向かって凹部(105a)を形成し、凹部(105a)の内側に絶縁膜(106)を形成し、絶縁膜(106)と電極パッド(102)の表面に導電経路(107)を形成し、アクティブ面の反対側の面から半導体基板(101)を薄型化して凹部(105a)の底部を貫通させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の欠けや割れが抑制される半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面1aに、外周端部から内側に向かって所定の幅を有して外周端部に沿って延在するパッシベーション膜3を形成する。半導体基板1の外周端部を研削することにより、表面1aおよび裏面1bと直交する外周端面1cを形成する。裏面1bを研削することにより、半導体基板1の厚みを所定の厚みにまで薄くする。研削された裏面を上方に向けた状態で、半導体基板1を回転させながら裏面上に混酸を吐出することにより、裏面にエッチング処理を施して破砕層を除去する。

(もっと読む)

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

半導体装置

【課題】駆動安定性を高め、積層工程での歩留まりを向上させ、実装形態での長期信頼性を向上させた薄型半導体チップの積層パッケージを実現する。

【解決手段】チップ表面に半導体素子110と、半導体素子110に信号を供給する配線と信号用電極と電源用電極とグランド用電極を有し、チップ裏面に信号用電極と電源用電極とグランド用電極を有し、チップ表面の電極とチップ裏面の電極とを電気的に接続する貫通配線を有し、チップの裏面を覆い、グランド用電極と接続した導体層120が形成されている複数の半導体チップ500、501とインターポーザ502とが積層されている半導体パッケージ。

(もっと読む)

81 - 100 / 214

[ Back to top ]