Fターム[5F033QQ58]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 基板 (558)

Fターム[5F033QQ58]に分類される特許

81 - 100 / 558

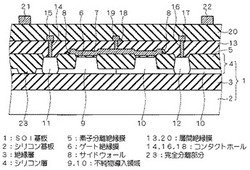

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

反射型液晶表示装置及びその製造方法

【課題】反射型液晶表示装置において、回路素子へ到達する入射光の量を低減するための技術を提供する。

【解決手段】回路素子に電気的に接続された、第1金属層112の上に、開口部127及び第1スルーホール126を有するようにパターニングされた第1絶縁層113を形成し、第1絶縁層に、開口部127に埋め込まれた金属部114及び第1スルーホール126に埋め込まれた第1プラグ115を形成した後、第2絶縁層116を形成する。第2絶縁層116の上に、開口部を有するようにパターニングされた第2金属層117を形成し、第2金属層の上に第3絶縁層119を形成した後、第2金属層117の開口部を通り且つ第1プラグ115の上面を露出させる第2スルーホール120を、第2絶縁層116及び第3絶縁層119に形成し、第2スルーホール120に埋め込まれた第2プラグ121と、第2プラグに接続された反射電極122とを形成する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

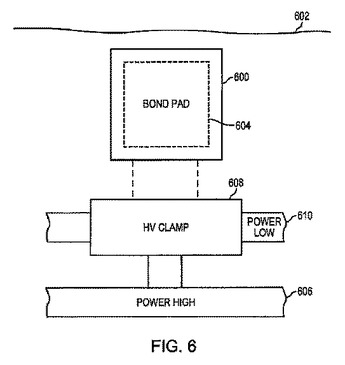

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

半導体デバイス用基板およびSOI基板

【課題】 裏面研削加工および裏面CMP処理が施されて製造される薄型半導体デバイスに用いられる半導体デバイス用基板であって、裏面研削を過不足なく行うことが可能であるとともに、研削加工の高速化を図ることができて、生産効率を向上させることができる半導体デバイス用基板を提供することである。

【解決手段】 半導体デバイス用基板10は、結晶性のシリコン基板11の内部に、構造変化層12が形成されたものである。この構造変化層12は、導電型領域を形成することがないイオンが注入されてなる層であって、シリコンとは異なる結晶構造に変化した層である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を内在する炭化珪素半導体を用いても、大面積半導体装置の高歩留りを安定して実現可能な半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体基板上に炭化珪素半導体層をエピタキシャル成長する工程と、炭化珪素半導体層表面を研磨する工程と、研磨する工程の後に、炭化珪素半導体層に不純物をイオン注入する工程と、不純物を活性化するための熱処理をする工程と、熱処理をする工程の後に、炭化珪素半導体層表面に第1の熱酸化膜を形成する工程と、第1の熱酸化膜を化学的に除去する工程と、炭化珪素半導体層上に電極層を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】配線構造に接続される低抵抗の貫通プラグ、または貫通プラグ及びコンタクトプラグを有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板1と、半導体基板1の表面近傍に埋め込まれた素子分離絶縁膜2と、素子分離絶縁膜2を貫通するように半導体基板1の裏面から表面まで貫通し、半導体基板1中で素子分離絶縁膜2に囲まれた領域を有する上段部101aと上段部101aよりも径が大きい下段部101bとを含む多段構造を有する貫通プラグ101と、貫通プラグ101の半導体基板1の表面側の端部に接続され、半導体基板1の表面側の上方に形成された電極パッド104と貫通プラグ101を接続するコンタクトプラグ103と、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】銅を用いた多層配線を有する半導体装置を高性能化する。

【解決手段】シリコン基板上に第1配線層用絶縁膜Z1を形成し、第1配線層用絶縁膜Z1に第1配線用孔部H1を形成する。その後、第1配線用孔部H1の側壁および底面を覆うようにして、タンタルまたはチタンを含む下部バリア導体膜eb1と、ルテニウムを主体とする上部バリア導体膜et1とからなる第1配線用バリア導体膜EM1を形成する。続いて、上部バリア導体膜et1をシード層として、電気めっき法により、銅を主体とする第1配線用導体膜EC1を形成し、CMP法により第1配線用導体膜EC1を第1配線用孔部H1に埋め込む。特に、上部バリア導体膜et1として、1〜5%の濃度で炭素を含ませるようにして、ルテニウムを主体とする導体膜を形成する。

(もっと読む)

81 - 100 / 558

[ Back to top ]