Fターム[5F033QQ58]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 基板 (558)

Fターム[5F033QQ58]に分類される特許

141 - 160 / 558

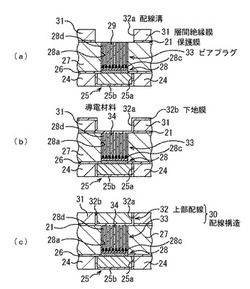

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

温度測定用基板及び熱処理温度測定方法

【課題】熱処理温度470℃〜530℃を測定する温度測定用基板及び熱処理温度測定方法を提供すること。

【解決手段】温度測定用基板は、リンが注入されたp型シリコン基板を備える。熱処理温度は、p型シリコン基板の層抵抗値から測定される。リンのドーズ量は、5×1014atom/cm2〜1×1015atom/cm2である。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

半導体装置

【課題】チャネル長を、トランジスタごとに自由に設計が可能な半導体装置を提供する。

【解決手段】複数の半導体柱2が立設された半導体基板1と、半導体柱2の外周面に設けられたゲート絶縁膜7と、半導体柱2の外周面を覆うゲート電極8と、半導体柱2の上側に設けられた第1不純物拡散領域3と、半導体柱2の下側に設けられた第2不純物拡散領域4と、を備え、第1不純物拡散領域3の厚さが半導体柱2ごとに異なっていることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することによって、ウエハW3のたわみを防いで、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つ。これにより、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間の接着剤51の未充填箇所の生成を防ぐ。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】表示デバイスに用いられる薄膜トランジスタ基板の配線構造において、Al合金膜と透明画素電極を直接コンタクトさせることができるとともに、薄膜トランジスタの製造プロセス中に用いられるアミン系剥離液に対する腐食性を改善できるAl合金膜を開発し、それを備えた表示デバイスを提供する。

【解決手段】Geを0.2〜2.0原子%、および元素群X(Ag、In、Sn、Ni、Co、Cu)より選択される少なくとも1種の元素を含むと共に、希土類元素と高融点金属群(Ti、Ta、V、Nb、Mo、W、Cr、Zr、Hf)からなる元素群Qより選択される少なくとも1種の元素を0.02〜1原子%含み、かつ、粒径が100nmを超える析出物が10−6cm2あたり1個以下であるところに特徴を有するAl合金膜と、該Al合金膜を備えた表示装置。

(もっと読む)

半導体装置の製造方法

【課題】ビア又は接着層とカルコゲナイド膜とのコンタクト性を確保しつつ、量産性を向上させることができる半導体装置及びその製造方法を提供すること。

【解決手段】層間絶縁膜3にビア2を形成する第1の工程と、層間絶縁膜3上のビア2の周囲の領域に接着層5を形成する第2の工程と、ビア2及び接着層5の表面にできた酸化物を、フッ化還元ガス雰囲気中に晒して還元する第3の工程と、ビア2及び接着層5の表面にできたフッ化物を、アンモニアガスを用いて除去する第4の工程と、ビア2及び接着層7を含む層間絶縁膜3上に、スパッタ法により相変化材料膜4を形成する第5の工程と、を含む。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

電気的固体装置の製造方法、電気的固体装置、および電気光学装置

【課題】ウエットエッチングを採用した場合でも、未エッチング部分を発生させずに微細なパターンを形成することができる電気的固体装置の製造方法、電気的固体装置、および電気光学装置を提供すること。

【解決手段】電気光学装置の素子基板上に、スリット7bを備えた透光性の画素電極7aを形成するにあたって、透光性導電膜7の上にレジストマスク96を形成した後、ウエットエッチングを行なう。レジストマスク96において、マスク開口部96bを挟むマスク線状部96eの側面部96fは斜め上向きのテーパ面になっている。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置に振幅の大きい信号が供給された場合においても正常に動作し、且つ信頼性の高い半導体装置を提供する。

【解決手段】半導体装置は、交流電圧を生成するアンテナ101と、交流電圧を整流し、内部電圧Vinを生成する整流回路102と、第1の保護回路107と、第2の保護回路108と、を有する。第1の保護回路107は、第1のダイオード201と、第2のダイオード202と、を有し、第2の保護回路は、容量素子203と、トランジスタ204と、を有する。第1の保護回路は、アンテナ101で生成される交流電圧の絶対値がある値よりも大きい場合に、その余剰分をカットし、第2の保護回路108は、整流回路102で生成された内部電圧Vinが大きい場合に機能し、共振周波数をずらすことにより、半導体装置に入力される信号を減少させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ビアホール下方でのスペーサ膜の閉塞を回避するとともに、ビアプラグの上方で隣接する配線層との間の余裕距離を確保することができる半導体装置を提供する。

【解決手段】シリコン基板1上に設けられた上面から下面まで貫通するコンタクトプラグ32を有する第1の層間絶縁膜30と、第1の層間絶縁膜30上に形成され、コンタクトプラグ32の形成位置に対応する位置の上面から下面まで貫通するビアホール41を有する第2の層間絶縁膜40と、ビアホール41内にコンタクトプラグ32と電気的に接触するように導電性材料が埋め込まれたビアプラグ43と、を備え、ビアホール41を形成する側壁は、第2の層間絶縁膜40の上面から下面に向かって、基板面に平行な方向の断面積が徐々に減少する順テーパ状を有し、ビアホールの上端部から所定の深さまでの側壁に、第2の層間絶縁膜40とは異なる絶縁性材料からなるスペーサ膜42が埋め込まれている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】繋ぎ露光において、マスクパターンの一端部を幅広に形成したマスクを使用しなくても、マスクの相対的な位置ずれに伴う配線抵抗の増大や配線信頼性の低下などの電気的な特性劣化を抑制する。

【解決手段】本発明の半導体装置は、半導体基板上で隣り合う第1の露光領域及び第2の露光領域のうち、第1の露光領域に第1の露光マスクを用いて形成された第1配線パターン101と、第1配線パターン101と繋ぎ合わせるための配線パターンとして、第1配線パターン101と同層でかつ第2の露光領域に第2の露光マスクを用いて形成された第2配線パターン102と、第1配線パターン101と第2配線パターン102との繋ぎ合わせ部分に形成されたビア103,104と、ビア103,104の間に形成された繋ぎパターン105とを備える。

(もっと読む)

半導体装置

【課題】チップ内における配線領域の占有面積の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】ゲート電極、ソース領域およびドレイン領域をそれぞれが有する第1および第2のトランジスタ121,122と、第1トランジスタ121のソースおよびドレイン領域の一方と第2トランジスタ122のソースおよびドレイン領域の一方と互いに連結する拡散領域150とを備える半導体装置110を採用する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】

DRAMの容量を安定化し、メモリセル部と周辺回路部の高低差を小さくして平坦化を容易にする。

【解決手段】

メモリセルトランジスタ上の第1の絶縁膜に第1のコンタクトプラグを埋め込み、エッチング特性の異なる第2、第3の絶縁膜を形成し、第3、第2の絶縁層を貫くコンタクト窓を形成し、シリンダ型蓄積電極を形成し、第2の絶縁膜をエッチングストッパとして第3の絶縁膜を除去し、キャパシタ絶縁膜、導電膜を形成し、パターニングして対向電極を形成し、対向電極に合わせて第2の絶縁膜も除去してメモリセルを形成し、周縁領域において第1の絶縁膜の上に導電膜、絶縁膜を形成し、第2のコンタクトプラグを埋め込む。第2の絶縁膜端部は、第2のコンタクトプラグに接しない。

(もっと読む)

141 - 160 / 558

[ Back to top ]