Fターム[5F033QQ58]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 基板 (558)

Fターム[5F033QQ58]に分類される特許

101 - 120 / 558

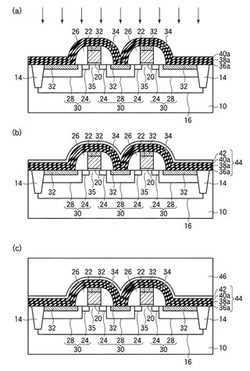

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

不揮発性半導体記憶装置及びディプレッション型MOSトランジスタ

【課題】トランジスタの耐圧を向上し、動作信頼性を向上出来る不揮発性半導体記憶装置及びディプレッション型MOSトランジスタを提供すること。

【解決手段】ゲート電極26と、第1不純物濃度を有するチャネル領域22と、第1不純物濃度よりも大きな第2不純物濃度を有するソース・ドレイン拡散領域21と、チャネル領域22とソース・ドレイン拡散領域21とが重複する領域に形成され、第2不純物濃度よりも大きな第3不純物濃度を有する重複領域24と、第2不純物濃度よりも大きな第4不純物濃度を有するコンタクト領域23と、ソース・ドレイン拡散領域21の一部領域内に形成され、第2不純物濃度よりも大きく且つ第4不純物濃度よりも小さい第5不純物濃度を有する不純物拡散領域27とを備え、不純物拡散領域27は、コンタクト領域23に接し且つ重複領域24に離隔するようにして形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプス現象およびゲートリーク電流を抑制することが可能な電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、基板10と、チャネル層11と、キャリア供給層12と、ソース電極21と、ドレイン電極22と、ゲート電極23と、ソース電極21とドレイン電極22との間でキャリア供給層12に積層されて電流コラプス現象を抑制する第1絶縁層31と、ドレイン電極22に対向する第1絶縁層31の端とドレイン電極22との間に形成された開口部40と、開口部40に露出したキャリア供給層12に積層された第2絶縁層32とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

小臨界次元のタングステン接点装置及び相互接続子の製法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

配線構造の製造方法、及び配線構造

【課題】製造コストが低い配線構造の製造方法、及び配線構造を提供する。

【解決手段】本発明に係る配線構造の製造方法は、基板10を準備する基板準備工程と、基板10上に半導体層を形成する半導体層形成工程と、半導体層上にドーパントを含むドーパント含有半導体層を形成するドーパント含有半導体層形成工程と、ドーパント含有半導体層の表面を、水分子を含ませた酸化性ガス雰囲気中で加熱することにより、ドーパント含有半導体層の表面に酸化層を形成する酸化層形成工程と、酸化層上に合金層を形成する合金層形成工程と、合金層上に配線層を形成する配線層形成工程とを備える。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

半導体装置

【課題】小型化・高耐圧化に優れ信頼性の高いパワー半導体装置を生産効率良くかつ高い製品歩留まりで製造できる誘電体分離型の半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板内のチップ配列領域において格子状のスクライブ領域によって区画された複数のチップ領域が整列配置され、前記複数のチップ領域の各々に半導体素子が形成された誘電体分離型の半導体装置であって、少なくとも前記複数のチップ領域の上には電極配線膜が厚さ0.8μm以上2.3μm以下で形成されており、前記電極配線膜の上に前記電極配線膜を保護するパシベーション膜が厚さ0.8μm以上2.7μm以下で形成されており、前記電極配線膜の厚さに対する前記パシベーション膜の厚さの比率が1.0以上1.2以下であることを特徴とする。

(もっと読む)

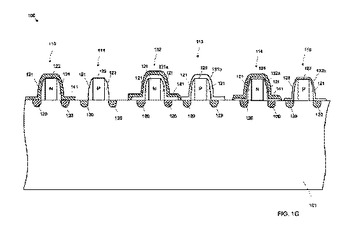

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】洗浄処理での腐食を抑えた高性能で高品質の半導体装置を提供する。

【解決手段】例えば、LCOSデバイスにおける画素電極90を形成する際、画素電極90の材料となる層に、間口の開口幅A1に対して底部の開口幅A2が狭い溝91を形成して、個々の画素電極90を形成した後、洗浄処理を行う。溝91の間口を広くすることで、洗浄処理時の液の滞留が抑えられ、画素電極90の腐食が抑えられるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増大を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散領域101aを表面に有する半導体基板100と、半導体基板100を覆う層間絶縁膜107と、層間絶縁膜107上に形成され、拡散領域109aを表面に有する半導体層108と、層間絶縁膜107および半導体層108を貫通する貫通口119a内に形成され、拡散領域101aに接し、且つ側面の一部が拡散領域109aに接するソース線プラグ116aと、ソース線プラグ116aと層間絶縁膜107との間に介在し、且つソース線プラグ116aが拡散領域109aと接する部分を除いてソース線プラグ116aと半導体層108との間に介在する側壁絶縁膜117aと、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

101 - 120 / 558

[ Back to top ]