Fターム[5F033QQ75]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | リフロー (248)

Fターム[5F033QQ75]に分類される特許

41 - 60 / 248

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】余分な工程を追加することなく、コンタクト抵抗の増加を抑制する半導体装置を提供する。

【解決手段】半導体装置の製造方法では、Cu配線上の第2層間絶縁膜内に設けたコンタクトホール内に第1のTi膜、TiN膜、第2のTi膜、第1のAl膜、及び第2のAl膜をこの順に形成する。第1のTi膜を成膜する際には、コンタクトホール底面上の第1の部分と第2層間絶縁膜上の第2の部分の膜厚の比(第1の部分)/(第2の部分)を0.05以下とする。また、第2のAl膜はアルミ・リフロー法を用いて形成し、この際に第2のTi膜及び第1のAl膜をアルミニウム・チタン合金膜とする。

(もっと読む)

半導体装置の製造方法

【課題】応力緩和機能を有するウェハレベルCSPと称される半導体装置において、外部電極の配置自由度が高い半導体装置の製造方法を提供する。

【解決手段】絶縁樹脂層を第1電極が形成された半導体ウェハ表面10に形成する工程、前記絶縁樹脂層の一部を除去して、開口径(D1)の開口部32を形成し、前記半導体ウェハ表面10の第1電極を露出させる工程、外部電極と前記第1電極を接続するための再配線層を前記絶縁樹脂層表面に形成する工程、前記再配線層の表面に再配線保護層を形成する工程、前記再配線保護層の一部を除去して、D2>D1となるような開口径(D2)の開口部32を形成し、前記第1電極と、前記外部電極を形成するための第2電極を露出させる工程、前記第1電極及び前記第2電極の表面にめっき層を形成する工程、前記めっき層を溶融することによって前記外部電極を形成する工程を含む、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】バリアメタル層を有する半導体装置を製造するに際し、パーティクルの発生を抑制可能な製造方法、及びこの製造方法を用いる半導体装置の製造装置を提供する。

【解決手段】

2つの金属層の間に金属化合物層が挟まれてなるバリアメタル層を有する半導体装置を製造するに際し、チタン及びタンタルのいずれか一方の金属元素から構成されるターゲットを希ガスの雰囲気でスパッタして、複数の金属層を下地配線上に積層する過程において最下層となる第1金属層に酸化処理を施す。次いで、最下層となる第1金属層の表面に第1金属酸化物層を形成した後に、層間において構成元素が異なるように、一つ以上の金属層を含む下地の表面に対して酸化処理、窒化処理、及び酸窒化処理のいずれかの処理を施す。こうした処理より第2金属化合物層を形成する。上記金属化合物層は、金属酸化物層の他、金属窒化物層や金属酸窒化物層であってもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】 銅からなる配線上に半田ボールが設けられた半導体装置において、半田ボール中の錫が配線に拡散するのをより一層抑制することができるようにする。

【解決手段】 配線7のランド上面には錫拡散抑制層12が設けられ、この錫拡散抑制層12上に半田ボール13が設けられている。この場合、錫拡散抑制層12は、銅含有率が高い非共晶組成の錫銅系鉛フリー半田によって形成され、リフロー時の加熱温度180℃以上280℃以下で溶融して固化した後同じ加熱温度180℃以上280℃以下で再溶融しないものからなっている。そして、この半導体装置が大きな電流を扱う電源IC等であっても、錫拡散抑制層12の存在により、半田ボール13中の錫が配線7に拡散するのをより一層抑制することができる。

(もっと読む)

電子デバイス及びその製造方法

【課題】接合熱処理温度が低くて済み、凝固後は高い融点を確保し得る高耐熱性の電子デバイス及びその製造方法を提供すること。

【解決手段】複数枚の基板WF1〜WFrのそれぞれは、縦導体31と、接続導体4とを有している。複数枚の基板WF1〜WFrのうち、隣接する基板WF1、WF2は、一方の基板WF2の接続導体(縦導体)31が、他方の基板WF1の接続導体4と、接合膜5によって接合されている。接合膜5は、第1金属または合金成分と、それよりも融点の高い第2金属または合金成分とを含み、凝固後の溶融温度が第1金属または合金成分の融点よりも高くなっている。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

パッケージおよびその製造方法

【課題】工程時間を短縮し、平坦度(又は、ボンディングの均一性)を高め、絶縁層(絶縁基板)とチップとの間の接着力が向上したパッケージおよびその製造方法を提供することを目的とする。

【解決手段】本発明のパッケージは、パターニング層上に形成された第1導電層と、前記パターニング層上に前記第1導電層を埋め込むように形成された絶縁層と、前記絶縁層の外面に形成された第2導電層と、前記第1導電層と第2導電層とを電気的に接続するように前記絶縁層の内部に形成された第3導電層とを含むことを特徴とする。

(もっと読む)

電極材料

【課題】溶融温度が低く、凝固後は高い融点を確保し得る導電性組成物を提供すること。

【解決手段】第1の金属粒子1は、平均粒径が、微細サイズ効果を生じ融点よりも低い温度で溶融可能なnm領域にある。第2の金属粒子2は、第1の金属粒子1の溶融により溶融する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上層の電極のコンタクトホール内でのカバレージを向上させること。

【解決手段】本発明の実施形態に係る半導体装置の製造方法において、第1エッチング工程で形成されるコンタクトホール300aの上部領域300Uaの中心部分からずれた位置に、第2エッチング工程で形成されるコンタクトホールの下部領域300Daが形成される。これにより、上部領域300Uaの下底部分に水平領域が存在し、その近くにおいては、第2電極30のオーバハング30hが生じにくくなり、カバレージが向上する。

(もっと読む)

電子デバイス用基板、電子デバイス用積層体、電子デバイス及びそれらの製造方法

【課題】TSV技術を適用して電子デバイスを製造に当たり、積層時位置合せを、簡単、かつ、確実に、しかも高精度で実行し得る製造方法、そのための基板、積層体及び電子デバイスを提供する。

【解決手段】複数枚rの基板WF1〜WFrを位置合せして積層するに当たり、外部から磁界Hを印加し、積層されて隣接する基板WF1〜WFrの磁性膜41−52の間に磁気的吸引力Fmを生じさせ、磁気的吸引力Fmにより、基板WF1〜WFrに設けられた縦導体3を位置合せする。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率層間絶縁膜と多層配線とを備える半導体装置において、低誘電率層間絶縁膜の表面が雰囲気に露出して吸湿するのを防止し、また、金属配線の界面及び低誘電率層間絶縁膜がコンタクトホール内に露出してオーバーエッチングされるのを防止することを目的とする。

【解決手段】水分の透過を防止しつつエッチングストッパとしても機能するエッチング防止膜14を低誘電率層間絶縁膜3の表面に形成し、更に、水分の透過を防止しつつエッチングストッパとしても機能するエッチング防止膜6を形成して、吸湿防止効果を有するエッチング防止膜を二重にする。

(もっと読む)

半導体装置

【課題】パッド電極が設けられる層間絶縁膜に低誘電率膜を用いた場合にも、該層間絶縁膜の破壊及び界面剥離を発生させず、高い接続信頼性を確保できるようにする。

【解決手段】半導体基板1の上方に、層間絶縁膜11、21等を介在させて形成された外部接続用電極を備えている。外部接続用電極は、上面を露出するパッドメタル層8と、該パッドメタル層8と半導体基板1との間に形成された第1のメタル層2と、層間絶縁膜21を貫通してパッドメタル層8と第1のメタル層2とを電気的に接続し、且つ、層間絶縁膜21に形成された少なくとも2つの第1のビア22とを有している。第1のビア22同士の最大の間隔bは、パッドメタル層8の幅寸法aよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】少ない工程数で樹脂コア及び樹脂保護膜を精度良く形成する。

【解決手段】電極パッド2が形成された基板(半導体基板1)上に、電極パッド2を露出させる開口3aを有する保護絶縁膜3を形成した後、感光性樹脂膜4を形成する。感光性樹脂膜4を多階調マスク5を用いて露光した後で現像する。この現像により、感光性樹脂膜4により構成される樹脂保護膜7と、樹脂保護膜7よりも厚膜の感光性樹脂膜4のパターンにより構成される樹脂コア6と、を一度に形成する。次に、樹脂コア6上から電極パッド2上に亘って配線8を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁層を貫通する導電性突起体と半導体素子の電極部とが電気的に接続された半導体装置において接続信頼性を向上させる。

【解決手段】半導体素子101の一面上に電極部102が配置されている。電極部102を除いて半導体素子101の一面を覆うように絶縁層107が形成されている。電極部102と電気的に接続する導電性突起体103を有する配線105が絶縁層107上に形成されている。導電性突起体103と電極部102との間に、錫及び銅を含む合金層104が介在している。

(もっと読む)

半導体装置の製造方法及びマスク

【課題】樹脂製のバンプコアの上に導電膜を形成したバンプを有する半導体装置の歩留まりを高くしつつ、バンプピッチを狭くする。

【解決手段】保護絶縁膜120上に感光性樹脂膜210を形成する。次いで、感光性樹脂膜210を露光及び現像することにより、保護絶縁膜120上に、第1の直線に沿って複数のバンプコアを形成する。次いで、複数のバンプコア上、複数の電極パッド130上、及び保護絶縁膜120上に導電膜を選択的に形成することにより、複数のバンプ、及び複数のバンプそれぞれをいずれかの電極パッド130に接続する複数の配線を形成する。そして複数のバンプコアを形成する工程において、多階調マスク50を使用して感光性樹脂膜210を1回のみ露光することにより、バンプコアの側面のうち配線に面する領域を、第1の直線と交わる領域より傾斜を緩やかにする。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板と、半導体基板の第1面側に形成された半導体素子と、半導体基板の第1面側に形成されて半導体素子と電気的に接続された配線を有する配線層と、半導体基板の第1面側に形成された電極パッド部と、半導体基板の第1面からその反対側の第2面まで貫通する貫通孔内に形成された貫通電極とを備え、前記電極パッド部は、半導体基板の第1面に部分的に積層された単一導電層と、単一導電層に積層された混成導電層とを有し、前記単一導電層は、貫通電極と電気的に接続する導電領域部からなり、前記混成導電層は、単一導電層と前記配線とを電気的に接続する導電領域部と、単一導電層と配線とを電気的に絶縁する絶縁領域部とが混成されてなる半導体装置。

(もっと読む)

金属充填装置

【課題】凹面化、空隙、ボイドなどを生じることなく、対象物の微細空間を金属充填材によって満たし、低コスト化と処理効率の向上とを実現しうる金属充填装置を提供すること。

【解決手段】金属充填装置は、微細空間の開口面の一つが開放された状態で、その開口面の反対側から対象物2を支持する第1の支持体10と、前記開口面側から第1の支持体10と接合して、対象物2を処理室A内に封入する第2の支持体11と、処理室Aに溶融金属Mを供給する溶融金属供給部12と、処理室A内の圧力を制御する圧力制御部13とを備えており、微細空間内に溶融金属Mが充填された後、その溶融金属が冷却により硬化するまで、処理室Aに圧力を与える加圧手段を有する。

(もっと読む)

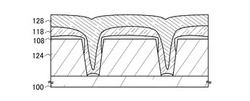

半導体装置の製造方法

【課題】ポリシリコン・ゲート電極作成のためのエッチング処理時に、クランプによって覆われていたポリサイド層上の層間絶縁膜の膜剥がれが起こりにくい半導体装置の製造方法を提供する。

【解決手段】半導体基板110上に、ポリシリコン膜220及びタングステン・シリサイド膜210をこの順に積層してポリサイド・ゲート電極230を形成する。ポリサイド・ゲート電極230を含む半導体基板110上に、B濃度が高濃度の下層BPSG膜140を第1の成膜速度v1で形成する。下層BPSG膜140の上に、B濃度が下層BPSG膜140より低い低濃度の上層BPSG膜120を第2の成膜速度v2で形成する。第2の成膜速度は前記第1の成膜速度未満である。

(もっと読む)

41 - 60 / 248

[ Back to top ]