Fターム[5F033QQ75]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | リフロー (248)

Fターム[5F033QQ75]に分類される特許

81 - 100 / 248

半導体装置及びその製造方法

【課題】Cuを主体とする配線について、配線抵抗を低く維持するとともに、ストレスマイグレーション耐性及びエレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜28、30と、層間絶縁膜28、30に形成されたビアホール34及び配線溝36内に形成され、Ta膜より成るバリアメタル膜38と、バリアメタル膜38上に形成されたTi膜40と、バリアメタル膜38及びTi膜40が形成されたビアホール34及び配線溝36内にそれぞれ埋め込まれ、Cuより成る導体プラグ44及び配線46とを有し、Ti膜40の膜厚が、配線溝36の底部において4nm以下になっている。

(もっと読む)

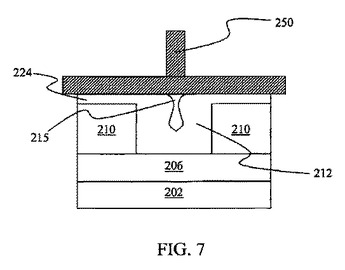

配線の作製方法及び表示装置の作製方法

【課題】配線の凹凸やコンタクト不良を大幅に低減した配線の作製方法を用いることによって半導体装置の信頼性を向上させること。

【解決手段】層間絶縁膜207に設けられた開口部に液滴吐出法を用いてノズル208から導電性組成物が分散された液滴209を滴下し配線210を形成する。さらに、加熱処理を行うことで配線210をリフローする。これにより、配線表面を平坦化し、且つ配線のコンタクト不良を改善することができる。

(もっと読む)

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

半導体装置及びその製造方法

【課題】細く深いバイアホールが設けられる場合でも、ソースインダクタンスを十分に低減し、高い放熱効率を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】SiC基板1上に化合物半導体領域2を形成し、その後、化合物半導体領域2上にゲート電極4g、ソース電極4s及びドレイン電極4dを形成し、更に、化合物半導体領域2上にソース電極4sに接続されるAu膜10を形成する。次に、SiC基板1の裏面にレーザビームを照射して、SiC基板1、化合物半導体領域2及びAu層を貫通するバイアホール21を形成する。次に、バイアホール21の側面及びSiC基板1の裏面にわたってビア配線14を形成する。次に、バイアホール21内に溶融金属滴32を充填し凝固させることにより、導通ビアを形成する。そして、溶融金属滴32を充填する際に、SiC基板1を溶融金属滴32に対して相対的に振動させる。

(もっと読む)

半導体装置

【課題】ダイシング時及びボンディング時においても活性領域への水分等の不純物の侵入を防止し、小型化を容易におこなうことができる半導体装置を提供することを目的とする。

【解決手段】

半導体素子と外部接続端子とを接続する配線が貫通する開口部を含み、前記半導体素子を含む半導体層上に設けられた絶縁膜内に延在して前記半導体素子の全体を囲み、かつ前記外部接続端子の内側に配置された筒状ダミー配線を有する。

(もっと読む)

回路基板、電子デバイス及びそれらの製造方法

【課題】回路パターンの表面における酸化膜、及び、貫通孔内におけるボイドの発生を抑制した回路基板、電子デバイス及びそれらの製造方法を提供すること。

【解決手段】回路パターン2は、基板1の厚み方向の一面に設けられている。貫通電極3は、基板1に設けられた貫通孔30の内部に充填され、一端が回路パターン2に接合されている。回路パターン2及び貫通電極3は、それぞれ、貴金属成分(Au成分)を含有する領域AL1、AL2を有し、領域AL1、AL2によって互いに接合されている。

(もっと読む)

半導体装置、電気光学装置及び電子機器

【課題】基板上の受動素子を用いてインピーダンス制御を行うために、高精度の抵抗部を容易に形成する。

【解決手段】半導体装置121の能動面121aの周縁部には、複数の電極パッド24が配列形成され、半導体装置121の能動面全体に保護膜としてのパッシベーション膜26が形成されており、上述した各電極パッド24の表面に、パッシベーション膜26の開口部26aが形成されている。パッシベーション膜26上には、応力緩和性の高い有機樹脂膜が形成される。そのパッシベーション膜26の表面であって、電極パッド列24aの内側には、樹脂突起12が形成されている。樹脂突起12は、半導体装置121の能動面121aから突出して形成され、略同一高さで直線状に延在しており、電極パッド列24aと平行に配設されている。

(もっと読む)

パターン配列シート、その製造方法、電子デバイスチップ及びその製造方法

【課題】簡単な原理、構造による新規なパターン配線シート、その製造方法、電子デバイスチップ及びその製造方法を提供する。

【解決手段】パターン配線シートあるいは電子デバイスチップは、紙、樹脂等、あるいは両者のハイブリッド材料である台紙基材上に粘着層を介して設けられた可撓性シート基材の表面に、インクジェッド原理の噴射ヘッドを使用して、電気的機能発現材料により形成される電気機能発現材料層を形成するので、新規なパターン配線シートあるいは電子デバイスチップを実現することが可能となる。

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】データ読み書きの繰り返しによるVthの変動を抑制する。

【解決手段】本発明の半導体装置は、第1の層間絶縁膜1中に形成された下層配線2を備え、第1の層間絶縁膜1と下層配線2の上に形成された絶縁膜3を備え、絶縁膜3の上に形成された第2の層間絶縁膜4を備え、第2の層間絶縁膜4の上に形成され下層配線2にビアホール6を介して接続されたAl製の上層配線5を備え、上層配線5の上面および側面に形成されたアルミナ膜8を備え、上層配線5の上に形成された第3の層間絶縁膜9を備えたものである。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体基板のストリートに合金層を形成すること無く、しかもバリア層の横方向エッチングであるサイドエッチング量が少ない半導体装置および半導体装置の製造方法を提供する。

【解決手段】 半導体装置の入出力端子となる電極パッド2と、電極パッド2上に順次設けるバリア層および共通電極層6と、この共通電極層6上に設ける突起電極11を有する半導体装置において、バリア層は、2層からなるとともに、突起電極11材料または共通電極層6材料と電極パッド2材料とが相互に拡散することを抑制する材料からなり、共通電極層6側の第2のバリア層5は、電極パッド2側の第1のバリア層4より膜厚が薄い半導体装置およびその製造方法により、第2のバリア層5のサイドエッチング量を少なくすることが可能となり、さらに半導体基板のストリートに合金層が形成されることはない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】信頼性を低下することなく高集積化が可能な半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】半導体装置は、コンタクト層40及びAl層の真上にAl層を積層したAlスタック構造をなすものであり、コンタクト層40の真上に1stAl層10が積層され、1stAl層10の真上に2ndAl層20が積層され、2ndAl層20の真上に3rdAl層30が積層されてなるものである。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールの深さに大きな差が存在するような場合であっても、焦点深度の不足の問題を回避してコンタクトホールを確実に高い精度で形成して、それぞれの導電領域にコンタクトする多層配線構造を確実に歩留まり良く形成する。

【解決手段】メモリセル領域10Aにおいては一対のゲート構造間に形成された拡散領域171AとBPSG膜182に形成された配線パターン222との間の電気接続のため、予めポリシリコンプラグ191を、ゲート電極142に自己整合した状態で形成しておく。一方、周辺回路領域10BにおいてはBPSG膜181に、ゲート電極142及び前記拡散領域171Bと、BPSG膜182に形成された配線パターン222との間の電気的接続のため、コンタクトプラグ212を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】アルミニウムを主成分とするパッドに導電性ボールを容易に接合できる構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11に形成された半導体素子を外部に電気的に接続するためのアルミニウムを主成分とするパッド12と、アルミニウムを主成分とするパッド12上に形成された焼結導電層13と、焼結導電層13上に溶着された導電性ボール14と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造が容易であり、貫通金属と半田との接合強度が大きい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明は、基板12と、基板12を貫通し、基板12の表面に設けられた電極部16に接し、基板12の裏面側から凹部30が設けられている貫通金属32と、凹部30に埋め込まれるように、基板12裏面側の貫通金属32の露出面に設けられた半田34からなる導電材と、を具備する半導体装置及びその製造方法である。

(もっと読む)

液晶表示装置及びその製造方法

【課題】データ線から発生する電気力線が画素電極に進入することを防止し、開口率を大きくすることができる液晶表示装置を提供する。

【解決手段】第1基板100Aは、データ線12を覆う無機絶縁膜15と、データ線12の上方において無機絶縁膜15上に設けられた突起状の有機絶縁膜21と、有機絶縁膜21を覆い、かつ、上方から見たときにデータ線12を覆うシールド共通電極26と、を有する。

(もっと読む)

導電体およびその製造方法

【課題】導電性および柔軟性の高い導電体及びその製造法の提供。

【解決手段】導電体100は、金属および導電性金属酸化物の少なくとも一方を含む第1導電層10と、第1導電層10の表面の少なくとも一部を覆う第2導電層20と、を有し、第2導電層20は、導電性高分子を含む。導電体100の製造方法は、凹凸パターンを有する版の凸部に、被転写層を形成する工程と、前記被転写層を基板に転写する工程と、を有し、前記被転写層を形成する工程は、前記版の凸部の上に導電性高分子を含む第1前駆体層を形成する工程と、前記第1前駆体層の上に、金属の前駆体および導電性金属酸化物の前駆体の少なくとも一方を含む第2前駆体層を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置は、n型領域を有するシリコン基板と、前記n型領域上に、窒素を含む酸化シリコンを用いて形成されたゲート絶縁膜と、ホウ素を含むシリコンを用いて、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極両側の前記シリコン基板内に形成されたp型ソース/ドレイン領域と、酸化シリコンを用いて、前記ゲート電極の側壁上に形成されたサイドウォールスペーサと、前記ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜と、前記層間絶縁膜の平坦化された表面から内部に向って形成された配線用凹部と、前記凹部を埋める、下地のバリア層とその上の銅領域を含む銅配線と、前記銅配線を覆って、前記層間絶縁膜上に形成された炭化シリコン層と、を有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】デバッグ等のために、完成した半導体集積回路装置の配線をFIB加工を用いて事後的に修正する場合がある。修正配線は配線として最適に材料を使用すべきである。しかし、たとえば、比抵抗の低い金属は、比較的その後の検査・試験環境に弱い等の問題がある。

【解決手段】本願発明は、ほぼ完成した半導体集積回路装置の配線を変更するために、FIB加工を用いて半導体集積回路チップの配線を修正するに当たり、半導体集積回路チップの主面上の絶縁膜に金属修正配線をFIBCVDにより形成後、その上を覆うように、金属修正配線よりも耐酸化性または耐腐食性の高い金属被覆膜を、FIBCVDにより形成するものである。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置は、n型領域を有するシリコン基板と、前記n型領域上に、窒素を含む酸化シリコンを用いて形成されたゲート絶縁膜と、ホウ素を含むシリコンを用いて、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極両側の前記シリコン基板内に形成されたp型ソース/ドレイン領域と、酸化シリコンを用いて、前記ゲート電極の側壁上に形成されたサイドウォールスペーサと、前記ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜と、前記層間絶縁膜の平坦化された表面から内部に向って形成された配線用凹部と、前記凹部を埋める、下地のバリア層とその上の銅領域を含む銅配線と、前記銅配線を覆って、前記層間絶縁膜上に形成された炭化シリコン層と、を有する。

(もっと読む)

81 - 100 / 248

[ Back to top ]