Fターム[5F033QQ94]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803) | 除去対象 (877) | 酸化物、酸化膜 (480)

Fターム[5F033QQ94]に分類される特許

21 - 40 / 480

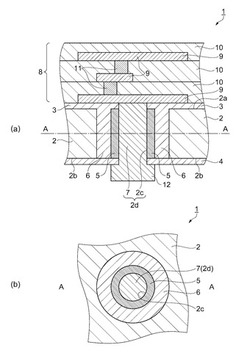

配線基板、赤外線センサー及び貫通電極形成方法

【課題】貫通電極を生産性良く形成できる貫通電極の構造を提供する。

【解決手段】配線基板1は、第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、ビアホール2cの面に設置され基板2と同じ材質のシード膜5と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3とシード膜5を囲む場所とに設置され熱酸化膜を含む第3絶縁膜6と、ビアホール2c内でシード膜5に囲まれた導電体7と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】信号速度の遅延を防止することができる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】金属窒化膜に隣接する他の膜の特性を劣化させない温度範囲において、金属窒化膜中の塩素原子や酸素原子の残留量を低減し、金属窒化膜の耐酸化性を改善する。

【解決手段】自然酸化膜が形成され、塩素原子を含む窒化チタニウム膜が形成された基板を処理室内に搬入して基板支持部により支持する工程と、基板を基板支持部により加熱する工程と、窒素原子含有ガス及び水素原子含有ガスをガス供給部により処理室内に供給しつつ、処理室内をガス排気部により排気する工程と、処理室内に供給された窒素原子含有ガス及び水素原子含有ガスをプラズマ生成部により励起する工程と、を有する。

(もっと読む)

銅結線のシード層の処理方法および処理装置

【課題】ダマシンプロセスによる銅の充填において、銅シード層の完全性を失わないように行う。

【解決手段】誘電体層に半導体結線形状を形成するための方法は、誘電体層上に形成された形成されたバリア層上、および誘電体層のエッチング形状内に、銅シード層を蒸着する工程を含む。次いで、銅シード層は、酸化された層を銅シード層から除去するために処理を施される。次いで、その方法は、処理された銅シード層上に銅充填層を電気メッキする工程に進む。銅充填層は、誘電体層のエッチング形状を満たすよう構成されている。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得る。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

(もっと読む)

半導体装置の製造方法

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

ラジカルクリーニング方法及びラジカルクリーニング装置

【課題】Si基板上に形成されたSiO2膜を除去するラジカルクリーニング方法であって、ラジカルクリーニングを行う際に生成する残留生成物も除去することができるラジカルクリーニング方法を提供する。

【解決手段】プラズマによりHラジカル生成用ガスを分解してHラジカルを生成させ、このHラジカルとNF3ガスを反応させてN、F及びHからなるラジカルを生成するNFHラジカル生成工程と、真空槽内で、Si基板上に形成されたSiO2膜に前記N、F及びHからなるラジカルを照射することにより前記SiO2膜を除去するエッチング工程と、真空槽内で、前記エッチング工程で前記Si基板上に生成した残留生成物にマイクロ波を照射することにより、前記残留生成物を加熱して蒸発させて除去する残留生成物除去工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

21 - 40 / 480

[ Back to top ]