Fターム[5F033RR27]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 感光性を有するもの (362)

Fターム[5F033RR27]に分類される特許

61 - 80 / 362

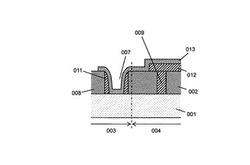

半導体装置およびその製造方法

【課題】 ダイシングに伴う膜剥れの防止および異常放電防止に好適な半導体装置を提供する。

【解決手段】 半導体装置はスクライブ領域003とIC領域004からなり、スクライブ領域003の層間絶縁膜002には少なくとも一つの分離溝007が設けられ、分離溝007の両側の側壁にはプラグ金属膜からなるサイドウォール011が形成され、少なくともサイドウォールを覆うパッシベーション膜を設ける構成とした半導体装置とする。

(もっと読む)

液晶表示装置および電子機器

【課題】有機膜が剥離することに起因して、電極が腐食するのを抑制することが可能な液晶表示装置を提供する。

【解決手段】この液晶表示装置100は、基板1と、基板1の表面上に形成される薄膜トランジスタ16と、薄膜トランジスタ16の表面を覆うように形成される平坦化膜17と、平坦化膜17の側端面の下端部17bと平坦化膜17が設けられるゲート絶縁膜12の上面との境界領域を少なくとも覆うように設けられる導電層19と、導電層19の基板1の端部側の端部とゲート絶縁膜12の上面との境界領域を少なくとも覆うように設けられる低温パッシベーション膜20aとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のバンプが十分な反発力と十分な密着性とを兼ね備えるようにし、バンプの接続性を向上させる。

【解決手段】半導体装置100は、電極パッド2と、電極パッド2を露出させる開口3aが形成された保護絶縁膜3を有する。更に、保護絶縁膜3上に形成されたバンプコア(樹脂コア4)と、バンプコア上に形成された導電層5aと、を含むバンプ(樹脂コアバンプ6)を有する。更に、導電層5aと電極パッド2とを接続する配線5bを有する。バンプコアは、互いに弾性率が異なる複数の樹脂層(例えば、第1及び第2樹脂層11、12)の積層構造を有する。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することを課題とする。

【解決手段】基板1上に第1絶縁層2を形成する工程と、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する工程と、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう金属膜5を形成する工程と、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する工程と、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6及び金属膜5の一部を除去する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の良好な半導体装置及びその製造方法を提供することにある。

【解決手段】一方の主面に於ける半導体素子領域2内に複数の機能素子が配設された半導体基板1と、半導体基板1の一方の主面上に配設され、複数の配線層3と複数の絶縁層4とを含む多層配線層2と、多層配線層2上に形成された第1の有機絶縁物層6と、第1の有機絶縁物層上に形成され、配線層に電気的に接続された他の配線層と、第1の有機絶縁物層6上に、他の配線層を覆うように形成された第2の有機絶縁物層10とを具備し、半導体素子領域を囲む半導体基板領域に、多層配線層を貫く溝が半導体素子領域を囲繞して配設されており、溝内には、前記有機絶縁物層6、有機絶縁物層10のいずれからも分離された有機絶縁物が配設されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面とを有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記貫通孔の内壁に設けられ、平面視において前記貫通孔と重なる位置に接続孔を有する樹脂膜と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に第1凹部を有する配線層と、前記配線層に接続され、前記第1凹部内と前記樹脂膜を介して前記貫通孔内とに設けられた貫通電極とを含む半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面を有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に凹部を有する配線層と、前記貫通孔と前記凹部とで構成される溝の内壁および前記溝の底面に設けられ、且つ、平面視において前記配線層の前記凹部と重なる接続孔を有する樹脂膜と、前記配線層に接続され、前記樹脂膜を介して前記溝内に設けられた貫通電極とを含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パッケージ端部の樹脂層の一部が剥離し、耐湿性が悪化するという問題があった。

【解決手段】本発明の半導体装置では、シリコン基板2の一主面側に再配線層5、5Aと剥離防止層6が配置され、それらを被覆するように樹脂層3が形成される。剥離防止層6は、再配線層5、5Aの無配置領域であり、半導体装置1の外周端部近傍に配置されることで、樹脂層3の樹脂量が低減される。この構造により、樹脂層3の熱収縮力に起因する樹脂の反り上がりが防止し、樹脂層3が、シリコン基板2上から剥離することが防止され、半導体装置1の耐湿性が向上される。

(もっと読む)

半導体装置及びその製造方法

【課題】配線及び半導体素子等を自由に配置できない領域を減少させる。

【解決手段】半導体装置は、半導体素子3が形成されている第1面及び第1面とは反対側の第2面を有する半導体基板1と、半導体基板1の上に形成され、且つ、第1のビア7を有する層間絶縁膜と、半導体基板1内に形成され、且つ、第1のビア7と接続する第2のビア13とを有し、第1のビア7の径は、第2のビア13の径よりも小さいことを特徴とする。

(もっと読む)

伝送線路および高周波デバイス

【課題】層間膜としてコンポジット膜を用いた伝送線路において伝送損失を低減するための技術を提供する。

【解決手段】接地導体膜301、層間膜310、および配線303をこの順に積層してなる伝送線路300であって、層間膜310は、第1の材料からなる粒子302Aが絶縁材料302Bに分散されてなるコンポジット膜302を含み、層間膜310の配線303側の表面からの粒子302Aの平均直径の深さまでの範囲における粒子302Aの密度が、層間膜310のそれ以外の範囲における粒子302Aの密度よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】少ない工程数で樹脂コア及び樹脂保護膜を精度良く形成する。

【解決手段】電極パッド2が形成された基板(半導体基板1)上に、電極パッド2を露出させる開口3aを有する保護絶縁膜3を形成した後、感光性樹脂膜4を形成する。感光性樹脂膜4を多階調マスク5を用いて露光した後で現像する。この現像により、感光性樹脂膜4により構成される樹脂保護膜7と、樹脂保護膜7よりも厚膜の感光性樹脂膜4のパターンにより構成される樹脂コア6と、を一度に形成する。次に、樹脂コア6上から電極パッド2上に亘って配線8を形成する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

積層チップパッケージの製造方法

【課題】積層チップパッケージを、低コストで短時間に大量生産する。

【解決手段】積層チップパッケージは、本体と、本体の少なくとも1つの側面に配置された配線を備えている。本体は、積層された複数の階層部分を含むと共に上面と下面を有する主要部分と、主要部分の上面と下面の少なくとも一方に配置されて配線に電気的に接続された複数の端子を有している。積層チップパッケージの製造方法では、それぞれ配列された複数の分離前本体2Pを含む複数の第1の積層基礎構造物を作製し、複数の第1の積層基礎構造物を積層して第2の積層基礎構造物を作製し、第2の積層基礎構造物を切断することによって、分離前本体2Pが2つの方向にそれぞれ複数個ずつ並んだブロック121を形成し、ブロック121に含まれる複数の分離前本体2Pに対して一括して配線を形成し、複数の分離前本体2Pを互いに分離する。

(もっと読む)

再配線構造を有する半導体素子とパッケージ、及びその製造方法

【課題】再配線構造を有する半導体素子とパッケージ、及びその製造方法を提供すること。

【解決手段】チップ基板上にチップパッドを形成し、上記チップパッド及び上記チップ基板上にパシベーション層を形成し、上記パシベーション層上に第1絶縁層を形成し、上記第1絶縁層内にリセスと第1開口を形成し、上記パシベーション層内に上記第1開口と垂直に整列された第2開口を形成し、上記リセス、上記第1開口、及び上記第2開口内に再配線ラインを形成し、上記再配線ラインと上記第1絶縁層上に第2絶縁層を形成し、及び上記第2絶縁層内に再配線パッドとして上記再配線ラインの一部を露出させる開口を形成することを含む半導体素子及び半導体素子の製造方法を提供する。

(もっと読む)

銅プラグを有する半導体デバイスおよびデバイスを形成するための方法

【課題】絶縁層がデバイスの最終配線層と接触する銅プラグを有する、半導体デバイスを提供する。

【解決手段】銅プラグと絶縁層とを分離する障壁層も存在可能である。他の実施形態では、絶縁層と銅プラグとの間にアルミニウム層も存在可能である。半導体デバイスを生成するためのプロセスも開示される。

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

薄膜トランジスタ

【課題】信頼性が高く、耐酸化性に優れる薄膜トランジスタを提供すること。

【解決手段】基板2上に、ゲート電極3、ゲート絶縁層4、半導体層5、ソース電極6およびドレイン電極7を形成してなる薄膜トランジスタであって、アルカリ可溶性フェノール樹脂(A)と感放射線化合物(B)とを含有する感放射線性樹脂組成物からなる保護膜8が、前記ゲート絶縁層4、前記半導体層5、前記ソース電極お6よび前記ドレイン電極7に接触して形成されていることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

61 - 80 / 362

[ Back to top ]