Fターム[5F033RR27]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 感光性を有するもの (362)

Fターム[5F033RR27]に分類される特許

41 - 60 / 362

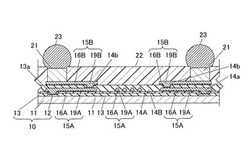

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ボンディングパッドの特性の劣化を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、LSI基板1上に形成された第1の金属を含む再配線層8a、bおよび前記LSI基板上に形成されたボンディングパッドとなる第2の金属を含むパッド電極22を被覆するように、層間膜10を形成する。前記層間膜のうち、前記再配線層に接続されるマイクロバンプを形成する領域およびボンディングワイヤが接続される領域に対応する部分を感光させ、アルカリ水溶液を含む第1のアルカリ現像液で現像することにより、前記再配線層が露出するように前記層間膜に第1の開口部10aを形成するとともに、前記パッド電極が露出するように前記層間膜に第2の開口部10bを形成する。さらに、テトラメチルアンモニウムヒドロキシドおよび多価アルコールを含む第2のアルカリ現像液で、前記層間膜の残りの露光された部分を現像する。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。上面が開口した枠体を、トランジスタの周囲を取り囲んで、半導体基板の上面上に形成する。枠体上にテープを貼り付けることにより、枠体及びテープによってトランジスタ及び配線を覆う。

(もっと読む)

半導体装置及びその製造方法

【課題】プローブの先端が電極パッドから外れてしまうことによる測定不良を十分に抑制する。

【解決手段】半導体装置(例えば、半導体ウェハ200)は、複数層の配線層と、相互に隣り合う配線層の間に介在する層間絶縁膜と、を含む多層配線層90を有する。更に、多層配線層90上に形成された無機絶縁膜(例えば、酸化膜4と酸化窒化膜5との積層膜)と、無機絶縁膜上に形成された有機絶縁膜6とを有する。更に、多層配線層90の複数層の配線層のうち、最上層でない配線層(例えば、最下層の配線層)に形成された電極パッド40と、有機絶縁膜6、無機絶縁膜、及び、多層配線層90において、電極パッド40上に位置する部位に形成された開口41と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】貫通ビアを形成する工程の効率化を図り、製造コストの抑制を図ることのできる半導体記憶装置を提供すること。

【解決手段】実施の形態の半導体装置1は、半導体基板11と、第1絶縁層20と、電極パッド14と、貫通孔21と、支持絶縁層12と、を備える。半導体基板は、配線層が設けられるとともに上下に貫通する貫通溝が形成される。第1絶縁層は、貫通溝に充填される。電極パッドは、配線層に含まれる配線と一体的に形成される。貫通孔は、電極パッドと第1絶縁層の間に設けられて電極パッドを支持する。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

貫通配線基板および製造方法

【課題】ボイドが生じた貫通配線基板で気密性を保つ。

【解決手段】貫通ビアが設けられた貫通配線基板であって、貫通孔が設けられた基板と、貫通孔に充填された導電体の貫通ビアと、貫通ビアと貫通孔の間のボイドに充填された樹脂を備える貫通配線基板および製造方法を提供する。基板は、ガラス基板であってよい。樹脂は、ポリイミドであってよい。また、樹脂は、ポリマーであってもよい。また、樹脂は、光に反応して固体に変化する光硬化樹脂であってもよい。

(もっと読む)

貫通配線基板および製造方法

【課題】ボイドを生じさせない貫通ビアを設けた貫通配線基板。

【解決手段】貫通ビアが設けられた貫通配線基板であって、貫通孔が形成された基板と、貫通孔内に設けられ、基板の上面と下面の間を電気的に接続する導電体と、導電体と貫通孔の間の隙間に充填された樹脂と、を備える貫通配線基板および製造方法を提供する。基板は、ガラス基板であってよい。樹脂は、ポリイミドであってよい。樹脂は、ポリマーであってもよい。樹脂は、光に反応して固体に変化する光硬化樹脂であってもよい。

(もっと読む)

微細空間への絶縁物充填方法

【課題】半導体基板に設けられた微細空間内に、充填不全などを回避して、絶縁物を確実に充填しえる方法を提供すること。

【解決手段】 半導体基板2に設けられた微細空間21内に絶縁物を充填するにあたり、微細空間21の開口する半導体基板2の一面側から、微細空間21内に流動性絶縁物4を充填する。そして、流動性絶縁物4を、加圧したままで、硬化させる。

(もっと読む)

電子デバイス及びその製造方法

【課題】高性能及び高機能で、高周波特性に優れ、コストダウンに有効な絶縁構造を持つ電子デバイス及びその製造方法を提供する。

【解決手段】半導体基板1は、その厚み方向に伸びる縦孔30を有している。絶縁物充填層3は、縦孔30内にその内周面を覆うように充填してなる環状層である。縦導体2は、絶縁物充填層3によって囲まれた領域20内に充填された凝固金属体でなる。絶縁充填層3は、有機絶縁物又はガラスを主成分とする無機絶縁物と、ナノコンポジット構造のセラミックとを有する層である。ナノコンポジット構造のセラミックは、常温比抵抗が1014Ω・cmを超え、比誘電率が4〜9の範囲にある。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、製造コストの増加を抑制可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板部10、誘電体膜22、再配線24、上部電極25、絶縁膜26、及び外部接続端子28を有する。半導体基板部10は、回路が形成され、回路にそれぞれ接続される下部電極15、上部電極パッド16、接続パッド17、18を上面に有する。誘電体膜22は、下部電極15を被い、上部電極パッド16、接続パッド17、18の上面に達する開口部を有する。再配線24は、一部の接続パッド17、18に電気的に接続される。上部電極25は、誘電体膜22を介して下部電極15の上面に対向して配置され、上部電極パッド16に接続され、再配線24を含む。絶縁膜26は、誘電体膜22、再配線24、及び上部電極25を被う。外部接続端子28は、絶縁膜26を貫通し再配線24に接続され、絶縁膜26の上面から露出する。

(もっと読む)

配線回路基板及びその製造方法

【課題】配線回路基板において、コンタクト抵抗の上昇を抑制し、熱応力による断線を防止することのできるコンタクト構造を提供する。

【解決手段】 配線回路基板は、第1配線層(5)、第2配線層(7)、及び前記第1配線層と前記第2配線層を電気的に接続するコンタクト配線(6)を有する。前記コンタクト配線は、前記第1配線層のコンタクト面を被覆する第1被覆部(6a)と、前記第2配線層のコンタクト面を被覆する第2被覆部(6c)と、前記第1被覆部と前記第2被覆部の間に延びるプラグ部(6b)を有する。前記第1被覆部、前記プラグ部、及び前記第2被覆部は、同一の導電性材料で一体的に形成された内部に界面のないコンタクト配線である。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、下層配線としてCu配線を含む多層配線と、前記Cu配線を形成するために用いられるCuアクセサリとが形成された半導体基板を、ポリイミド膜で覆う工程と、前記多層配線の最上層配線の表面および前記Cuアクセサリの表面を露出させる工程と、前記半導体基板をCu腐食防止剤の蒸気にさらして、前記最上層配線の表面および前記Cuアクセサリの表面にCu腐食防止膜を形成する工程と、前記最上層配線の表面に形成されたCu腐食防止膜を選択的に除去する工程と、前記Cuアクセサリの表面にCu腐食防止膜が形成された状態で、前記ポリイミド膜をベーク処理する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】応力緩和機能を有するウェハレベルCSPと称される半導体装置において、外部電極の配置自由度が高い半導体装置の製造方法を提供する。

【解決手段】絶縁樹脂層を第1電極が形成された半導体ウェハ表面10に形成する工程、前記絶縁樹脂層の一部を除去して、開口径(D1)の開口部32を形成し、前記半導体ウェハ表面10の第1電極を露出させる工程、外部電極と前記第1電極を接続するための再配線層を前記絶縁樹脂層表面に形成する工程、前記再配線層の表面に再配線保護層を形成する工程、前記再配線保護層の一部を除去して、D2>D1となるような開口径(D2)の開口部32を形成し、前記第1電極と、前記外部電極を形成するための第2電極を露出させる工程、前記第1電極及び前記第2電極の表面にめっき層を形成する工程、前記めっき層を溶融することによって前記外部電極を形成する工程を含む、半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置において、貫通電極によって被覆された貫通孔の内部を充填する保護層にクラック等が発生する不具合を防止する。

【解決手段】

貫通電極9を被覆するとともに、貫通孔6内を充填する保護層10を備える半導体装置1において、保護層10が複数層11、12からなり、複数層の保護層のうち最も半導体基板2の一面2aに近い層が、少なくとも貫通電極の底面9aと側面9bの交差部を被覆し、かつ、ポジ型感光性樹脂を用いて形成されることを特徴とする半導体装置を提供する。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】複数の顧客による各々異なるLSIが共同で作製された基板を、守秘性が得られた状態で各々の顧客に提供できるようにする。

【解決手段】特定の顧客への提供対象とするLSIチップ領域331以外の領域が開放した開口部307aを備えるマスクパターン307を形成する。次に、マスクパターン307をマスクとし、開口部307に露出しているLSIチップ領域332をエッチング除去し、ブラインド領域301aを形成する。ブラインド領域301aの形成では、第1配線層302,第2配線層303,および第3配線層304を除去し、これらの下層の一部までを除去する。

(もっと読む)

半導体デバイスの製造方法及び積層化半導体デバイスの製造方法

【課題】半導体デバイスの薄型化工程および分割工程における半導体デバイスの歩留まり低下を抑制し、基板両面に配線層を有する半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイス110の製造方法は、基板101の一方の面に第1の半導体素子102を形成する工程と、第1の半導体素子102上に第1の配線層104を形成する工程と、支持基板上に保護樹脂層を形成する工程と、第1の配線層104と保護樹脂層とが接触するように、支持基板を基板101に支柱を介して固定する工程と、基板101の他方の面側に第2の配線層404を形成する工程と、基板101の一部及び支柱の一部又は全部を除去して基板101と支持基板とを分離する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20と、シリコン基板20の上方に形成された層間絶縁膜38と、層間絶縁膜38の上に互いに間隔をおいて複数形成されたヒューズ41a、41bと、層間絶縁膜38の上であって、隣接するヒューズ41a、41bの間に形成されたダミーパターン41xと、ヒューズ41a、41bのうちの少なくとも一部とダミーパターン41xとを覆うと共に、下から順に塗布型絶縁膜46と窒化シリコン膜47とを備えたパシベーション膜48と有する半導体装置による。

(もっと読む)

41 - 60 / 362

[ Back to top ]