Fターム[5F033RR27]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 感光性を有するもの (362)

Fターム[5F033RR27]に分類される特許

121 - 140 / 362

電子装置、電子装置の製造方法、電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる電子装置、電子装置の製造方法、電子機器を提供する。

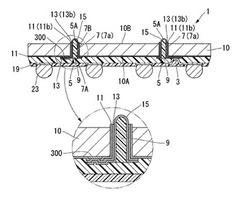

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに半導体基板10の能動面10A側に部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】能動素子、受動素子等の損傷や特性変化を防止しつつ、より小型化が図れる半導体装置を提供する。

【解決手段】複数の層2〜4が積層された半導体装置において、最上部に位置する第1配線層59と、最上部から下方の2番目に位置する第2配線層54と、第1配線層59と第2配線層54の間に形成された金属膜56と、金属層56の外周に形成され、第1配線層59と第2配線層54を接続する第1導電性プラグ58と、金属膜56及び第1配線層59の上方に形成されたパッド62と、パッド62と第1配線59を接続する第2導電性プラグ61とを有する。

(もっと読む)

液晶表示装置の製造方法

【課題】一対の電極間に形成される層間絶縁膜のコンタクトホールによって露出される導

電層と電極とのコンタクト抵抗が大きくなるのを抑制することが可能な液晶表示装置の製

造方法を提供する。

【解決手段】この液晶表示装置100の製造方法では、共通電位配線17および画素電極

19を覆うように有機膜からなる層間絶縁膜20を形成する工程と、層間絶縁膜20の共

通電位配線17に対応する領域にコンタクトホール20aを形成する工程と、コンタクト

ホール20aによって露出された共通電位配線17および層間絶縁膜20の表面をエッチ

ングする工程と、共通電位配線17にコンタクトホール20aを介して接続され、層間絶

縁膜20を挟んで画素電極19と対向するように設けられる共通電極21を形成する工程

とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置に設けられた半導体部品等の電極パッドとそれに接続されるべくインクジェット法により形成される配線との電気的な接続を好適に確保することのできる半導体装置、及びその半導体装置の製造方法を提供する。

【解決手段】半導体装置の第2電極パッド15に電気的に接続される金属配線膜19が、銀微粒子を分散媒に分散させた導電性インクからなる液滴(液層25L)の配置及び乾燥により形成される。このとき、第2電極パッド15の表面のメッキ層21に銀微粒子の結合層からなる中間層23Dを形成した後、中間層23Dを覆うかたちに上記分散媒を撥液する撥液材料を含む撥液層24を積層する。これにより、金属配線膜19は、その乾燥焼成を通じて中間層23Dと物理的に接続するようになり、撥液層24を間に挟みつつ第2電極パッド15と物理的に接続され、すなわち電気的にも接続されるようになる。

(もっと読む)

薄膜トランジスタ、表示装置、およびそれらの作製方法

【課題】薄膜トランジスタの電気特性の信頼性を高めることが可能な薄膜トランジスタ及びその作製方法を提供する。また、画質を向上させることが可能な表示装置及びその作製方法を提供する。

【解決手段】また、ゲート電極と、ゲート電極上に形成されるゲート絶縁層と、ゲート電極に重畳し、且つゲート絶縁層上に形成される酸化物半導体層と、ゲート絶縁層及び酸化物半導体層上に形成される配線と、酸化物半導体層及び配線に接する有機樹脂層とを有する薄膜トランジスタである。

(もっと読む)

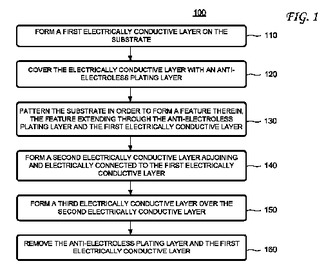

選択的な基板領域メッキを可能とする方法

本発明の方法は、基板(201)の選択的領域メッキを可能とする方法であり:前記基板に第一の電気的伝導層を形成し;前記第一の電気的導電性層(301)を抗−無電解メッキ層(410)で覆い;前記抗−無電解メッキ層と前記第一の電気的伝導層とを通して延長する構造(510、520)を形成するために、前記基板をパターン化し;前記第一の電気的伝導層に隣接してかつ電気的に結合された、第二の電気的伝導層(610)を形成し;前記第二の電気的伝導層の上に第三の電気的伝導層(710)を形成し;及び前記抗−無電解メッキ層と前記第一の電気的伝導層を除去することを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】窒化珪素膜でCu配線を挟み込むことによりCuによりTFTが汚染されるのを防ぐ。

【解決手段】結晶性半導体膜と、結晶性半導体膜上のゲート絶縁膜とゲート絶縁膜上のゲート電極と、結晶性半導体膜及びゲート電極上の第1の層間絶縁膜と、第1の層間絶縁膜に設けられた第1のコンタクト部を介して結晶性半導体膜に電気的に接続される第1の配線と、第1の層間絶縁膜及び第1の配線上の、第1の配線の一部を露出させた第2のコンタクト部が設けられた第1の窒化珪素膜及び第1の窒化珪素膜上の第2の層間絶縁膜と、第2のコンタクト部により露出させた第1の配線上に設けられたCuの拡散を防ぐバリア層と、第2のコンタクト部に設けられたバリア層上のCuでなる第2の配線と、第2の配線を被覆して設けられた第2の窒化珪素膜とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の使用時において熱による反りを抑制し、半導体装置の信頼性を向上させる。

【解決手段】縦型MOSトランジスタを構成する半導体基板10の表面上に、ソース領域と接続したソースパッド電極18が形成されている。ソースパッド電極18には、メッキ法により形成された表面電極23が形成されている。表面電極23にはバンプ電極31が接続されており、表面電極23は、バンプ電極31を露出する保護膜26に覆われている。一方、半導体基板10の裏面上には、ドレイン領域と接続した裏面電極30が形成されている。表面電極23と裏面電極30は、同じ線膨張係数を有した金属、好ましくは銅からなる。また、表面電極23と裏面電極30は、好ましくは同じ厚さ、あるいは略同じ厚さを有している。

(もっと読む)

メモリデバイスを実現する積層チップパッケージ

【課題】メモリデバイスを実現する積層チップパッケージにおいて、チップ間の電気的接続を行う配線を容易に形成でき、且つ配線の信頼性を高めることができるようにする。

【解決手段】積層チップパッケージ1は、本体2と、本体2の側面に配置された配線3A,3Bとを備えている。本体2は、それぞれ第1の種類の半導体チップを含む複数の第1の種類の階層部分12〜18と、第2の種類の半導体チップを含む第2の種類の階層部分11とを含んでいる。第1の種類の半導体チップは、複数のメモリセルを含んでいる。第2の種類の半導体チップは、複数の第1の種類の階層部分に含まれる複数のメモリセルに対する書き込みと読み出しを制御する回路を含んでいる。各階層部分は、半導体チップの少なくとも1つの側面を覆う絶縁部と、半導体チップに接続された複数の電極とを含んでいる。各電極の端面は、本体2の側面に配置され、配線3A,3Bに接続されている。

(もっと読む)

半導体装置、その半導体装置の製造方法及びパワーモジュール

【課題】絶縁層を厚くして電極間の寄生容量を低く抑えることができ、かつ、当該絶縁層に精度良く開口部を形成して作製される小型の半導体装置、その半導体装置の製造方法、及びその半導体装置を含むパワーモジュールを提供する。

【解決手段】セル160は、基板104と、基板104上に形成されるドレイン電極180、ソース電極182、及びゲート電極184と、基板104及び各電極上に形成され、ドレイン電極180の表面を露出する開口部220が形成された絶縁層142とを含む。開口部220は、ドレイン電極180の表面から絶縁層142の表面に向かってその径を広げながら所定高さまで立上がる壁面222と、基板104の表面から当該所定高さで基板104の表面に平行となった踊り場状の平坦面224と、平坦面224から絶縁層142の表面に向かってその径を広げながら立ち上がる壁面226とを有する。

(もっと読む)

半導体装置の製造方法

【課題】第1の再配線層のビア部内にレジスト膜を残存させることなく、第1の再配線層とビア部を介して電気的に接続される第2の再配線層を所望のパターンで形成することができる半導体装置の製造方法を提供する。

【解決手段】第2のレジスト膜34の第2の再配線層22が形成される領域に対応する領域Aに、露光光38を照射する。続けて、第2のレジスト膜34の第2の開口部20aが形成された領域に対応する領域Bに、露光光38を照射する。領域Aの内側に在る領域Bの第2のレジスト膜34は多重露光され、露光が深さ方向まで行き渡ることになる。現像処理により露光された第2のレジスト膜34を除去して、第2のレジスト膜34を所望の再配線パターンにパターニングする。第2の開口部20a内のレジスト膜34や、第1のビア部18aの凹部内のレジスト膜34も除去される。

(もっと読む)

半導体装置およびその製造方法

【課題】 配線の引き回しに制約を受けにくいようにする。

【解決手段】 第1の保護膜5上には複数の配線7が設けられている。配線7を含む第1の保護膜5上には、配線7の接続パッド部7cに対応する部分に開口部11を有する第2の保護膜10が設けられている。第2の保護膜10の開口部11を介して露出された配線7の接続パッド部7c上面およびその周囲における第2の保護膜10上には柱状電極13が設けられている。これにより、配線7の接続パッド部7cの平面サイズが柱状電極13の平面サイズよりも小さくなり、配線7の接続パッド部7c間の間隔を広くすることができ、ひいては配線7の引き回しに制約を受けにくいようにすることができる。

(もっと読む)

高周波デバイス及びその製造方法

【課題】コンタクトの剥がれ、絶縁膜表面の段差、及び、コンタクトの両端に発生する気泡を防止し、信頼性が高く、拡散工程の短い高周波デバイスを提供する。

【解決手段】本発明の高周波デバイス200は、Si基板201上に形成された能動素子と、前記Si基板201上に積層して形成されている10GHz以上の周波数における誘電正接が0.02以下で膜厚が10μm以上の絶縁膜205と、前記絶縁膜205上に形成されている受動素子を主に形成する配線層207と、前記能動素子と前記受動素子を主に形成する配線層207とを前記絶縁膜205を介して、前記Si基板201に対して垂直方向に接続する金属であるコンタクト206とを備え、前記コンタクト206は、無電解メッキによって形成されている。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】正常に動作しないチップに接続された配線に起因する問題を低減しながら、正常に動作しないチップを使用不能にする。

【解決手段】積層チップパッケージ1は、複数の階層部分11〜18を含む本体2と、本体2の側面に配置された配線3A,3Bとを備えている。複数の階層部分は、第1の種類の階層部分11〜16,18と、第2の種類の階層部分17とを含んでいる。第1の種類の階層部分と第2の種類の階層部分は、いずれも、半導体チップを含んでいる。第1の種類の階層部分は、それぞれ半導体チップに接続され、配線3A,3Bが配置された本体2の側面に配置された端面を有する複数の電極を含むが、第2の種類の階層部分は、半導体チップに接続されると共に配線3A,3Bが配置された本体2の側面に配置される端面を有する電極を含んでいない。配線3A,3Bは、複数の電極の端面に接続されている。

(もっと読む)

TFTアレイ基板の製造方法

【課題】簡単な工程で画素電極とコンタクトホールとを形成するTFTアレイ基板の製造方法を提供する。

【解決手段】絶縁膜を成膜する工程と、絶縁膜の上に導電膜を成膜する工程と、導電膜をパターニングして開口が設けられた画素電極を形成する工程と、開口が設けられた画素電極をエッチングマスクとしてエッチング法により絶縁膜に開口と連通するコンタクトホールを形成する工程と、を有することを特徴とするTFTアレイ基板の製造方法。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通電極で接続するにあたって、貫通孔底部の角部におけるリーク電流の発生や絶縁膜のクラック等を抑制する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。貫通孔3は半導体基板2の第1の面2aに開口された第1の開口3aの開口径が第2の面2bに開口された第2の開口3bに近い側の内径より大きくなるように、第1の面2aの近傍を拡張させる拡張部4を備える。半導体基板2の第1の面2aには第1の絶縁層5と第1の配線層6とが設けられている。貫通孔3には拡張部4を充填しつつ内壁面を覆う第2の絶縁層7が設けられており、さらに第1および第2の絶縁層5、7の開口を介して第1の配線層6と接続された第2の配線層8が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板と、ホトダイオードの出力を半導体基板の一方の主面側から他方の主面側に導く導電性部材との間の電気絶縁性を確保することが可能な半導体装置及びその製造方法を提供すること。

【解決手段】n型半導体基板105には、隣接するp型不純物拡散領域109間に、一方の主面側から他方の主面側に貫通する貫通孔105cが形成されている。貫通孔105cは、p型不純物拡散領域109それぞれに対応して設けられている。貫通孔105cを画成するn型半導体基板105の壁面上には、熱酸化膜113が形成されている。貫通孔105c内には、熱酸化膜113の内側に導電性部材としての貫通配線115が設けられている。貫通配線115の一端側の部分は、電極配線117の一端側の部分に電気的に接続されている。電極配線117は、熱酸化膜107上に形成されており、その他端側の部分がp型不純物拡散領域109に電気的に接続されている。

(もっと読む)

シリカ系塗膜形成用塗布液およびその調製方法

【課題】 本発明は、パターニング特性を備え、しかも比較的高い塗膜強度と比較的低い比誘電率を有し、さらには表面平坦性や耐クラック性などに優れたシリカ系塗膜を形成するための液状組成物からなるシリカ系塗膜形成用塗布液およびその調製方法に関する。

【解決手段】 パターニング特性を備えたシリカ系塗膜を形成するための液状組成物からなるシリカ系塗膜形成用塗布液であって、塩基性触媒成分を含有するシリカ系微粒子、特定の有機珪素化合物を加水分解して得られる珪素化合物および紫外線照射により酸を発生する酸発生剤を少なくとも含むシリカ系塗膜形成用塗布液および該シリカ系塗膜形成用塗布液の調製方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】パッドと半導体チップとの接続部分への応力の集中を防止することをができる半導体装置およびその製造方法を提供する。

【解決手段】半導体チップ2の最表面には、パッシベーション膜4が形成されている。パッシベーション膜4には、その下層に設けられた配線3の一部を露出させる開口5が形成されている。半導体チップ2上には、ポリイミド層6が積層されている。ポリイミド層6には、配線3における開口5を介してパッシベーション膜4から露出する部分と対向する位置に、それを厚さ方向に貫通する貫通孔7が形成されている。ポリイミド層6における貫通孔7の周辺部分8上および貫通孔7内には、その表面上に外部接続端子12が配置されるパッド9が形成されている。ポリイミド層6は、貫通孔7の周辺部分8が局所的に厚く形成されている。

(もっと読む)

121 - 140 / 362

[ Back to top ]