Fターム[5F033RR27]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 感光性を有するもの (362)

Fターム[5F033RR27]に分類される特許

21 - 40 / 362

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

半導体装置

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置、スタックドパッケージ型半導体装置および半導体装置の製造方法

【課題】巣及びボイドのないビアを形成する。

【解決手段】半導体基板11を貫通するビアホール51と、ビアホール51の内壁面を被覆する無機絶縁膜13と、無機絶縁膜13の表面に脱水縮合により一端が結合され、他端にメルカプト基又は含硫黄芳香族複素環式基を有するカップリング剤から形成されたカップリング層15と、メルカプト基又は含硫黄芳香族複素環式基に結合された触媒金属16と、触媒金属16上に形成された無電解めっき金属からなるシード層17と、ビアホール51を埋め込みシード層17上に形成された電解めっき金属18からなるビア18aと、を有する半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】スルーホールの微細化による半導体装置の高集積化と、スルーホール内に埋め込まれる導体のカバレッジ性と、を両立させる。

【解決手段】半導体装置は、下層配線2と、下層配線2上に形成され、下層配線2の上面を露出させる開口31を有する第1絶縁膜(例えば、有機絶縁膜3)と、第1絶縁膜上に形成され、スルーホール5が形成された第2絶縁膜(例えば、無機絶縁膜4)とを有する。半導体装置は、更に、スルーホール5に埋め込まれ、下層配線2と電気的に接続された導体9を有する。開口31は、上側に向けて拡径するテーパー形状に形成されている。スルーホール5の側壁5aの少なくとも下端は、開口31の側壁31aを構成する傾斜面の上に位置している。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

硬化性組成物およびそれを用いた薄膜トランジスタ

【課題】光硬化性を有し、かつ耐溶剤性、メタル配線への密着性に優れた薄膜を与える硬化性組成物を提供することである。

【解決手段】 必須成分として(A)光重合性官能基を有する化合物、(B)アルケニル基を有する化合物、(C)SiH基を有する化合物、(D)光重合開始剤 (E)ヒドロシリル化触媒を含有する硬化性組成物であり、

成分A、Dよる光重合反応と成分B、Cおよび成分Eによるヒドロシリル化反応の2種の反応が進行することにより、光硬化性を有しながら耐溶剤性、メタル配線への密着性に優れた薄膜を与える得ることが可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】回路を形成した半導体ウェハをダイシングするときに発生するクラックの伝搬を抑制する。

【解決手段】ウェハ1上のチップ領域2にMOSトランジスタT1及び配線31,48,54,64,64を形成すると共に、チップ領域2内でMOSトランジスタT1及び配線31,48,54,64,64を囲むガードリング76を形成する。また、ウェハ1上のスクライブライン領域3には、チップ領域2に第1層の配線31を形成するときに、第1の応力吸収パターン33を同時に形成する。さらに、最上層の配線74を形成するときに、第2の応力吸収パターン77を同時に形成する。各応力吸収パターン33,77は、チップ領域2を囲むように連続して形成され、スクライブライン領域3の中心線SCを跨ぐベタパターンである。ダイシング時には、第1及び第2の応力吸収パターン33,77の一部が残るようにウェハ1を切断する。

(もっと読む)

検出装置及び放射線検出システム

【課題】 更なる小画素ピッチ化及び多画素化が求められる検出装置、特に、積層型の検出装置において、信号線容量の更なる低減による低ノイズ化及び駆動線の時定数の更なる低減による高速駆動化が可能な検出装置を提供する。

【解決手段】 放射線又は光を電荷に変換する変換素子104と、スイッチ素子105と、を含み、行方向及び列方向に配列された複数の画素102と、行方向の複数のスイッチ素子105に接続された駆動線107と、列方向の複数のスイッチ素子105に接続された信号線108と、を有し、変換素子104がスイッチ素子105の上方に配置された検出装置であって、信号線108は、変換素子104の下方に配置されたスイッチ素子の主電極の最上位表面105よりも下方に配置された駆動線107の最上位表面よりも下層の絶縁部材に埋め込んで形成された導電層202からなることを特徴とする。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 アンダーフィル材を用いなくとも、柱状電極と半田端子との接合強度不足や、信頼性の低下を抑制する。

【解決手段】 半導体装置は、半導体基板と、半導体基板上に設けられた複数の配線と、複数の配線上にそれぞれ接続された複数の半田端子と、複数の配線の少なくとも一部を覆う樹脂層と、を備えている。樹脂層上には、少なくとも半田端子の周囲を覆うオーバーコート膜が被膜され、隣接する半田端子間のオーバーコート膜の高さは、半田端子の高さよりも低い。

(もっと読む)

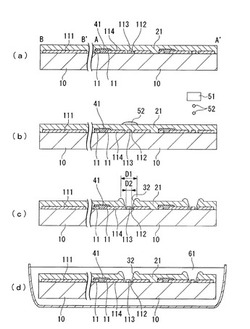

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

21 - 40 / 362

[ Back to top ]