Fターム[5F033SS21]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 塗布 (1,869)

Fターム[5F033SS21]の下位に属するFターム

塗布後に焼成するもの (977)

Fターム[5F033SS21]に分類される特許

21 - 40 / 892

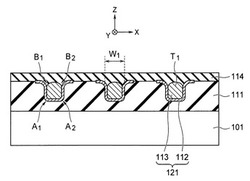

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

3DIC方法および装置

【解決手段】 切り分けられたダイまたはウェハのような素子を3次元的に集積する方法および切り分けられたダイまたはウェハのような素子が接続された集積構造。ダイまたはウェハの一方または両方は、その中に形成された半導体デバイスを有する。第1コンタクト構造を有する第1素子は、第2コンタクト構造を有する第2素子に接着される。第1、第2コンタクト構造は、接着の際に露出されることが可能で、また接着の結果、電気的に接続される。接着後にビアがエッチングされるとともに埋め込まれて電気的配線を露出および形成して第1、第2コンタクト構造を接続するとともに、この電気的配線への表面からの電気的なアクセスが可能になる。または、第1、第2コンタクト構造は接着の際に露出されず、接着後にビアがエッチングおよび埋め込みされて第1、第2コンタクト構造が電気的に接続されるとともに接続された第1、第2コンタクト構造への電気的なアクセスが得られる。 (もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

半導体装置の製造方法

【課題】所定値以上の厚みを有するパッドを少ない工程数で形成することができる半導体装置の製造方法を提供すること。

【解決手段】本発明は、アルミ層22を、半導体基板上に形成された層間絶縁膜1の上方に堆積させる。アルミ層22上には、アルミ層24を堆積させる。パッド領域102のアルミ層24の上方に、フォトレジスト7を形成する。フォトレジスト7を用いてエッチングを行うことにより、パッド領域102にパッド上層52を形成するとともに、配線領域101のアルミ層24を除去する。そして、フォトレジスト8を、パッド領域102のパッド上層52を覆い、かつ、配線領域101で配線パターンを構成するように形成する。フォトレジスト8を用いてエッチングを行うことにより、パッド領域102にパッド下層51を形成するとともに、配線領域101に配線2を形成する。

(もっと読む)

半導体装置

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

表側および裏側の電気インターコネクトを含む集積回路

【課題】シリコン・オン・インシュレータ(SOI)基板の層内に配置された複数のトランジスタ、および層の第1の側の上に配置されたベース酸化物層を含むSOI基板を備えた集積回路を提供すること。

【解決手段】集積回路はまた、層の第1の側に形成された第1のインターコネクトを含むことができ、第1のインターコネクトが、複数のトランジスタのうちの第1のトランジスタと複数のトランジスタのうちの第2のトランジスタとを電気的に接続することができる。加えて、集積回路は、層の第1の側とは反対の層の第2の側に形成された第2のインターコネクトを含み、第2のインターコネクトが、複数のトランジスタのうちの第3のトランジスタと複数のトランジスタのうちの第4のトランジスタとを電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

貫通配線付き接合基板

【課題】貫通孔内に配した樹脂が熱膨張することによって電極を破損することを防止した貫通配線付き接合基板の提供。

【解決手段】

一面1aに電極層2が形成された第一基板1、及び電極層2と接合樹脂層3を介して、第一基板1と接合された第二基板4とを備えた貫通配線付き接合基板10Aであって、第一基板1の他面1b側から電極層2が露出するまで第一基板1を貫通する貫通孔5と、貫通孔5の内部において、貫通孔5の内側面5c及び電極層2を覆う貫通配線層6と、貫通配線層6を覆い貫通孔5の内部に充填された充填樹脂部7とを有し、充填樹脂部7を構成する樹脂のヤング率は、接合樹脂層3を構成する樹脂のヤング率よりも小さいことを特徴とする貫通配線付き接合基板10A。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

回路基板、回路基板の製造方法、表示装置および電子機器

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の一主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】2枚の基板の貼り合わせによって電極間接合がなされた構成において、電極材料の拡散を防止しつつも貼り合わせ強度が確保され、これによって信頼性の向上が図られた三次元構造の半導体装置を提供する。

【解決手段】第1電極33、および第1電極33の拡散防止材料で構成され第1電極33の周囲を覆う第1絶縁膜35を含むと共に、第1電極33と第1絶縁膜35とで貼合せ面41が構成された第1基板2と、第1基板2に貼り合わせて設けられ、第1電極33に接合された第2電極67、および第2電極67の拡散防止材料で構成され第2電極67の周囲を覆う第2絶縁膜69を含むと共に、第2電極67と第2絶縁膜69とで第1基板2に対する貼合せ面71が構成された第2基板7とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

(もっと読む)

半導体装置、及びその製造方法

【課題】多孔質低誘電率絶縁膜が用いられていても、絶縁破壊耐性に優れた配線構造の半導体装置を提供する。

【解決手段】CMP処理工程を経て配線膜が構成される半導体装置の製造方法であって、CMP処理によって汚染された多孔質低誘電率絶縁膜に対して、酸処理、アニール処理、あるいは汚染個所の清浄化処理工程を施し、前記多孔質低誘電率絶縁膜表面の有機成分量、水分量、銅、ナトリウム、カリウム等の残存量を規定値以下に低減する。

(もっと読む)

21 - 40 / 892

[ Back to top ]