Fターム[5F033SS21]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 塗布 (1,869)

Fターム[5F033SS21]の下位に属するFターム

塗布後に焼成するもの (977)

Fターム[5F033SS21]に分類される特許

61 - 80 / 892

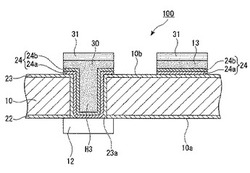

半導体装置、半導体装置の製造方法、回路基板および電子機器

【課題】電極パッドと貫通電極との接続面積を確保しつつ、下地膜が確実に形成される半導体装置、半導体装置の製造方法、回路基板および電子機器を提供する。

【解決手段】半導体基板10の能動面10a側に設けられた第一絶縁膜22と、第一絶縁膜22上に設けられた電極パッド12と、電極パッド12の形成位置に対応し、半導体基板10および第一絶縁膜22に形成された貫通孔H3と、貫通孔H3の少なくとも側面に設けられた第二絶縁膜23と、第二絶縁膜23と電極パッド12とを覆うように設けられた下地膜24と、下地膜24の内側で、貫通孔H3に埋め込まれた導電材料からなる貫通電極30と、を具備した半導体装置100において、貫通孔H3の側面と電極パッド12の裏面との角部23aに、第二絶縁膜23がフィレット状に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

半導体装置、回路基板および電子機器

【課題】半導体基板と貫通電極との絶縁を確実とする半導体装置を提供する。

【解決手段】半導体装置10の一方の面14から他方の面16に形成された電極パッド24の裏面に到達する貫通電極13を形成した半導体装置10であって、他方の面16側には第1の絶縁膜20を介して電極パッド24が設けられ、貫通電極13を構成する貫通孔21と第1の絶縁膜20との境界面に、一方の面14側の開口よりも大きい開口を有し、貫通電極13を形成する際、他方の面16側の貫通孔21開口部内周に貫通電極13を構成する導電材料と電極パッド24との間に第2の絶縁膜23を備え、貫通孔21内壁面および第2の絶縁膜上に第3の絶縁膜22が設けられる。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

基板処理方法および記憶媒体

【課題】 変性処理およびその後の溶解処理によるダメージにより低誘電率膜のk値が上昇した場合にも十分にk値を回復させることができる基板処理方法を提供すること。

【解決手段】 低誘電率膜をエッチング処理して所定パターンを形成し(ステップ3)、エッチング処理を終了した後に残存する物質を所定の液に対して可溶化するように変性し(ステップ8)、ステップ8の後、パターンが形成された低誘電率膜の表面にシリル化剤を供給し、ステップ8の際に低誘電率膜に入ったダメージを回復するためのシリル化処理をし、変性された物質を溶解除去し(ステップ9)、ステップ9の後、パターンが形成された低誘電率膜の表面にシリル化剤を供給し、ステップ9の際に低誘電率膜が受けたダメージを回復するためのシリル化処理をし(ステップ10)、ステップ10の後、基板をベークしてシリル化処理後の低誘電率膜の比誘電率を下げる(ステップ11)。

(もっと読む)

膜形成方法および半導体装置の製造方法

【課題】担持体上に形成したポリシラザン膜を転写することにより、基板表面に良好な膜を形成することのできる技術を提供する。

【解決手段】ポリシラザン材料を含む塗布液PをシートフィルムFの表面に塗布し、溶剤を揮発させることでポリシラザン薄膜Rを得る。これを半導体基板に転写するのに先立って、UV光源202から拡散板203を介して強度を均一化したUV光Lを薄膜Rに照射する。これにより、薄膜Rの表面Raの粘度が選択的に増大し、基板転写時に、基板表面に形成されたトレンチを埋めることなくエアギャップを形成することができる。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

61 - 80 / 892

[ Back to top ]