Fターム[5F033UU01]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445)

Fターム[5F033UU01]の下位に属するFターム

Fターム[5F033UU01]に分類される特許

41 - 60 / 300

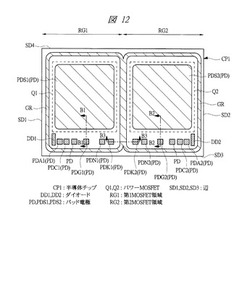

半導体装置

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】半導体チップCP1には、スイッチ用のパワーMOSFETQ1,Q2と、パワーMOSFETQ1の発熱を検知するためのダイオードDD1と、パワーMOSFETQ2の発熱を検知するためのダイオードDD2と、複数のパッド電極PDとが形成されている。パワーMOSFETQ1およびダイオードDD1は、辺SD1側の第1MOSFET領域RG1に配置され、パワーMOSFETQ2およびダイオードDD2は、辺SD2側の第2MOSFET領域RG2に配置されている。ダイオードDD1は辺SD1に沿って配置され、ダイオードDD2は辺SD2に沿って配置され、ダイオードDD1,DD2間にソース用のパッド電極PDS1,PDS2以外の全てのパッド電極PDを辺SD3に沿って配置している。

(もっと読む)

半導体集積回路装置

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】フリップチップ構造を有する半導体集積回路装置において、応力の影響を受ける半導体チップ101の外周列におけるパッド102の構造及び配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトする。

(もっと読む)

半導体装置

【課題】 パッド内での過度の電流集中を抑制することが可能なパッド構造を有する半導体装置を提供する。

【解決手段】 半導体基板の上に、絶縁性材料からなる第1の絶縁膜が形成されている。第1の絶縁膜の上に、導電材料からなるパッド部が形成されている。パッド部に電気的に連続し、第1の幅W1を有する配線部が形成されている。第1の絶縁膜の上であって、パッド部の外周線から第2の幅W2より内側の第1の領域に、複数の第2の絶縁膜が配置されている。配線部とパッド部との境界線に最も近い第2の絶縁膜を連ねる直線のうち、配線部をパッド部内に延長した領域と重なる部分が、パッド部の導電材料と交差する長さをL3としたとき、W1≦2×W2+L3を満たす。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】寄生容量を低減し、高性能化を図った固体撮像装置等の半導体装置とその製造方法、前記固体撮像装置を備えたカメラ等の電子機器を提供するものである。

【解決手段】本発明の半導体装置は、2つ以上の半導体チプ部22,26が貼り合わされた積層半導体チップ27を有する。積層半導体チップ27では、少なくとも第1の半導体チップ部22に画素アレイ23と多層配線層41が形成され、第2の半導体チップ部26にロジック回路25と多層配線層55が形成される。第1の半導体チップ部22には、一部の半導体部分が全て除去された半導体除去領域52が形成され、半導体除去領域52内に第1の半導体チップ部22と第2の半導体チップ部26との間を接続する複数の接続配線67が形成される。この半導体装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置

【課題】デュアルダマシン構造の多層配線構造を有する半導体装置において、コンタクトのストレスマイグレーション耐性を向上させる。

【解決手段】デュアルダマシン構造を有する上層導体パターン47Aは延出部47Bに設けられたビアプラグ47Cを介して下層配線パターン43Aと接続している。この接続部でのストレスマイグレーションによる接続不良を防止するため延出部47Bより先端部の領域に下層配線層のダミーCuパターン43Bとダミービアプラグ47Dで接続する構造を追加する。ストレスマイグレーションは先端部の下層配線層のダミーCuパターン43Bとダミービアプラグ47Dの接続部で発生し、ビアプラグ47Cと下層配線パターン43Aの接続部ではストレスマイグレーションの発生は防止される。

(もっと読む)

回路素子

【課題】回路素子の向きを簡単な構成で認識しやすくすることにより、実装ミスの低減を図る回路素子を提供する。

【解決手段】複数の接続パッド31a及び31bの一部である接続パッド31aと基板32との間に設けられた成膜層33は、基板32側の配線33b上に保護膜33c側の配線33aが直接重ねられ、複数の接続パッド31a及び31bの残りと基板32との間に設けられた成膜層33は、2層の配線33a、33b間に絶縁層33eが設けられている。そして、これにより接続パッド31aと基板32との間に設けられた成膜層33の膜厚d1と、複数の接続パッド31bと基板32との間に設けられた成膜層33の膜厚d2と、を互いに異ならせて、互いに色が異なるように視認させる。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性が向上した半導体装置およびその製造方法の提供。

【解決手段】第1の辺を有する第1の面を有する半導体基板10と、前記半導体基板上に設けられた電極14と、前記電極の上に位置する第1の開口部24を有する第1の絶縁層16と、前記第1の絶縁層の上であって、前記電極の少なくとも一部を避けて設けられた樹脂層20と、前記樹脂層の上に設けられた第1の部分31と、前記第1の部分と前記電極とを電気的に接続する第2の部分32と、前記第1の部分または前記第2の部分と電気的に接続する第3の部分33と、を有する導電層と、前記導電層の前記第2の部分を覆うように設けられ、前記導電層の前記第1の部分の少なくとも一部の上に位置する第2の開口部41を有し、かつ、前記導電層の前記第3の部分を避けて設けられた第2の絶縁層40と、前記導電層の前記第3の部分は、前記第1の面の前記第1の辺と、前記第2の絶縁層との間に位置する。

(もっと読む)

半導体集積回路装置及びその入出力用ボンディングパッドの配置方法

【課題】電源用ボンディングパッドが同一周回上で複数の電源に対応することを実現することで、半導体集積回路装置の設計時における高い自由度を確保しながらも、良好な電気特性の実現、消費電流の増大への対応、空間の有効活用、及び基板への実装時のマークとしての効果を有する半導体集積回路装置及びその入出力用ボンディングパッドの配置方法を提供する。

【解決手段】半導体集積回路装置の外縁部に沿って周回する額縁状の位置で、周回と直交する方向に分断されることで形成される2つ、又はそれ以上の領域に配置された外部接続用パッドを備える。

(もっと読む)

シリコン貫通ビアのためのESD/アンテナダイオード

概略を述べると、アンテナダイオードが、少なくとも一部がTSVの周囲の排他的区域内に形成され、金属1層の導電体を介してTSV(シリコン貫通ビア)に接続されている。それと同時に、TSVは、排他的区域の外側に位置する1又は複数のトランジスタのゲートポリ又は拡散領域に接続している。 (もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

半導体装置

【課題】WCSPの再配線を用いて、回路から発生するノイズが他の回路ブロックへ干渉することを防ぎ、特性劣化を防止できる半導体装置を提供する。

【解決手段】2以上の回路ブロック1、2が形成される半導体基板と、前記半導体基板の回路形成面上に配置され外部端子3a〜3e、4a〜4eが先端に設けられるポストと、該ポストの基端と前記半導体基板の回路形成面における前記回路ブロック1、2の電極端子とを接続する再配線12a、12b、16a、16bとが樹脂封止された封止樹脂層とを備える半導体装置において、前記2以上の回路ブロック1、2のうち少なくとも1つの回路ブロック1、2では、接地用の前記電極端子と接地用の前記外部端子3a〜3e、4a〜4eとを接続する前記再配線12a、12b、16a、16bが自回路ブロック1、2の形成領域の全部または一部を覆うように設けられている。

(もっと読む)

半導体装置および携帯機器

【課題】差動信号の伝送特性に優れ、かつ、簡易な構成の半導体装置を提供する。

【解決手段】半導体装置100、一対の差動伝送線路26を含む配線層12と、電位が固定された導電層であって、電気的に連続した導体によって形成された連続領域を有する導電層16と、半導体基板24と、半導体基板24と導電層16との間に設けられ、電気的に浮いている導体を有する阻止層20と、配線層12と導電層16と阻止層20と半導体基板24との間に設けられた絶縁層と、を備える。一対の差動伝送線路26は、積層方向から見て導電層16の導体と交差し、阻止層20は、導電層16の導体と交差する複数の間隙が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、配線層の平坦性を保つためのダミーパターンを有する半導体装置とその製造方法を提供することを目的とする。

【解決手段】半導体装置の機能を実現するうえで必要な機能パターンと、半導体装置の所定の層に、前記機能パターンと共に複数のダミーパターンとを備え、第一の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンが配置されない領域に、第二の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンと前記機能パターンとの間に前記第二の大きさの複数のダミーパターンが配置され、第一所定方向に配置された前記第一の大きさの複数のダミーパターンと、第二所定方向に配置された前記第二の大きさの複数のダミーパターンとは隣り合い、前記第一の大きさのダミーパターン間の幅は、前記第二の大きさのダミーパターン間の幅よりも大きい。

(もっと読む)

ボンドパッドを有する半導体装置およびそのための方法

【課題】ワイヤボンド接続の信頼性を低下させることなくダイをプローブ検査でき、小さいボンドパッドおよびボンドパッド間の微細なピッチ間隔でダイについての確実なプローブ検査が行える技術の提供。

【解決手段】ボンドパッド36が、実質的に重なりのないプローブ37領域およびワイヤボンド38領域を有する。ボンドパッド36は最終金属層パッド16に接続されている。ボンドパッド36はアルミニウム製であり、最終金属層パッド16は銅製である。プローブ37領域をワイヤボンド38領域から分離することで、最終金属層パッド16がプローブ検査によって損傷を受けることが防止され、より信頼性の高いワイヤボンドが可能となる。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

半導体集積回路装置

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体チップの小型化を妨げたり、回路設計を煩雑にしたりすることなく、前工程においてケルビンコンタクト法を用いた半導体集積回路の電気特性検査を行うことを可能とする。

【解決手段】検査装置のプローブカードは、コイル型プローブ針とその内側に配置されたポゴピン型プローブ針とで構成されたケルビンコンタクト用プローブ針および2端子測定用プローブ針を備えている。ウエハのチップ領域1Aに形成された電極パッド2、3は、ケルビンコンタクト用プローブ針が接触する電極パッド3の面積をB、2端子測定用プローブ針が接触する電極パッド2の面積をAとしたとき、A≦B<2Aの関係にある。

(もっと読む)

集積回路装置

【課題】チップサイズを増加させずに、チップ位置情報等の識別情報を記録した集積回路装置を提供すること。

【解決手段】集積回路を有する集積回路基板と、前記集積回路に接続された導電性パッドと、前記導電性パッドを露出する開口部を持つ絶縁膜を備えた外部電極構造体とを有し、前記外部電極構造体が、前記集積回路基板の識別情報に対応する形状を有すること。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズを大きくすることなく、チップ外周のガードリングの、外部応力に対する耐性を強化する。

【解決手段】この半導体装置は、半導体基板と、半導体基板上に形成された集積回路部と、半導体基板上の集積回路部の周辺に存在する絶縁層中に形成された、集積回路部を包囲するガードリング4と、を有する。ガードリング4は、半導体基板に対して垂直な方向に関して重なる位置に配された少なくとも2層の配線層M1,M2,M3と、これらの配線層間を接続するビア9a,9bと、で構成される。ビア9a,9bの形状が、ガードリング4の近傍に位置する一のダイシングライン3から垂直に集積回路部側へ向かう外部応力10を分散させる形状となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグの断面に占めるバリア層の割合が比較的小さい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板101と、基板中に形成され、基板の表面に平行な第1方向に沿って交互に設けられた素子分離層及び活性層111,112と、素子分離層及び活性層上に形成され、個々の活性層上に、個々のコンタクトプラグ用の穴を有する層間絶縁膜121と、上記穴の内部に露出した活性層の上面、及び上記穴の上記第1方向に垂直な2つの側面のうちの片側の側面に形成されたバリア層131と、上記穴の内部のバリア層上に形成されたプラグ材層132とを備える。

(もっと読む)

41 - 60 / 300

[ Back to top ]