Fターム[5F033UU01]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445)

Fターム[5F033UU01]の下位に属するFターム

Fターム[5F033UU01]に分類される特許

21 - 40 / 300

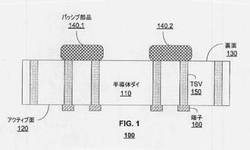

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の品質及び製造歩留まりを向上させる。

【解決手段】半導体装置の製造方法は、SOQウェハ等の貼り合せウェハに複数の半導体チップ部を形成する工程と、絶縁膜を含む下部層(611,621)とメタル配線(メタル層)を含む上部層(612,622)とを有する配線層(61,62)を形成するプロセスを複数回行うことによって、複数の半導体チップ部上に多層配線構造(6)を形成する工程とを有し、ダミーチップ部上に複数重ねられた配線層(61,62)は、製品チップ部上における配線層と同じ形状(パターン)を持つ第1の配線層(61又は62)と、第1の配線層と異なる形状を持つ第2の配線層(62又は61)とを含み、ダミーチップ部上に複数重ねられた配線層のいずれかにおける下部層(611又は621)は、貫通メタル配線を持たない絶縁膜である。

(もっと読む)

配線層の形成方法及び半導体装置の製造方法

【課題】配線層の表面の平坦度を高めることができ且つ配線間隔が広い領域において磁界を変動させる構成を無くした配線層の形成方法及び半導体装置の製造方法を提供する。

【解決手段】配線層の形成方法は、下側部材上に配線パターン102を形成する工程と、その上に絶縁材料層103,106を形成する工程と、配線パターンの間に形成された絶縁材料層の一部を、絶縁膜ブロック111として残すと共に、絶縁膜ブロック111の高さを、絶縁膜ブロック以外の絶縁材料層の高さより高くなるように、絶縁材料層をエッチング処理する工程と、絶縁膜ブロックを含む絶縁材料層を研磨して、表面が平坦化された層間膜を形成する工程とを有する。半導体装置の製造方法は、半導体基板と配線層とを有し、上記配線層の形成方法を用いて配線層の少なくとも1つを製造する。

(もっと読む)

配線パターン

【課題】コンタクトホールを起点とした絶縁膜の剥がれの伸展を防ぐことができる配線パターンを得る。

【解決手段】半絶縁性GaAs基板1上に、配線メタル2が設けられている。配線メタル2上に金メッキ4が設けられている。金メッキ4は、ボンディングパッド部5と配線部6を有する。ボンディングパッド部5及び配線部6を覆うように金メッキ4上に連続してSiN膜7が設けられている。ボンディングパッド部5上においてSiN膜7にコンタクトホール8が設けられている。ボンディングパッド部5と配線部6の間において金メッキ4に段差が設けられている。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

ディスプレイ装置及びその製造方法

【課題】構造及び製造工程を簡素化しながら、開口率を向上させた、ディスプレイ装置及びその製造方法を提供する。

【解決手段】本発明の実施形態に係るディスプレイ装置101は、基板111、前記基板111上に形成された前記第1透明導電膜1301及び前記第1透明導電膜1301上に形成された第1金属膜1302を含む多重膜構造と前記第1透明導電膜1301で形成された単一膜構造とを含むゲート配線、前記ゲート配線の一部の領域上に形成された半導体層153、そして前記半導体層上に形成された第2透明導電膜1701及び前記第2透明導電膜1701上に形成された第2金属膜1702を含む多重膜構造と前記第2透明導電膜1701で形成された単一膜構造とを含むデータ配線を含む。

(もっと読む)

半導体装置

【課題】電極パッド直下の領域を有効領域とする半導体装置の提供を目的とする。

【解決手段】本発明の半導体装置は、半導体層上に設けられた、シリサイド膜からなるエミッタ電極7と、エミッタ電極7上に形成された絶縁膜10と、絶縁膜10上に形成されたAlからなる電極パッド8とを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】周期的に配列された複数本の配線と導電部材が設けられ、導電部材に配線よりも高い電圧を印加することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、一方向に延び、周期的に配列された複数本の第1配線と、前記複数本の第1配線からなる群の外側に配置され、前記一方向に延びる第2配線と、前記群と前記第2配線との間に設けられた第3配線と、前記第2配線から見て前記群の反対側に配置された複数の導電部材と、を備える。そして、前記第1配線と前記第3配線との最短距離、及び前記第3配線と前記第2配線との最短距離は、前記第1配線間の最短距離と等しく、前記第2配線と前記導電部材との最短距離は、前記第1配線間の最短距離よりも長い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】生産性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、積層構造体MLと、選択ゲート電極SGと、半導体ピラーSPと、記憶層48と、内側絶縁膜42と、外側絶縁膜43と、選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、電極間絶縁膜62と、を有する。選択ゲート電極は、積層構造体と積層された複数の選択ゲート導電膜71と、選択ゲート導電膜間絶縁膜72と、を有する。半導体ピラーは、積層構造体及び選択ゲート電極を第1方向に貫通する。記憶層は、電極膜と半導体ピラーとの間に、内側絶縁膜は、記憶層と半導体ピラーとの間に、外側絶縁膜は、記憶層と電極膜との間に、選択ゲート絶縁膜は、選択ゲート導電膜と半導体ピラーとの間に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体集積回路およびそのパターンレイアウト方法

【課題】CMP処理においてダミーパターンに機械的ストレスが作用しても、ダミーパターンが折れ曲がったり、ダミーパターンの一部が欠落したりすることを抑制できる半導体集積回路およびそのパターンレイアウト方法を提供する。

【解決手段】半導体集積回路は、所定の機能領域と、空き領域SP1に形成されたダミーパターンDMP1とを備える。空き領域SP1は、所定の機能領域同士の間に位置する。ダミーパターンDMP1は、枠状に形成されるとともに、ダミーパターンDMP1の外縁EDを規定する第1メタル部MT1と、第1メタル部MT1の内周側に位置し、第1メタル部MT1に連続するように形成された第2メタル部MT2と、第1メタル部MT1の内周側において第2メタル部MT2が形成されていない領域に位置する複数の非形成領域NTと、を有する。

(もっと読む)

ドライバー集積回路チップの電源連結構造

【課題】本発明は、ドライバー集積回路チップの電源連結構造に関し、より詳細には、ドライバー集積回路チップ内部のルーティングパターンをLOGと並列で配置して、チップの両端に配置された電源を連結することで配線を簡素化してライン抵抗を減少させることができるドライバー集積回路チップの電源連結構造を提供する。

【解決手段】本発明によるドライバー集積回路チップの電源連結構造によると、ドライバー集積回路チップの入出力端子の配線数を減少させて配線を簡素化して、これによりチップサイズを減らして及び製造費用を減少させることができる効果があり、チップ内部のルーティングパターンとLOGを並列で連結することでライン抵抗が減少されて、信号の遅延を減らすことができる長所がある。

(もっと読む)

半導体装置の設計方法及び製造方法

【課題】トランジスタ等の電気的特性のばらつきを低減し得る半導体装置の設計方法及び半導体装置の製造方法を提供する。

【解決手段】素子領域の実パターンである複数の第1の実パターンと、ゲート配線の実パターンである複数の第2の実パターンとを配置するステップと、レイアウト領域を複数の分割領域に分割するステップと、レイアウト領域内に、ダミーの素子領域のパターンである複数の第1のダミーパターンと、ダミーのゲート配線のパターンである複数の第2のダミーパターンとを配置するステップであって、分割領域内における第1の実パターン、第2の実パターン、第1のダミーパターン及び第2のダミーパターンの周囲長の総和の、分割領域間におけるばらつきが、所定の範囲内となるように、第1のダミーパターン及び第2のダミーパターンを配置する。

(もっと読む)

半導体集積回路及びその製造方法

【課題】検査時におけるプロービングの機械的な力学的ストレスや、組立のワイヤ・ボンディングによる機械的な力学的ストレスによって発生する応力を緩和できる構成を有する半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンと電気的に接続する第1のバス(140)と、第2の金属パターンと電気的に接続する第2のバス(150)と、第1のバス(140)及び第2のバス(150)に1つづつ設けられたコンタクト・パッド(304)とを備え、第1のバス(140)及び第2のバス(150)の各々には、少なくとも1つのスリット(10a)が形成されている。

(もっと読む)

評価素子

【課題】チャージアップした電荷を検出する感度を向上させること。

【解決手段】半導体基板10上に形成された絶縁膜14と、前記絶縁膜内に形成され、延伸方向に延伸した延伸部22を含む第1配線20と、前記絶縁膜内に設けられ、前記半導体基板と前記延伸部とを電気的に接続するコンタクト26と、前記絶縁膜内に形成され、前記延伸部と前記半導体基板の面方向に対向し前記延伸部より長さの短い対向部32と、前記対向部から前記第1配線の反対方向に引き出される引き出し部34と、を含む第2配線30と、前記引き出し部に電気的に接続されたアンテナ電極40と、含む評価素子。

(もっと読む)

21 - 40 / 300

[ Back to top ]