Fターム[5F033VV03]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | シールド (219)

Fターム[5F033VV03]に分類される特許

1 - 20 / 219

半導体装置およびその製造方法

【課題】同一レイヤに成膜された後、複数回のエッチングにより形成された導電性被加工物を、下地層に段差を作ることなく、異なる電位に固定する。

【解決手段】同一レイヤに成膜された後、複数回のエッチングにより線状に形成された導電性被加工物を備え、導電性被加工物は、自身を電気的に分断する2以上の分断部分を有し、分断部分における導電性被加工物は、その一部が平行になるように形成されており、平行に形成された部分の少なくとも一方は分断されている。複数回のエッチングに用いられるレジストパターンのうちの、所定回数目のエッチングに用いられる第1のレジストパターンと、他の回数目のエッチングに用いられる第2のレジストパターンとが重なる領域の、平行に形成された部分に対応する箇所の幅は、エッチングによる導電性被加工物の後退量より小さい。本技術は、半導体装置に適用することができる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

半導体装置

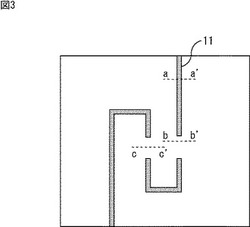

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線レイアウトや配線構造の複雑化や大幅な変更を伴うことなく、積層配線間に生じるクロストークノイズを低減する。

【解決手段】配線103上に絶縁膜104及び106を挟んで配線108が形成されている。配線103と配線108とは平面視において少なくとも部分的にオーバーラップしている。少なくとも配線103と配線108とのオーバーラップ部分の前記絶縁膜中に導電性シールド層105が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法

【課題】ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体装置の正面と背面に対応する正面と背面を有する装置基板と、装置基板の正面上に形成される金属層部と、半導体装置の背面に設置され、金属層部と電気的に接続するボンディングパッドと、装置基板の背面上に設置されるシールド構造と、を含み、シールド構造とボンディングパッドは異なる厚さを有する。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置

【課題】埋め込み電極プラグからの応力伝播による半導体装置の特性変動、および、埋め込み電極プラグからの電気的雑音伝播による、半導体装置の動作不安定化を防止する。

【解決手段】半導体基板と、半導体基板上に形成された半導体素子を有する素子形成領域と、半導体基板を貫通するように設けられた1以上の埋め込み電極プラグと、素子形成領域と埋め込み電極プラグの間の半導体基板内に位置するトレンチ内に埋め込まれた溝型電極と、を有する半導体装置。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置

【課題】高出力の高周波信号の影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、電子回路が設けられた主面を有する半導体基板10と、前記主面の上に絶縁膜2,3,4を介して設けられたパッシブ回路30と、を備える。そして、前記半導体基板と前記パッシブ回路との間に前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙45を有した第1の導体層40と、前記第1の導体層と前記パッシブ回路との間に、前記第1の導体層および前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙55を有し、前記パッシブ回路から見た前記第1の導体層の間隙を覆う第2の導体層50と、を備える。

(もっと読む)

1 - 20 / 219

[ Back to top ]