Fターム[5F033XX03]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 微細化 (1,181)

Fターム[5F033XX03]の下位に属するFターム

高アスペクト化 (211)

Fターム[5F033XX03]に分類される特許

21 - 40 / 970

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置及びその製造方法

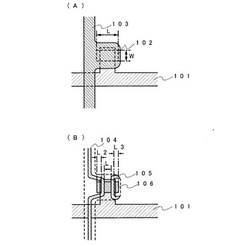

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、工程数削減によるコスト低減を図れる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、第2の被加工膜の上に第2の方向に延びる複数の第2の芯材膜であって、第1のスペースを隔てて第1の方向に並んだ第1の配列部と、第1のスペースよりも大きな第2のスペースを第1の方向に隔てて配置された第2の配列部とを有し、第2のスペースがループ部の上に位置する第2の芯材膜を形成する工程と、第2の芯材膜を除去し第2の被加工膜上に第2のスペーサー膜を残す工程と、第2のスペーサー膜をマスクにしたエッチングにより、第1の配列部の下の第2の被加工膜を、第2の方向に延びる第2のラインパターンを含む第2のラインアンドスペースパターンに加工するとともに、第2のスペースの下の第2の被加工膜と、第1の被加工膜のループ部とを除去する工程とを備える。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

配線レイアウトの設計方法、半導体装置及び配線レイアウトの設計を支援するプログラム

【課題】高集積化を図ることができる配線レイアウトの設計方法、半導体装置及び配線レイアウトの設計を支援するプログラムを提供する。

【解決手段】実施形態に係る配線レイアウトの設計方法は、側壁法によって形成されるレイアウトの設計方法であって、第1の方向に延び、前記第1の方向と交差する第2の方向に第1の周期で配置された複数本の第1のパターン、及び、前記第1の方向に延び、前記第1のパターン間の中央にそれぞれ配置された複数本の第2のパターンが設けられたベースパターンを用意する工程と、1本の前記第2のパターンを挟んで隣り合う2本の前記第1のパターン間に、前記第2の方向に延び、前記2本の第1のパターン同士を接続すると共に、前記1本の第2のパターンを前記2本の第1のパターンと接しない2つのパターンに置き換える工程と、を備える。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

銅および銅合金のエッチング液

【課題】

本発明の課題は、銅層と銅酸化物層および/または銅合金層とを含む金属積層膜パターンを精度良くエッチング加工し、優れた断面形状を形成し、かつ実用性に優れた安定で液寿命の長いエッチング液組成物、およびかかるエッチング液組成物を用いたエッチング方法を提供することにある。

【解決手段】

本発明は銅層と銅酸化物層および/または銅合金層とを有する金属積層膜を、過硫酸塩および/または過硫酸溶液0.1〜80重量%と、りん酸0.1〜80重量%と、硝酸および/または硫酸0.1〜50重量%とを含有するエッチング液組成物であり、さらに塩化物イオンやアンモニウムイオンを加えることで、エッチングレートや断面形状を容易に制御することが可能となるエッチング液組成物またはエッチング方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

21 - 40 / 970

[ Back to top ]