Fターム[5F033XX14]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 密着性改善 (1,147) | 配線と絶縁膜との密着性改善 (441)

Fターム[5F033XX14]に分類される特許

401 - 420 / 441

半導体装置

【課題】多層配線の層間絶縁膜として低誘電率絶縁膜を使用しても、配線と低誘電率絶縁膜との境界部分における応力集中を低減でき、絶縁膜の剥れを抑制でき、さらに放熱能力を向上した配線構造を具備した半導体装置を提供する。

【解決手段】上記の課題を解決した半導体装置は、半導体基板の上方に形成された絶縁膜ILDと、前記絶縁膜内に形成された配線Mと、前記低誘電率絶縁膜内に前記配線と離間して形成された網目状ダミー構造体NDとを具備する。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

【解決手段】 本発明の表面疎水化用組成物は、(A)官能基を有するシラン化合物と、(B)炭素数4〜8のアルコール系溶媒とを含む。

(もっと読む)

金属膜を備えた基板および金属膜の形成方法

【課題】 プリント基板の製造プロセスを簡略化およびその製造コストの低減を可能とする技術を提供すること。

【解決手段】 プラスチックの基板611の上に、めっきシードとしての触媒金属を含有する有機または無機金属化合物を含む溶剤を塗布・乾燥させて金属化合物膜612を形成し、その所望領域に電子線などのエネルギ線613を照射して触媒金属を析出させる。当該照射領域への局所的なエネルギ線照射によりその照射領域のみで金属触媒析出の化学反応が生じ、触媒金属が局所的に析出してパターニングされた金属触媒膜614を得ることができる。また、エネルギ照射された基板611は、表面の溶融により触媒金属を極浅領域に取り込んだり、表面のアブレーションにより触媒金属と基板表面の接触面積が実効的に広くなったり、あるいは化学的改質により基板と触媒金属との結合状態が強固なものとなるので、固着程度が高まり金属触媒膜の剥離が生じ難くなる。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

【解決手段】 本発明の表面疎水化用組成物は、(A)官能基を有するシラン化合物と、(B)ケトン系溶媒とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10上に第1の絶縁膜11を介して形成されたパッド電極12上に、高融点金属層13を形成する。次に、パッド電極12及び高融点金属層13上を含む半導体基板10の表面上にパッシベーション層14を形成し、さらに、樹脂層15を介して支持体16を形成する。次に、半導体基板10をエッチングして、半導体基板10の裏面からパッド電極12に到達するビアホール17を形成する。次に、第2の絶縁膜18を介して、ビアホール17の底部で露出されたパッド電極12と電気的に接続された貫通電極20及び配線層21を形成する。さらに、ソルダーレジスト層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

配線形成方法及び装置

【課題】 例えデザインルールが厳しくなっても、十分な密着性を有する配線材料を電解めっきによって基板の全面に均一に形成して、信頼性の高い埋込み配線を形成できるようにする。

【解決手段】 絶縁膜内に配線用凹部を形成した基板表面に、配線材料成膜用の電解めっき液に対して不溶性の導電膜を形成し、前記導電膜をシード膜として、電解めっき法により該導電膜の表面に配線材料を前記配線用凹部内に埋込みつつ成膜し、前記導電膜の表面に成膜した余剰の配線材料を除去して前記配線用凹部内に埋込んだ配線材料で配線を形成する。

(もっと読む)

フラッシュメモリ素子のソースコンタクト形成方法

【課題】 金属配線およびコンタクト抵抗に優れると同時に、後続の熱処理工程が行われても素子特性の低下を防止することを可能とするフラッシュメモリ素子のソースコンタクト形成方法を提供する。

【解決手段】 本発明のフラッシュメモリ素子のソースコンタクト形成方法は、セル領域のSSL用ゲート電極パターンに備えられた接合領域が形成された半導体基板の全面に層間絶縁膜を形成し、前記層間絶縁膜をパターニングし、前記SSL用ゲート電極パターンの一側で前記接合領域を露出させるソースコンタクトホールを形成する段階と、前記ソースコンタクトホールの形成された結果物の全面にタングステンシリサイド膜の含まれた膜を形成し、前記層間絶縁膜が露出するまで平坦化工程を行い、前記ソースコンタクトホール内にのみ前記タングステンシリサイド膜の含まれた膜が埋め立てられてソースコンタクトを形成する段階とを含む。

(もっと読む)

半導体装置

【課題】非晶質化のために必要な電流(リセット電流)を低減した相変化メモリを提供する。

【解決手段】相変化膜で構成されるメモリセル30と、メモリセル30の下主面にその一端が直接に接続され、他端がMOSトランジスタ10の一方のソース・ドレイン層3に接続されて、当該ソース・ドレイン層3とメモリセル30とを電気的に接続するとともに、メモリセル30の下部電極となるプラグ電極CP1と、メモリセル30の上主面にその一端が直接に接続され、他端がメモリセル30を覆うように配設された層間絶縁膜9上に配設されたビット配線層WRに接続されて、当該ビット配線層WRとメモリセル30とを電気的に接続するとともに、メモリセル30の上部電極となるプラグ電極CP10とを備えている。

(もっと読む)

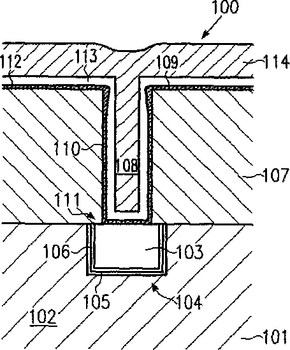

半導体装置及びその製造方法

【課題】絶縁膜−絶縁膜間等の界面における膜剥がれやクラック等による不良が生じない低誘電率膜を用いた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板101上の第1の絶縁膜102に第1の配線106を形成し、第1の絶縁膜102上に第2の絶縁膜107、第3の絶縁膜108、第4の絶縁膜109及び第5の絶縁膜110を順次堆積する。その後、第1の配線106上の第5の絶縁膜110から第2の絶縁膜107までを突き抜ける第1のスルーホール112と第1のスルーホール112につながる第2の配線溝114に第2の配線117を形成し、第5の絶縁膜110から第1の絶縁膜102までを突き抜ける第2のスルーホール120に第1の支柱123を形成する。

(もっと読む)

貫通孔へのメッキ埋め込み方法及びメッキ装置

【課題】貫通孔へのメッキ埋め込み方法及びメッキ装置において、メッキ埋め込み工程の前後に別プロセスを必要とせずに直接貫通孔に金属を埋め込み、また、埋め込み金属中にボイドの発生のない信頼性の高い貫通電極をより高速に形成することを可能とする。

【解決手段】貫通孔3を有する絶縁材料からなる基板1又は表面が絶縁された基板1にメッキを施して貫通孔3の内部に金属4を埋め込むメッキ埋め込み方法であって、第1工程では基板1の表面に金属薄膜2を形成し、第2工程では基板1の面A側の電流密度と面B側の電流密度を異ならせて金属薄膜2にメッキを施し電流密度の高い側の面Aの貫通孔3の開口部をメッキ金属4で塞ぎ、第3工程ではメッキ抑制剤及び又はメッキ促進剤を含むメッキ液を用いるとともに基板1の面A側の電流密度と面B側の電流密度の高低を第2工程とは逆に設定してメッキを施し貫通孔3にメッキ金属4を埋め込む。

(もっと読む)

半導体装置およびその製造方法

【課題】 Cu電極層と有機樹脂膜との密着性寿命を、従来よりも向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 パワーデバイスと、パワーデバイス上の厚いCu電極層2と、Cu電極層2を覆う有機樹脂膜3とを備える半導体装置において、Cu電極層2の表面(上面2aと側面2b)の全領域を覆うように、Cu窒化膜8を配置する。ここで、Cu電極層2と有機樹脂膜3との密着性を低下させる主原因は、有機樹脂膜3を通過した酸素がCu電極層2と反応して、Cu電極層2の表面に酸化膜が生成することである。そこで、Cu電極層2と有機樹脂膜3との間の領域に、酸素の透過を抑制することができるCu窒化膜8を配置することで、Cu電極層と有機樹脂膜との密着性寿命を、従来よりも向上させることができる。

(もっと読む)

触媒を用いた無電解めっきによりパターン化された絶縁体上に金属層を形成する方法

金属層は、触媒により活性化された下地材料の表面領域上に、めっきプロセスによって形成されうる。この触媒はCVD、PVDまたはALDによって堆積されるかまたは下地材料を堆積する際に少なくとも部分的に取り込まれる。このようにして、メタライゼーション構造の高アスペクト比のビアに優れた金属シード層を形成することができる。  (もっと読む)

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】その後の加工プロセスとの整合性を有し、かつ、表面のダメージをより簡便にかつ効率良く修復する事ができる表面疎水化法、ならびに表面のダメージの修復に使用可能な表面疎水化用組成物、及び前記表面疎水化方法によって、表面疎水化処理が施された層を含む半導体装置及びその製造方法、を提供する。

【解決手段】層間絶縁膜20をエッチングして形成された凹部22の内壁22aの表面に、(A)官能基を有するシラン化合物と、(B)有機溶媒と、(C)安定化剤とを含む膜を形成し、前記膜中に含まれるシラン化合物と、前記凹部内壁表面にエッチングで生成されたシラノール基を反応させることによって、前記凹部内壁表面に疎水性膜24を形成した後、凹部内に導電性膜26を充填する。

(もっと読む)

アクティブマトリクス型表示装置およびその製造方法

【課題】 電極の段切れを防止して表示品位の優れたアクティブマトリクス型表示装置およびその製造方法を提供する。

【解決手段】 アクティブマトリクス型表示装置は、接続配線4と、貫通孔33を含む無機絶縁膜21と、コンタクトホール32を含む有機絶縁膜22と、画素メタル電極6とを備える。貫通孔33は、接続配線4の表面においてコンタクトホール32よりも大きくなるように形成され、有機絶縁膜22は、貫通孔33とコンタクトホール32とに挟まれるように形成された介在部31を含む。接続配線4は、表面のうち少なくとも介在部31が接する領域に形成された酸化膜を含む。

(もっと読む)

半導体装置

【課題】 はんだ接続用パッドを有する半導体装置において、製造工程中の熱負荷などによって発生する恐れのある、パッド部の膜剥がれを防止する。

【解決手段】 シリコン、シリコン酸化膜上に形成されるTi膜またはTi化合物膜と、はんだが接続されるNi膜(またはCu膜)との間に、両者との密着性が良好なCr膜を挿入したパッド構造とする。さらに、Ti膜またはTi化合物膜とシリコン酸化膜との界面に生じる剥離を防止するため、Cr膜がTi膜またはTi化合物膜よりも大きな面積で形成された構造とする。

(もっと読む)

半導体装置とその製造方法

【課題】配線上にSiCN膜を有する半導体装置において、SiCN膜から流出する不安定なNによるレジストポイゾニングの発生を低減する。

【解決手段】SiCN膜を有する半導体装置の製造方法において、SiCN膜成膜時に一部に有機基を有する原料ガスとHeの流量比を1:4.2以上にする。または原料ガスの流量×原料ガスの有機基との結合数とHeの流量比を1:1.4以上にする。その結果、SiCN膜中のSiNH基の増加を抑制し、膜ストレス変化とポイゾニング不良の発生を合わせて抑制することが半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 誘電体薄膜と導体層との密着性を高め信頼性の高い配線構造をもつ半導体装置を提供する。

【解決手段】 本発明の方法は、Si−O結合を主成分とする骨格の周りに多数の空孔が配置された誘電体薄膜表面に、反応性プラズマを供給し、前処理を行なう工程と、前記前処理のなされた前記誘電体薄膜表面にスパッタリング法により導電性膜を形成する工程とを含む半導体装置の製造方法であって、前記前処理工程に先立ち、前記誘電体薄膜表面に、テトラメチルシクロテトラシロキサン(TMCTS)、ヘキサメチルシラザン(HMDS)、トリメチルクロロシラン(TMCS)分子のうちの少なくとも1種を含むガスを接触させる工程とを含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【目的】 層間絶縁膜が剥離または破壊される事態が起こりにくい半導体装置の製造方法を提供することを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜上に導電性材料を堆積させる堆積工程(S114〜S118)と、堆積した前記導電性材料を所定の深さまでウェットエッチングするウェットエッチング工程(S120)と、ウェットエッチングされた前記導電性材料を研磨する研磨工程(S122)と、を備えたことを特徴とする。

(もっと読む)

配線基板の製造方法

【課題】 微細配線を実現することができる「配線基板の製造方法」を提供すること。

【解決手段】 ダマシンプロセスを用いた配線形成工程を含む配線基板の製造方法において、下層配線層10上に形成された層間絶縁層11に、下層配線層11に達するビアホールVHを形成し、その際に生じたスミアSMを除去した後、層間絶縁層11上に、ビアホールVHの上方に位置する所要の配線パターンの形状に従う開口部(配線溝)OPを有するように感光性永久レジスト層12を形成する。次に、全面にシード層13を形成し、ビアホールVH及び開口部(配線溝)OPの内部を充填するようにしてシード層13上に導体層14を形成した後、感光性永久レジスト層12が露出するまで導体層14の表面を研磨して平坦化し、配線パターン15を形成する。

(もっと読む)

401 - 420 / 441

[ Back to top ]