Fターム[5F038AC15]の内容

Fターム[5F038AC15]に分類される特許

41 - 60 / 762

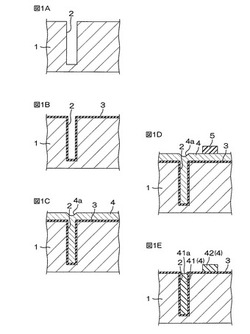

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

プラズマ処理方法、記憶媒体及びプラズマ処理装置

【課題】高誘電率絶縁膜のエッチング制御性を向上することができるプラズマ処理方法を提供する。

【解決手段】ウエハW上の半導体デバイスに形成されたハフニウム酸化膜にエッチング処理を施す際、ウエハWをプラズマ処理装置10のチャンバ11内に搬入し、該チャンバ11内の処理空間SにC4F8ガス、一酸化炭素ガス、アルゴンガス及びキセノンガスを所定の流量比で供給し、処理空間Sに高周波電力を印加して供給された処理ガスからプラズマを発生させ、キセノンによってC4F8からのフッ素の解離をより促進して高いエッチレートで高誘電率絶縁膜をエッチングする。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】半導体装置に用いられるキャパシタを効率よく、しかも少ない占有床面積で行うことができる半導体装置の製造方法および基板処理装置を提供する。

【解決手段】基板200上に下電極を形成する工程(S104)と、下電極の上に、それぞれ異なる金属元素を含む3種の金属酸化膜を積層して誘電膜を形成する工程(S106、S108、S110)と、誘電膜の上に、上電極を形成する工程(S112)と、を有し、各工程は同一の装置で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

電子装置およびその製造方法

【課題】半導体基板に設けられた貫通穴に、絶縁体を介して2つの導電体を充填してなるキャパシタ構造体を有する電子装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の表裏両主面11、12間を貫通する貫通穴30には、当該穴の内面側から第1の導電体40、絶縁体50、第2の導電体60が順次充填されてキャパシタ構造体20が形成されており、キャパシタ構造体20は、貫通穴30の内部から半導体基板10の両主面11、12まで連続して形成され、キャパシタ構造体20の静電容量は、キャパシタ構造体20のうち貫通穴30に位置する部位の容量と両主面11、12に位置する部位の容量との合計とされている。

(もっと読む)

酸化プラセオジムを備えた誘電体、酸化プラセオジムを備えたトランジスタ及びその製造方法

【課題】酸化プラセオジムの誘電体、酸化プラセオジムを備えたトランジスタ及びその製造方法を提供し、以って半導体素子のリーク電流及び等価酸化物膜厚の過大の問題を解決すること。

【解決手段】本発明では、酸化プラセオジムを備えたトランジスタは、少なくとも一つのIII−V族基板と、一つのゲート誘電層と、一つのゲート電極とを含む。また、III−V族基板にゲート誘電層が設けられ、ゲート誘電層にゲート電極が設けられ、誘電層は酸化プラセオジム(PrxOy)である。本発明は、誘電層材料として高誘電率及び高エネルギーギャップを備えた酸化プラセオジム(Pr6O11)を用いることにより、リーク電流を有効に抑制する外、更にIII−V族材料を基板とした素子の等価酸化膜厚(EOT)を薄くさせることもできる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

周波数特性の調整方法、半導体装置の製造方法及び半導体装置

【課題】寄生容量が回避できないSi半導体基板上に集積回路と一緒に製造するオンチップアンテナにおいて、その周波数特性をウエハプロセス製造工程後に自在に所望値へ制御する。

【解決手段】Si半導体基板に対して第1のプロセスで形成される集積回路部及びアンテナ部を備える半導体装置において、該アンテナ部の周波数特性を調整する方法であって、アンテナ部と集積回路部との間に非連続的な複数の導線パターンを前記第1のプロセスにおいて形成し、第1のプロセスの終了後に、複数の導線パターンの一部又は全部を選択して、選択した前記導線パターンが直列的となるようにボンディングワイヤを懸架する。

(もっと読む)

コンデンサとその製造方法ならびに多層配線基板

【課題】簡便・安価に製造可能な浮遊インダクタンスの小さいコンデンサ部品と、その製造方法を提供する。また、前記コンデンサ部品を低背化した部品と、その低背コンデンサを内蔵した多層配線基板を提供する。

【解決手段】有機材料の単分子膜を誘電体とするコンデンサにおいて、コンデンサ用電極のうち少なくとも一つが、誘電体単分子膜に担持された触媒物質によって開始する無電解めっきで形成されることを特徴とするコンデンサ。コンデンサを支持基材の上に形成することで、薄膜コンデンサを部品として扱うことが可能となる。また、前記支持基材を薄く研削することで、部品の低背化が可能となる。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】本発明は、大容量化及び小面積化の要請に応えつつ、電圧依存性の低いキャパシタ装置及びその製造方法を提供することを目的とする。

【解決手段】シリコン31、32からなる下部電極30上に、容量絶縁膜40と上部電極50が順次積層形成されたキャパシタ装置であって、

前記下部電極は、互いに導電極性の異なるN型領域20とP型領域10とが所定比率で混在配置されているとともに、前記N型領域の表面が前記P型領域の表面よりも窪んだ凹凸構造を有することを特徴とする。

(もっと読む)

化合物半導体装置

【課題】容量耐性を高めると共に信頼性の向上を図った容量付PDを提供する。

【解決手段】PD、ダイオードを含む素子と複数のMIM容量を基板上に集積した化合物半導体装置において、前記素子からの引き出し配線とMIM容量の下部配線を結ぶ線を第1配線、MIM容量の上部電極とボンディングパッドを結ぶ線を第2配線としたときに前記第1配線と第2配線をスルーホールで接続し、MIM容量に印加する電圧方向を1方向に揃えるように、MIM容量の上下メタルに電圧を印加した。

(もっと読む)

誘電体薄膜形成用組成物、誘電体薄膜の形成方法及び該方法により形成された誘電体薄膜

【課題】薄膜キャパシタ等において、チューナビリティ、リーク電流特性及び誘電率を向上させ得る誘電体薄膜形成用組成物、誘電体薄膜の形成方法及び誘電体薄膜を提供する。

【解決手段】一般式:Ba1-xSrxTiyO3(式中0.2<x<0.6、0.9<y<1.1)で示される複合金属酸化物Aに、Cu(銅)を含む複合酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、複合金属酸化物Aを構成するための原料及び複合酸化物Bを構成するための原料が上記一般式で示される金属原子比を与えるような割合で、かつAとBとのモル比B/Aが0.001≦B/A<0.15の範囲内となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】キャパシタ装置及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ装置10は、第1導電型を有して第1電圧が印加される第1ウェル105及び第2導電型を有して第2電圧が印加される第2ウェル110を有する基板100、及び第1または第2ウェル105,110と絶縁されるように第1または第2ウェル105,110の上部に配されたゲート電極126を含み、キャパシタ装置10のキャパシタンスは、第1ウェル105と第2ウェル110との間の第1キャパシタンス及び第1または第2ウェル105,110とゲート電極126との間の第2キャパシタンスを含む。

(もっと読む)

薄膜キャパシタの製造方法及び該方法により得られた薄膜キャパシタ

【課題】薄膜キャパシタにおける諸特性低下の原因となるヒロックを抑制し、リーク電流特性及び絶縁耐圧特性に優れた薄膜キャパシタを製造する。

【解決手段】下部電極を形成した後、300℃よりも高い温度のアニール処理を行わずに薄膜形成前駆体溶液を下部電極上に塗布し、乾燥は室温〜450℃の範囲内の所定の温度で行い、焼成は乾燥温度よりも高い450〜800℃の範囲内の所定の温度で行い、塗布から焼成までの工程は塗布から焼成までの工程を1回又は2回以上行うか或いは塗布から乾燥までの工程を2回以上行った後、焼成を1回行い、初回の焼成後に形成される誘電体薄膜の厚さは20〜600nmにする。下部電極の厚さと初回の焼成後に形成される誘電体薄膜の厚さの比(下部電極の厚さ/誘電体薄膜の厚さ)は0.10〜15.0の範囲とするのが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

41 - 60 / 762

[ Back to top ]