Fターム[5F038AC15]の内容

Fターム[5F038AC15]に分類される特許

121 - 140 / 762

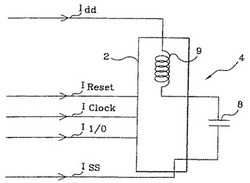

電子シグニチャーの減衰により安全保護された集積回路デバイス

【課題】集積回路デバイスの電子シグニチャーの解析をより複雑にすることにより、秘密データへのアクセスを防止する。

【解決手段】本発明は、メモリーを有するポータブルメモリ媒体、特にカード形式に組込むように設計された集積回路デバイス(2)に関する。集積回路デバイス(2)は、集積回路デバイス(2)により消費される電流のピーク(Idd)の振幅を減衰させるための少なくとも1つのキャパシター(8)を備える。本発明は、スマートカードの電気的シグニチャーを減衰させるのに特に有用である。

(もっと読む)

半導体装置

【課題】一定の静電容量を確保すると同時に、小型化を図ることが可能なキャパシタを備える半導体装置を提供する。

【解決手段】半導体装置は、金属膜を含むキャパシタ下部電極3aと、キャパシタ下部電極3aの上部表面上に配置され、キャパシタ下部電極3aの厚みより薄い厚みを有する誘電体膜4aと、誘電体膜4a上に配置され、金属膜を含むキャパシタ上部電極6aと、キャパシタ上部電極6aと同一レベルの層により構成される下部配線部分6bと、下部配線部分6b上に配置される層間絶縁膜8と、層間絶縁膜8上に配置される上部配線部分12bとを備える。

(もっと読む)

薄膜キャパシタ

【課題】バンプ等の外部接続端子に働く鉛直方向の応力が電極層に集中しない構造を有するとともに、等価直列抵抗を所望の値に増加させることが容易な薄膜キャパシタとその製造方法を提供する。

【解決手段】基板と、前記基板上に形成され少なくとも1層の誘電体薄膜と少なくとも2層の電極層からなるキャパシタ部と、前記キャパシタ部の少なくとも一部を覆う保護層と、前記キャパシタ部のいずれかの電極層と電気的に接続する引き出し導体と、前記引き出し導体上に形成されたバンプと、を備え、前記引き出し導体は、前記保護層に形成された開口部内に形成されて前記キャパシタ部のいずれかの電極層と電気的に接続する接続部と、前記保護層上に延伸された引き回し部とからなり、前記バンプは前記引き回し部上に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化によってキャパシタが小型化された場合であっても、キャパシタの実効的なキャパシタ容量の低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】下部電極に形成した凹部開口の内周面を含む下部電極上に誘電膜を形成し、凹部開口内を含む誘電膜上に下部電極と対向する上部電極を形成する。さらに、下部電極を、第1導電膜と、絶縁膜と、不純物がドープされた低抵抗の第2導電膜とを順次積層して形成し、第1導電膜と第2導電膜とを接続する。

(もっと読む)

電子装置とその製造方法

【課題】

電子装置とその製造方法を提供する。

【解決手段】

電子装置は、ガラス基板と、少なくとも一つの開口を有し、ガラス基板上に設置されるパターン化半導体基板と、第一導電層と第二導電層を有し、第一導電層が、パターン化半導体基板とガラス基板間に設置される少なくとも一つの受動素子と、からなる。

(もっと読む)

半導体装置

【課題】 入出力部の電源配線の近傍にバイパスコンデンサを配置する場合、LSIの端子数が多くなると、バイパスコンデンサを配置するための領域を確保することが困難になる。

【解決手段】 半導体基板の表面に、電子回路素子が形成されている電子回路領域が画定される。半導体基板の上に、一方に基準電位が印加され、他方に電源電圧が印加される第1及び第2の配線が配置される。シールリングが、電子回路領域を取り囲むように、半導体基板の上に配置される。シールリングは、第1の配線に電気的に接続される。第1の不純物拡散領域が、シールリングよりも内側において、半導体基板の表層部に形成される。第1の不純物拡散領域の上に誘電体膜が配置される。誘電体膜の上に、シールリングに電気的に接続され、導電材料で形成されたキャパシタ導電膜が配置される。

(もっと読む)

高周波デバイス

【課題】 渦電流や寄生容量の発生を抑制することができ、優れた高周波特性を示す小型の高周波デバイスを提供する。

【解決手段】 開口14を有する基板11上の誘電体層13にバンドパスフィルタBPFを備える。BPFは例えば第1誘導性素子L1および第1容量性素子C1の組と、第2誘導性素子L2および第2容量性素子C2の組と、第3誘導性素子L3および第3容量性素子C3の組とにより構成されている。開口14は第1誘導性素子L1に対向する位置に設けられている。基板11に対して開口14を設けることにより第1誘導性素子L1の直下での寄生容量および渦電流の発生が抑制され、これにより信号損失が低減されてフィルタ回路の特性が向上する。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

円筒型キャパシタを備えたウェーハレベルパッケージ及びその製造方法

【課題】円筒型キャパシタ構造を採用することにより、静電容量を増大させることが可能な構造を有する円筒型キャパシタを備えたウェーハレベルパッケージ及びその製造方法を提供する。

【解決手段】上面にボンディングパッド104を備え、ボンディングパッド104を露出させる絶縁層106が形成されたウェーハチップ102と、ボンディングパッド104に連結された状態で絶縁層106の一側に延長される再配線層108と、再配線層108に連結され、内部に中空部を有する円筒状の外部電極114bと、中空部内に外部電極114bと分離されるように形成された円筒状の内部電極114aと、外部電極114bと内部電極114aとの間に形成される誘電体層116と、再配線層108、内部電極114a、外部電極114b及び誘電体層116をカバーするように絶縁層106に形成され、内部電極114aの上面を露出させる第1オープン部120aを有する樹脂封止部118とを含んでなる。

(もっと読む)

半導体装置

【課題】 求められる特性が異なる複数のキャパシタを同一基板上に混載するには、さらなる工夫が必要とされる。

【解決手段】 下部電極、上部電極、及び両者の間に配置された誘電体膜を含む下層キャパシタが、半導体基板の上に配置されている。第1の層間絶縁膜が、第1のキャパシタを覆う。複数の上層キャパシタが、第1の層間絶縁膜の上に配置されている。上層キャパシタは、下部電極、上部電極、及び両者の間に配置された誘電体膜を含み、平面視において、下層キャパシタに重なる。半導体基板の上に、上層キャパシタに対応して複数のトランジスタ配置されている。トランジスタは、上層キャパシタとともにメモリセルを構成する。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

高い絶縁破壊電圧の埋め込まれたMIMキャパシタ構造体

高い絶縁破壊電圧の埋め込まれた複数のキャパシタに関連する方法及び装置が提供される。半導体装置は、絶縁体(209)に埋め込まれたゲート材料(204)、複数の金属接触部(213)及び複数のキャパシタ(C1−C4)を含み得る。複数のキャパシタは、下部電極(217)、下部電極の表面を覆うように形成される誘電体(219)及び誘電体に形成される上部電極(221b、c)を含み得る。さらに、複数の接触部は、複数のキャパシタの下部電極の各々をゲート材料に接続し得る。複数のキャパシタは、ゲート材料を介して直列に接続され得る。  (もっと読む)

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

半導体装置および電子機器

【課題】高速動作に適したN型層を用いたN型TFTを液晶容量と、蓄積容量の充電に用いる場合には、リーク電流特性に劣るN型層を蓄積容量に用いることとなり、電荷保持特性が低下するという課題がある。またP型層を用いたP型TFTを液晶容量と、蓄積容量の充電に用いた場合には、P型TFTがN型TFTと比べ移動度が低いことから高速動作が困難となり、TFTによるスイッチング特性が劣化するという課題がある。

【解決手段】N型TFT90をスイッチングに用い、P型電極層41を保持容量として用い、かつP延展部40と、N型ドレイン側延展部1tとを切り離すことなく形成した。P延展部40と、N型ドレイン側延展部1tとの間には段差はなく、コンタクトホール94を形成するためのエッチング工程を均一な層厚を備えた第1層間絶縁層4に対して行うことができ、エッチングむら等による電気抵抗の増加を防止することが可能となる。

(もっと読む)

電子素子及び電子素子の製造方法

【課題】簡易な構成でリーク電流の抑制された電子素子及びその製造方法を提供する。

【解決手段】基板上に設けられ、Mo−Nb合金から構成された第1の電極と、前記第1の電極上に配置された絶縁膜と、前記第1の電極に対して少なくとも前記絶縁膜を介して配置された第2の電極と、を備えた電子素子とする。

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁耐圧を向上し、接続プラグのリセスをなくすための高度な平坦化を不要にし、メモリの高集積化も可能にした、半導体装置及びその製造方法を提供する。

【解決手段】基板2と、駆動素子3と、駆動素子3に電気的に接続する第1プラグ8と、基板2の上方に形成されて、電極本体部14aの外側に延在してなる電極延在部14bの底面側で、第1プラグ8に電気的に接続する下部電極14と、下部電極14の電極本体部14a上に形成された強誘電体本体部15a、及び下部電極14の電極延在部14b上に、強誘電体本体部15aより薄厚に形成されてなる強誘電体延在部15b、からなる強誘電体膜15と、強誘電体膜15の強誘電体延在部15b上に形成されることなく、強誘電体本体部15a上に形成された上部電極16と、上部電極16に導通して形成された第2プラグ19と、を含む半導体装置1。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】寄生抵抗、寄生容量を低減する。

【解決手段】基板に、第1配線層111と、前記第1配線層111の上層に層間絶縁膜132と、前記層間絶縁膜132の上面に開口部を有し前記層間絶縁膜にホール112Aと、前記ホール112A内壁面を被覆する第1金属層112と、前記第1金属層112で被覆されたホール112A内に第2金属層113と、前記第1金属層112の上層に誘電絶縁膜135と、前記誘電絶縁膜135の上層に第2配線層114−116と、を備え、前記ホール112A内壁面を被覆する第1金属層112が前記誘電絶縁膜135下層の下部電極の少なくとも一部を形成し、前記第2配線層114−116の前記下部電極に対向する部分が前記誘電絶縁膜上層の上部電極P1を形成し、前記下部電極、誘電絶縁膜135および上部電極P1によってコンデンサ160が形成されている。

(もっと読む)

121 - 140 / 762

[ Back to top ]