Fターム[5F038AC15]の内容

Fターム[5F038AC15]に分類される特許

21 - 40 / 762

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

静電容量素子

【課題】 生産性に優れる温度補償型の静電容量素子を提供する。

【解決手段】 静電容量素子10は、基板20と、基板20の上に位置する第1コンデンサ30と、基板20の上に位置して第1コンデンサ30と電気的に並列接続されている第2コンデンサ40とを有し、第1コンデンサ30は、第1下部電極31と第1誘電体32と第1上部電極33とで構成され、第2コンデンサ40は、基板20側から順に第1下部電極31と異なる材料からなる第1層41xと、第1下部電極31と同じ材料からなる第2層41yとが積層されてなる第2下部電極41と、第1誘電体32と同じ組成の材料からなる第2誘電体42と、第2上部電極43とで構成され、温度が上昇する際の第1コンデンサ30の静電容量の変化量と第2コンデンサ40の静電容量の変化量とで変化の正負が異なっている。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

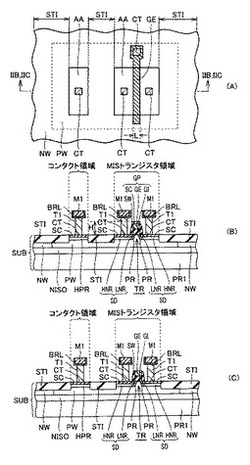

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供する。

【解決手段】半導体装置2は、半導体チップ10と、半導体チップ10の表面10Tに形成された電子回路と、半導体チップ10の少なくとも1つの側面10L、10Rに形成され、半導体チップ10側から内部電極21と絶縁膜22と外部電極23との積層構造を有するMIMキャパシタ20とを備えている。半導体装置2は、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

無線通信デバイス、受動素子の製造方法、及び無線通信機器

【課題】高周波回路のワンチップ化を実現し、上層回路と下層回路との間におけるアイソレーション特性を向上し、かつ量産性の高い無線通信デバイスを提供する。

【解決手段】RFICと、キャパシタ32と、インダクタ24とが積層配置され、キャパシタ32の少なくとも一部がRFICとインダクタ24との間に位置するようにして前記RFICに対して積層して実装される受動素子チップ12と、を備えることを特徴とする。このような特徴を有する無線通信デバイスでは、受動素子チップ12は、キャパシタ32の上部電極26を構成する金属パターンとインダクタ24を構成する金属パターンとを横並びに備え、キャパシタ32の下部電極を構成する下層金属パターン18をインダクタ24を構成する金属パターンの下部にまで延設して構成すると良い。

(もっと読む)

半導体装置およびその製造方法

【課題】同一半導体基板上に、トランジスタ素子、及び、容量素子、及び、抵抗素子を有する半導体装置において、十分な機能を有する容量素子を提供する。

【解決手段】容量素子をアクティブ領域上、抵抗素子を素子分離領域上に同一の多結晶シリコンで形成した後、CMPやエッチバック等で、所望の抵抗体の膜厚になるまで、基板表面を平坦化させながら削る。この時、アクティブ領域と、素子分離領域との高さの違いによって、膜厚の薄い抵抗素子と、膜厚の厚い容量素子の上部電極が形成される。容量素子の上部電極が十分な膜厚を持つので、コンタクトの突き抜けや、高抵抗化に伴う電圧依存性の増加などの特性劣化が防止され、アナログ回路に必要な高抵抗素子とプロセスを共通化することが可能であり、かつ、十分な機能を有する容量素子を製造することができる。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

MEMSアクチュエータおよび可変容量素子

【課題】スティッキングによる可変容量素子の動作不良を防ぎ、また、特性ばらつきを抑える。

【解決手段】可変容量素子1は、固定板2と可動板3と誘電体膜8と電極4A,4B,5A,5B,6,7A,7Bとを備える。電極5A,5B,7A,7Bは対向し、駆動電圧が印加される。誘電体膜8は、電極5A,5B,7A,7Bに対向する領域8Cが周囲よりも薄肉で、領域8Cを挟むように周囲から突出する2列のストッパ8Aを備える。ストッパ8Aの間隔は狭く、可動板3のヤング率は高く、可動板3の厚みは厚く、駆動電圧は低く、ストッパ高さは高いことが望ましい。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

半導体装置およびそれを用いた発光装置

【課題】 層間絶縁膜を挟んでゲート電極と容量電極が対向してできる容量の占有面積を小さくする。

【解決手段】 チャネル領域上の層間絶縁膜が周囲よりも膜厚が薄く、その部分で容量電極がゲート電極と対向して容量を形成している半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子について、レイアウト面積の増大を防ぎつつ、周辺の電荷の影響を受けずに安定した抵抗値を得ることができ、しかも、抵抗体に印加できる電位の極性に制限のない半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1上のLOCOS酸化膜3上に形成された抵抗素子10と、を備え、抵抗素子10は、LOCOS酸化膜3上に形成されたシールド用ポリシリコン膜11と、シールド用ポリシリコン膜11上に形成されたシリコン酸化膜13と、シリコン酸化膜13上に形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15の一方の端部に接合された第1の電極21と、ポリシリコン抵抗体15の他方の端部に接合された第2の電極22と、シールド用ポリシリコン膜11に接合された第3の電極23と、を有し、第1の電極21及び第2の電極22うちの一方が、配線25を介して第3の電極23と電気的に接続されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スタック構造かつMIM構造の容量素子を備える構成において、容量素子を構成する各電極に配線をつなぐための複数のビアホールを形成する工程の簡略化を図ることができる半導体装置の製造方法および半導体装置を提供すること。

【解決手段】下部電極3の表面に第1容量膜4を形成し、第1容量膜4の表面の第1領域Aに中間電極5を形成し、中間電極5の表面に第2容量膜6を形成する。第2容量膜6を挟んで中間電極5に対向し、第2領域Bで第1容量膜4を挟んで下部電極3に対向する上部電極7を形成して、第2領域Bにおける上部電極7に貫通孔35を形成し、絶縁層8を形成する。貫通孔35の位置で絶縁層8および第1容量膜4を貫通して下部電極3に達する第1のビアホール23と、第1領域Aにおいて上部電極7がない部分で絶縁層8および第2容量膜6を貫通して中間電極5に達する第2のビアホール24とを同時に形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

コンデンサ及びその製造方法

【課題】金属−絶縁体−金属コンデンサや、内部接続構造の金属間誘電体として使用して、その素子や構造の平均故障寿命を改善できる誘電体構造を提供すること。

【解決手段】酸化膜層、誘電体材料層及び誘電体材料層の上に第2酸化膜層を有する、炭化ケイ素用のコンデンサ及び内部接続構造が提供される。酸化膜層の厚みは、酸化膜層と誘電体材料層の約0.5から約33パーセントであってよい。誘電体構造として酸窒化ケイ素層を有する炭化ケイ素用のコンデンサおよび内部接続構造もまた提供される。こうしたコンデンサ及び構造を作製する方法もまた提供される。

(もっと読む)

演算増幅器、駆動回路、駆動装置、および画像形成装置

【課題】演算増幅器(回路)には発振防止等の特性改善のために位相補償用のコンデンサを備える。MOS集積回路ではMOS容量を用いることが一般的であるが、特性が不安定、かつ大きな静電容量値がとれないという問題があった。もしくはこれを回避するためにコストアップをもたらす濃いイオン打ち込みの新たな製造工程を必要とした。

【解決手段】MOSトランジスタ、ダイオードでバイアス電圧を発生させ、コンデンサの両端にMOS容量がMOSトランジスタとしてみた場合に常時オンしている状態に相当する電位を与えて、MOS容量直下における空乏層の発生をおさえることにより、広い動作電圧範囲において、大きな容量値と安定した特性をコスト増加なしに実現する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】実用上限温度をより向上させた炭化珪素半導体装置の製造方法を提供する。

【解決手段】ゲート窓6が形成された炭化珪素基板1の表面に、前駆酸化シリコン膜を成膜する工程と、前駆酸化シリコン膜を酸化窒素ガス雰囲気で熱処理して第1の酸化シリコン膜(O)とする工程と、窒化シリコン膜(N)を積層する工程と、窒化シリコン膜を酸化させて、表面から所定の深さまで第2の酸化シリコン膜(O)を形成して、ONO絶縁膜を形成する工程と、ONO絶縁膜の上にゲート電極を形成する工程とを備える。ゲート電極を形成する工程は、ONO絶縁膜の上に多結晶シリコン膜を成膜する工程と、所望のマスクを用いて、多結晶シリコン膜、第2の酸化シリコン膜、窒化シリコン膜、を連続的にエッチングして、ゲート電極と第2の酸化シリコン膜と窒化シリコン膜の外縁を定義する工程と、ゲート電極の側面及び上部と窒化シリコン膜の外縁を酸化する工程を備える。

(もっと読む)

21 - 40 / 762

[ Back to top ]