Fターム[5F044LL01]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160)

Fターム[5F044LL01]の下位に属するFターム

基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL01]に分類される特許

1,041 - 1,060 / 1,142

配線基板

【課題】接続パッドを外部電気回路基板の端子パッドに導体バンプを介して長期にわたって確実に電気的接続させておくことが可能で、特に絶縁基体と外部電気回路基板との熱膨張係数の差による応力が大きくなっても、その接続を確保することが可能な、外部電気回路基板に対して高い電気的な接続信頼性を有する配線基板を提供する。

【解決手段】絶縁基体1と、絶縁基体の内部に形成された配線導体2と、絶縁基体1の主面に配線導体2と電気的に接続されて形成された接続パッド3と、絶縁基体1の主面に接続パッド3aの周縁部を跨るようにして形成された非貫通の穴5と、穴の内側面に形成された導体層とを有した配線基板。

(もっと読む)

半導体装置

【課題】熱膨張による熱ストレスが生じてもはんだバンプの断線や半導体チップのはがれのない信頼性の高いBGA構造の半導体装置を提供する。

【解決手段】積層された複数の絶縁層13、該複数の絶縁層それぞれの上面に設けられた複数の配線9、および異なる絶縁層上面に設けられた複数の配線を電気的に接続するために絶縁層に設けられた複数のビアホール12からなるBGA基板1と、前記複数の配線にそれぞれ接続される複数の電極を有する半導体チップ2とを含んでなる半導体装置であって、前記複数の絶縁層の材料が、半導体装置が実装される実装基板の熱膨張特性にあわせられた有機系材料からなる半導体装置。

(もっと読む)

半導体パッケージのプリント配線板への接続方法

【課題】信頼性をもって容易に操作できる半導体パッケージと配線板の電気接続方法。

【解決手段】はんだバンプ2を有するバンプアレイパッケージ1の表面に熱流動性でかつ熱硬化性の接着フィルム3を配置し、前記はんだバンプと前記接着フィルムとからなる平坦な表面を有するバンプアレイパッケージを形成すること、前記はんだバンプと接着フィルムとからなる平坦な表面を配線板5上に配置し、前記接着フィルムの硬化を完了させるのに十分な温度であってかつ前記はんだの融解温度より高い温度に加熱することで、バンプアレイパッケージを配線板に接続するバンプアレイパッケージを配線板に電気接続するための方法。

(もっと読む)

電子部品の超音波実装方法

【課題】 超音波振動を利用して電子部品を回路基板に実装する際の回路基板の振動を抑制して、電子部品を確実に回路基板に実装可能とする。

【解決手段】 電極端子22が設けられた回路基板20に、超音波振動を半導体チップ10に印加してフリップチップ接続により半導体チップを搭載する電子部品の超音波実装方法において、前記半導体チップ10に超音波振動を印加した際に、前記回路基板20に伝達される振動の振幅が最大となる位置に合わせて前記回路基板20を押さえて半導体チップ10を実装する。

(もっと読む)

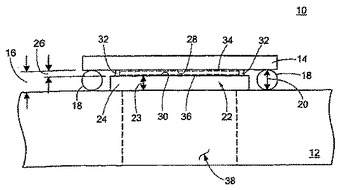

離間した突き当て型コンポーネント構造体

離間した突き当て型コンポーネント構造体であって、このものは、第1のプレートと、第1の間隙によって第1のプレートから離間させられた第2のプレートと、これらプレート同士を相互接続すると共に第1の間隙を形成している複数のハンダバンプとを具備してなり、上記プレートの少なくとも一方は、上記第1の間隙とは異なるサイズを有する第2の間隙を形成するために、隆起したプラットホームおよび凹部のうちの一方を含む特異セクションを有している。  (もっと読む)

(もっと読む)

電子部品及びその製造方法

【課題】 信頼性の高い電子部品及びその製造方法を提供する。

【解決手段】 セラミックスで形成されたパッケージ基板20と、この上に搭載されるデバイスチップ10と、パッケージ基板20とデバイスチップ10との間に設けられた気密封止用のはんだめっきフィルム30とを有し、はんだめっきフィルムは、樹脂で形成されたベース36と、ベース全体を覆うはんだ層38とを有する。はんだめっきフィルム30は、デバイスチップ10の外周表面部分とパッケージ基板20の外周表面部分とに接触している。

(もっと読む)

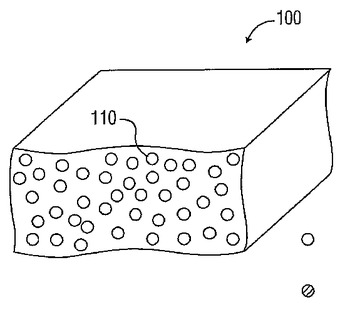

集積回路のためのカーボンナノチューブを基材とする充填材

チップおよびパッケージ型式基板を有する集積回路チップ構造の種々の特性を助長する。種々の実施例において、カーボンナノチューブ充填材料(110)を、集積回路チップ(220,340)とパッケージ型基板(210,350)と間の構成に使用する。カーボンナノチューブ充填材料は、パッケージの封入(モールド化合物(330)として)、ダイ接着(374)、フリップチップのアンダーフィル(240)など多様な用途に使用される。カーボンナノチューブは、強度、熱伝導性、導電性、耐久性、流動性など、多様な特性を助長する。  (もっと読む)

(もっと読む)

イメージセンサー用電子パッケージおよびそのパッケージング方法

半導体素子パッケージおよびその製造方法が提供される。半導体素子パッケージは大体少なくとも一つの半導体ダイおよび半導体ダイに結合された基板を含む。半導体ダイには密閉領域を定義する前面側および該前面側上に形成された第1ソルダ密閉リングパッドが提供される。基板には第2ソルダ密閉リングパッドが形成された半導体ダイの前面側に対向する前面表面が提供される。ソルダ密閉リング構造は密閉領域の実質的な部分の周囲から周辺に延長され、半導体ダイと基板との間でそこの空洞を実質的に囲むように基板および半導体ダイの第1および第2ソルダ密閉パッドの間に介在される。ソルダ密閉リング構造は基板と半導体ダイのうち少なくとも一つに対して空洞と開放通風される空気通路を定義する少なくとも一つの通路部分を含む。 (もっと読む)

半導体装置およびその製造方法

【課題】 ポストの配置や形状を変えることなくチップの向きを一目瞭然にすることができる半導体装置およびその製造方法を実現する。

【解決手段】 ダイシングにより切削されたチップ周辺の各側面の内、一辺の任意の箇所だけに切り欠き部50を有し、それ以外には帯状に残留して露出する金属層30を形成する。このようにすれば、金属層30が露出していない切り欠き部50がチップの向きを表すマークとして機能するようになる。この結果、ポストの配置や形状を変えることなくチップの向きを一目瞭然にすることができる。

(もっと読む)

熱エネルギー放散を改善したプリント回路板組立体

PCB上に実装された集積回路(IC)を備えるプリント回路板(PCB)組立体の熱伝導度を改善する方法と装置である。空所がPCB内に形成され、除去された部分の回路基板の熱伝導度より高い熱伝導度を有するデバイスまたは材料が空所内に配置される。また、PCBは少なくとも1つの回路トレースを含み、ICダイは、その上の電気的接触パッドをPCBの回路トレースと相互接続する少なくとも1つの電気的相互接続によってPCBに相互接続される。空所内に相対的に高い熱伝導度を有する材料を配置することによって、熱ネルギー放散効果が改善される。  (もっと読む)

(もっと読む)

フリップチップ実装方法及びフリップチップ実装体

【課題】 次世代LSIのフリップチップ実装に適用可能な、生産性及び信頼性の高いフリップチップ実装方法及びフリップチップ実装体を提供することにある。

【解決手段】 複数の電極端子11を有する配線基板10上に、はんだ粉及び対流添加剤12を含有する樹脂13を供給した後、樹脂13の表面に複数の接続端子21を有する半導体チップ20を当接させる。この状態で、配線基板10を、はんだ粉が溶融する温度に加熱する。加熱温度は、対流添加剤12の沸点よりも高い温度で行なわれ、沸騰した対流添加剤12は樹脂13中を対流する。この加熱工程において、溶融したはんだ粉を、配線基板10の電極端子11と半導体チップ20の接続端子21との間に自己集合させることによって、電極端子11と接続端子21とを電気的に接続する。最後に、樹脂13を硬化させて、半導体チップ20を配線基板10に固定する。

(もっと読む)

電気接点を有する基板及びその製造方法

第1金属接点パッド(13a〜13d)を有する第1基板(10)を提供するものであり、第1接点パッド(13a〜13d)は第2基板(20)上の第2接点パッド(23a〜23d)とはんだ付けされるものである。本発明によれば、前記第1基板の第1表面に対する、前記第1接点パッド(13a〜13d)の最大平面伸張長さ(Din)が20μmを超えないようにする。このように、第1基板(10)及び第2基板(20)が互いにはんだ付けされると、0またはほぼ0のスタンドオフ距離Xinを達成することができる。この方法は例えば、「アンダーバンプメタライゼーション(UBM)」及び、「はんだ浸漬バンピング(ISB)」が、前記第1基板(10)の製造に用いられるフリップチップ技術に適用することができる。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の実装構造、及び半導体装置の実装方法

【課題】 隣り合うバンプ間でのマイグレーションによる電流リークやショートを防止し、これによってバンプの狭ピッチ化を可能にした半導体装置と、これを用いた半導体装置の実装構造、及び半導体装置の実装方法を提供する。

【解決手段】 少なくとも一方の面に複数のバンプを形成した半導体チップ3を有してなる半導体装置1である。バンプ2、2間に、バンプ2の上面を覆うことなくバンプ2、2間の間隙を埋めるように絶縁層4が形成され、絶縁層4の上面に凹部5が形成されている。

(もっと読む)

異方性導電フィルムを用いた電気部品の接続方法

【課題】 接続信頼性を大幅に向上させたACF接続構造を実現する。

【解決手段】 電子部品8と配線基板9の電極間の接続を従来の導電性粒子を介した接触接続に加え、電極間を金属間化合物3によるはんだ接続とする。

(もっと読む)

実装基板および半導体装置

【課題】実装基板に対して半導体チップが平行な姿勢で接合された半導体装置、およびそのような半導体装置を得ることができる実装基板を提供すること。

【解決手段】実装基板1のソルダレジスト膜4には、各電極部3を個別に露出させるための複数の電極開口部5と、各電極開口部5に連続する逃がし開口部6とが形成されている。一方、半導体チップ7の表面には、複数の金属ボール8が配置されている。複数の金属ボール8は、半導体チップ7が実装基板1に接合されたときに、それぞれ対応する電極部3に接続されて、半導体チップ7を実装基板1に対して所定間隔を保つように連結する。このとき、複数の金属ボール8間でサイズにばらつきがあっても、相対的に大きなサイズを有する金属ボール8の一部を逃がし開口部6に逃がすことができるので、実装基板1に対して半導体チップ7を平行に保つことができる。

(もっと読む)

半導体部品の垂直マウント方法

フリップチップマウントの際に、ウェーハ(1)内に製造された複数の半導体部品(2)の複数の接続コンタクト(3)上への複数のさらなる接続コンタクト(5)を有する、複数の半導体チップ(4)の表面に、液状層(6)が提供される。その液状層は、ウェーハ(1)上への複数の半導体チップ(4)の配置の際に、固まり、それにより、半導体チップを固定する。その構造は、真空オーブン内において、高温状態においてはんだ付けされ得、その際、付着剤は蒸発する。複数の半導体チップ(4)は、その際、ウェーハ上において加圧され得る。  (もっと読む)

(もっと読む)

発光光源及びその製造方法並びに発光装置

【課題】LEDベアチップ等の発光素子と基板との間の空隙をなくすことができ、出力光の色度が均一で、発光効率の高い発光光源を提供する。

【解決手段】発光素子(1)と、導体パターン(4)を含む基板(2)と、蛍光体と透光性母材とを含む蛍光体層材料(3)とを含み、発光素子(1)は導体パターン(4b)に接続され、蛍光体層材料(3)は発光素子(1)を被覆し、発光素子(1)と基板(2)との間に蛍光体層材料(3)の少なくとも透光性母材が配置されている発光光源とする。

(もっと読む)

はんだ印刷用マスクおよびはんだバンプの形成方法

【課題】本発明は、半導体パッケージや回路部品を回路基板上に実装してなる電子機器の製造において、回路基板上にはんだペーストを充填する際、ばらつきが小さく、かつ短タクトのはんだペーストの充填方法を提供することを目的とするものである。

【解決手段】所望の形状をした貫通孔3を有する高耐熱性材料の板体1の片面に、前記貫通孔3と同一位置に貫通孔4を有する弾性材料からなる膜2を形成してはんだ印刷用マスク5を構成する。

(もっと読む)

バンプ電極付き電子部品の製造方法

【課題】充分な膜厚の表面保護用絶縁膜および充分な高さのバンプ部を具備する電子部品を、オープン不良の発生を抑制しつつ製造するのに適した方法を提供する。

【解決手段】本発明の電子部品製造方法は、電極パッド12と、当該電極パッド12に対応する開口部を有する絶縁膜とが設けられている基材における当該電極パッド12の上に、開口部内において導電連絡部を形成する工程と、導電連絡部の上に、当該導電連絡部に直接接触して開口部から突出するようにバンプ部15を形成する工程とを含む。バンプ部15を形成する工程は、絶縁膜の上に樹脂膜30を積層形成する工程と、樹脂膜30に対して、導電連絡部が露出するように開口部30aを形成する工程と、樹脂膜30の開口部30aに溶融ハンダ36を供給する工程(a)と、溶融ハンダ36を冷却してバンプ部15を形成する工程(b)と、樹脂膜30を絶縁膜から剥離する工程(c)とを含む。

(もっと読む)

ウェハ積層時の重ね合わせ方法

【解決課題】

ウェハを積層して積層型半導体装置を製造するとき、重ね合わせるウェハ上のマークを検出してウェハ間のアライメントを行う。この時、すでに積層されたウェハを観察するとウェハ上のアライメントマークが複数個視野内に入り、検出精度が低下する。このために重ね精度が低下して積層型半導体装置の製造歩留まりが悪くなる。

【解決手段】

隣接して積層されるウェハ上のマークを互いに所定の間隔を有して形成する。これにより、例え同じ視野内に複数のマークが入ってもマークの分離が容易になる。

(もっと読む)

1,041 - 1,060 / 1,142

[ Back to top ]