Fターム[5F044LL01]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160)

Fターム[5F044LL01]の下位に属するFターム

基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL01]に分類される特許

1,121 - 1,140 / 1,142

エポキシ樹脂組成物及びそれを用いた半導体装置並びに表示素子

【課題】本発明の課題は、液状樹脂組成物を用いて半導体チップ、特に回路面にはんだ電極を有する半導体チップを封止する半導体装置及び表示素子の製造方法において、良好なはんだ接続性と高信頼性を同時に満足する半導体装置及び表示素子を得ることである。

【解決手段】 常温で液状であり、1分子中にエポキシ基を2個以上含むエポキシ樹脂(A)、1分子中に少なくとも2個のフェノール性水酸基と少なくとも1個の芳香族カルボキシル基を有する硬化剤(B)、及びフェノール性水酸基を1分子あたり3個以上有する硬化剤(C)を含むことを特徴とするエポキシ樹脂組成物を用いる。

(もっと読む)

インジウム、ビスマス及び/またはカドミウムを含有する低温活性半田を用いて形成した電子パッケージ

活性半田合金、電子装置を基板に結合する前記活性半田合金を含有する電子装置パッケージ及び前記半田合金を用いる半田付けによって高強度接合部を形成する方法。前記合金は、約10重量%までのチタン、ジルコニウム、ハフニウム、バナジウム、ニオブ及びタンタルから成る群から選択される元素または元素混合物;約0.1‐5重量%のランタノイド元素(希土類元素)の群から選択される元素または元素混合物;約0.01‐1重量%のガリウム;約10重量%までの銀;約2重量%までのマグネシウム;及び錫、ビスマス、インジウム、カドミウム、またはこれらの元素の2種以上の混合物から成る残余を含有する。前記合金は、比較的狭い溶融範囲(約10℃未満)内で低温(約180℃未満)半田付けを可能とする。  (もっと読む)

(もっと読む)

はんだの組成物、及びはんだ接続部を製造する方法

はんだ組成物が、熱力学的に準安定な合金の粒子を有する。前記合金の元素の1つは、金属表面と共に金属間化合物を形成する。前記はんだ組成物は、半導体デバイスのバンピングにおける使用に特に適している。  (もっと読む)

(もっと読む)

超高真空管のための半導体取り付け

【解決手段】熱効率のよい超高真空管を形成するために、半導体ダイとともに使用する、新規な結合および相互接続の技術に関するもので、形成された超高真空管もまた新規である。  (もっと読む)

(もっと読む)

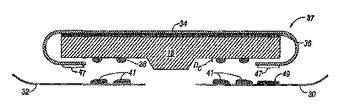

重ねモジュールシステムと方法

本発明は、チップスケールパッケージ集積回路(CSP)を積み重ねてPWB他のボードの表面積を一定に保つモジュールにする。発明の好ましい実施の形態において、1つ以上のCSPに関連する型台は、標準的な接続可能な屈曲回路デザインを用いると共に、CSPパッケージの幅の広いファミリーにおいて見られる多くの異なるパッケージサイズを使用可能にする。好ましい実施の形態において、下側CSPのコンタクトは、屈曲回路がCSPと型台との組合せに取り付けられる前に圧縮され、CSPと屈曲回路の間のロープロファイルコンタクトを形成する。  (もっと読む)

(もっと読む)

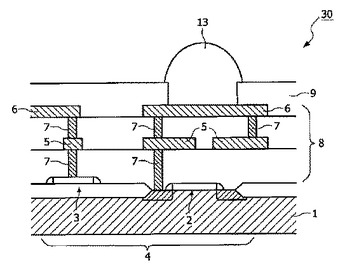

所定領域上に密封構造を有する電子パッケージ及びその方法

光感知素子用電子パッケージが提供される。パッケージは、所定の波長周囲内の光に対して実質的に透明な物質の基板を含むように形成される。また、パッケージは、その前面側上に定義された光感知領域を有する1つ以上の光感知台を含むように形成される。該光感知台は、光感知領域の周囲に配置された複数の配線接合によって前記基板に実装され、それによって前記光感知台の前記前面側は、前記基板の前記前面の表面から間隙を置いて離隔される。密封構造が光感知台と基板との間で実質的に密封された方式で内部の空洞を連続的に捕獲するように、密封構造が形成されてその周囲の間隙の一部を満たすように配線接合の周囲から延長される。この内部の空洞は、光感知台の光感知領域と通じる。 (もっと読む)

半導体装置、半導体装置の製造方法および配線基板の製造方法

配線基板の半田接続用の端子である銅のランド部(4b)上に、無電解Ni−Pめっき層(13a)を形成し、その上に無電解Pdめっき層(13b)を形成し、その上に無電解Auめっき層を形成する。無電解Ni−Pめっき層(13a)上に無電解Pdめっき層(13b)を形成する工程では、下地の無電解Ni−Pめっき層(13a)から無電解Pdめっき液中へのニッケルの溶出量が5×10−6kg/m2以下となるようにする。無電解Ni−Pめっき層(13a)と無電解Pdめっき層(13b)の界面には、10nm以上のボイドは形成されない。その後、配線基板に半導体チップを搭載し、ワイヤボンディングを行い、樹脂封止し、配線基板のランド部(4b)に半田ボールを接続して、半導体装置を製造する。 (もっと読む)

垂直ダイ・チップオンボード

垂直方向ダイ・チップオンボードセンサーパッケージのための方法と装置が提供されている。そのような垂直方向ダイ・チップオンボードセンサーパッケージは、第1面、第2面、底縁部、上縁部、2つの側縁部、底縁部近くに配置されている入/出力(I/O)パッド、及び少なくとも1つの感受方向を備えた垂直方向センサー回路構成要素を備えている。そのような垂直方向ダイ・チップオンボードセンサーパッケージは、更に、上面、印刷回路板(PCB)取り付け面、垂直方向センサー回路構成要素境界縁部、2つ又はそれ以上の他の縁部、及び1つ又は複数の感受方向を備えた1つ又は複数の水平方向センサー回路構成要素を備えており、垂直方向センサー回路構成要素境界縁部は、垂直方向センサー回路構成要素をZ軸に沿って支持し、垂直方向センサー回路構成要素に導電的又は非導電的に接続されている。  (もっと読む)

(もっと読む)

回路基板の実装構造

【課題】第1の回路基板と第2の回路基板に配線された差動伝送路が、第1の基板の少なくとも一方の面に設けられたパッドと、それに対向する第2の回路基板の面に設けられたパッドと、そのパッド間に挿入された導体バンプによって接続する回路基板の実装構造において、半導体装置と回路基板、或いは回路基板同士で高周波信号の差動伝送をする際に生じる反射を低減し、高密度接続の容易性を損なうことなく、信号信頼度の高い回路基板の実装構造を提供する。

【解決手段】第1の回路基板の信号用の前記パッドに対面する位置における第1の回路基板のグランドプレーンは排除され、信号用の前記パッドに近接するグランドプレーンの排除された輪郭の一部が、対応するパッド形状の相似形であることを特徴とする回路基板の実装構造。

(もっと読む)

半導体チップ・パッケージ

半導体チップ・パッケージは集積回路チップと基板を含む。チップ・コンタクト・パッドがチップの第1面上に形成される。スタッドがワイヤ・ボンド機を使用してワイヤからチップ・コンタクト・パッド上に形成される。スタッドはチップ・コンタクト・パッドに接着された部分的に押しつぶされたボール部分を有する。スタッドはまた部分的に押しつぶされたボール部分から延びる延長部分を有する。絶縁材の第1層が基板の第1面上にある。底部付きのウェルが第1層に形成され基板の第1面に開口する。第1導電材は少なくとも部分的にウェルを充填する。第1導電材は基板の少なくとも1つのトレース線路に電気的に接続される。スタッドは第1導電材に部分的に埋め込まれてチップと基板との間の電気的接続を形成する。  (もっと読む)

(もっと読む)

直接的なダイの取付けのための金属相互接続システムおよび方法

支持体に直接的に接続させる半導体チップの例示的な態様を示す。チップは、チップの上表面に被着されている金属層と、この金属層状に被着されている保護層であって、保護層の複数の部分が選択的に除去されて1つ以上の開口(「結合パッド」)が形成され、金属層の複数の部分が露出するようになっている、保護層と、1つ以上の開口のそれぞれの上に形成されている1つ以上のはんだ付け可能な金属接触領域とを備えている。チップを支持体上に下向きに配置し、はんだの薄層を設け、加熱すると、はんだ付け可能な金属接触領域が支持体に電気的に接続される。 (もっと読む)

二段階のウェーハ塗布アンダフィル

【課題】超小型電子チップ・アセンブリ、特に集積回路にアンダフィルを塗布する方法及び材料の提供。

【解決手段】大きなウェーハ又は集積回路チップの活性面の塗布される100%非揮発性、一液型液体アンダフィル封入剤が開示される。塗布時に、その封入剤は放射線、特にUV、可視及び赤外線に暴露することによって液化可能、不粘着性固体に転化される。アンダフィルを被覆したウェ−ハは硬化の進行なしに顕著な保存寿命を示す。大きなウェーハは小さいウェーハ切片に単数化されて数ヶ月貯蔵され、その後、半田リフロー中にウェーハ連結アセンブリは固定され、アンダフィルは液化し、すみ肉に流出し、そして熱活性化架橋時に熱硬化へ転化する。

(もっと読む)

バンプ−オン−リードフリップチップ相互接続

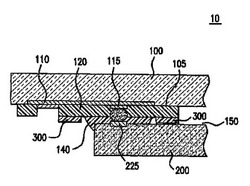

【課題】基板上のトレースのより効率的なルーティングをもたらし、特に、基板の単一金属層において完全にシグナルルーティングを形成し得るバンプ−オン−リードフリップチップ相互接続を提供する。

【解決手段】フリップチップ相互接続は、キャプチャパッド上にというよりも、リード(114)上に相互接続バンプ(104)を直接結合することによって形成される。また、フリップチップパッケージは、アクティブ面の相互接続パッドに取付けられたはんだバンプ(104)を有するダイ(102)と、ダイ取付面(113)に導電性トレース(114)を有する基板(112)とを備え、前記バンプ(104)はトレース(114)上に直接結合される。また、相互接続は、はんだマスク(86)を使用せずに形成される。更に、硬化性接着剤(122)は、ダイ(102)のバンプ(104)上にまたは基板(112)のトレース(114)上に分配され;接着剤(122)は、結合工程の間に部分的に硬化処理され、部分的に硬化処理された接着剤は、リフロー工程の間溶融はんだを閉じ込めるのに役立つ。

(もっと読む)

平坦な上面を有するパッドの製造方法

電子部品において平坦な上面を有するパッドを作製する方法であって、a)第一電子基板上に硬化性シリコーン組成物の平坦な上面を有する堆積物をステンシル印刷する過程であって、第一電子基板が半導体ダイ又は半導体ダイ取り付け部材から選択され、平坦な上面を有する堆積物のステンシル印刷がダウンステップステンシルを通したスクイジーにより行われる、堆積物をステンシル印刷する過程と、b)平坦な上面を有する堆積物を硬化させる過程であって、それにより、平坦な上面を有するパッドを形成する、堆積物を硬化させる過程と、任意にc)平坦な上面を有するパッドの上面に第二電子基板を接着する過程であって、第二電子基板は半導体ダイ又は半導体ダイ取り付け部材から選択される、第二電子基板を接着する過程、並びに、任意にd)過程a)、b)及びc)を反復する過程を包含する、パッドを作製する方法。

(もっと読む)

(もっと読む)

集積型電子チップ及び相互接続デバイス、並びにそれを製造するための方法

【課題】 集積型電子チップ及び相互接続デバイス、並びにそれを製造するための方法を提供すること。

【解決手段】 半導体デバイスと、マザーボードに接続するためのコネクタとを含む集積構造を形成するための方法が説明される。第1の層(26)が除去用放射線を通すプレート(23)上に形成され、第2の層(32)が半導体デバイス(31)上に形成される。第1の層は、マザーボードへの接続に必要とされる間隔に応じた第1の間隔距離だけ離されたボンディング・パッド(27p)に接続される導体の第1の組(27)を有する。第2の層は、半導体デバイスに接続される導体の第2の組(33)を有する。第1の層及び第2の層は、ボンディング・パッドの間隔より短い間隔を有するスタッド/バイア・コネクタ(29、36)を用いて接続される。このようにして、半導体デバイスが第1の層に取り付けられ、導体の第1の組と第2の組とがスタッドを通して接続される。第1の層とプレートとの間の界面が、該プレートを透過する除去用放射線(45)によって除去され、それによって該プレートが分離される。次いで、コネクタ構造(47、48、49)がボンディング・パッドに取り付けられる。本方法は、低コストで、高密度にパッケージされたデバイスを製造することを可能にする。

(もっと読む)

熱可塑性フラクシングアンダーフィル組成物及び方法

ハンダバンプと、熱可塑性樹脂とフラックスであるアンダーフィルとを有するフリップチップ、及びそのデバイスを製造する方法並びに材料を提供する。得られるデバイスは、プリント回路板に対する簡単なワンステップ適用に適し、フリップチップの製造方法を簡単にすることができる。  (もっと読む)

(もっと読む)

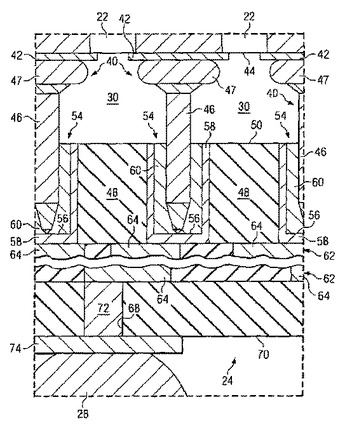

リードモールドパッケージ内のフリップチップ搭載のための開口部または溝つきリードフレーム構造

半導体パッケージについて開示する。ある実施例では、ダイパッケージは第1表面と第2表面を有する半導体ダイと、ダイ接合領域とダイ接合領域から伸長している複数のリードをもつリードフレーム構造を有している。ダイ接合領域は1つ又は複数の開口部を含んでいる。モールド材は少なくともリードフレームのダイ接合領域と半導体ダイの周囲を囲んでいる。モールド材は1つ又は複数の開口部の内部にも存在する。  (もっと読む)

(もっと読む)

半導体装置の製造方法、半導体装置、及び電子機器

【課題】半導体チップを封止する樹脂の収縮による半導体チップの撓み及びクラックを防止し、高い充填率で封止樹脂を充填することができ、高信頼性を有する半導体装置を製造することができる半導体装置の製造方法及び半導体装置、並びに当該半導体装置を備える電子機器を提供する。

【解決手段】接続電極42が形成されたインターポーザ40上に、積層する半導体チップC1との間隔と同程度の径であり電気的絶縁性を有する支持球46を搭載し、この支持球46が搭載された面上に半導体チップC1を積層する。半導体チップC1上に他の半導体チップを積層する場合も同様に、半導体チップC1と他の半導体チップとの間隔と同程度の径であり電気的絶縁性を有する支持球48を搭載し、この支持球48が搭載された面上に他の半導体チップを積層する。

(もっと読む)

電子部品実装システムおよび電子部品実装方法

【課題】 リフロー過程における接合不良を防止することができる電子部品実装システムおよび電子部品実装方法を提供することを目的とする。

【解決手段】 基板3に電子部品15を半田接合により実装して実装基板を製造する電子部品実装において、基板3に搭載された電子部品15の上にこの電子部品15を自重により基板に対して押し付ける押付部材16を載置する。この状態で基板3をリフローに送り、加熱することにより電子部品15の半田バンプ15aを溶融させて基板3の回路電極3aと半田接合する。これにより、半田溶融時に電子部品15を押付部材16の押し付け力によって適正に沈み込ませることができ、接合不良を防止することができる。

(もっと読む)

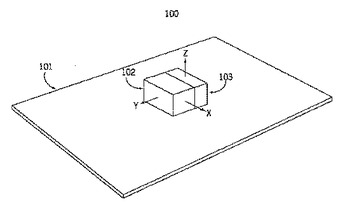

半導体デバイス、半導体モジュール及びこれらの実装方法

【課題】 半導体デバイスや半導体モジュールの誤実装を低減する。

【解決手段】 半導体デバイス10の半導体パッケージ11の裏面に配設された各接続電極12に融点の異なる第1の半田ボール13及び第2の半田ボール14を接合し、融点の低い第1の半田ボール13を半導体デバイス10の外周側に配設し、融点の高い第2の半田ボール14を内周側に配設する。そして、ベース基板21上に接点22を配設し、この接点22上に半田ペースト23が印刷された実装基板20上に半導体デバイス10を配置し、第1の半田ボール13が溶融する第1の温度まで加熱し、次に第2の半田ボール14及び半田ペースト23が溶融する第2の温度まで加熱するリフロー半田付けを行う。

(もっと読む)

1,121 - 1,140 / 1,142

[ Back to top ]