Fターム[5F045AD11]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜温度 (8,040) | 700≦T<800℃ (666)

Fターム[5F045AD11]に分類される特許

41 - 60 / 666

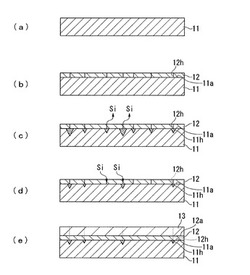

立方晶炭化珪素半導体基板の製造方法

【課題】結晶欠陥の少ない高品質な3C−SiC層を形成することが可能な立方晶炭化珪素半導体基板の製造方法を提供する。

【解決手段】シリコン基板11の上面11aに炭化層12を形成する第1の工程と、シリコン基板11の温度を第2の温度範囲の温度まで下降させる第2の工程と、シリコン基板11の温度が第2の温度範囲の温度となったところで、シリコン原料ガスを導入し、シリコン基板11と炭化層12の間の界面に形成された空孔11hにシリコンをエピタキシャル成長させて空孔11hを埋める第3の工程と、シリコン原料ガスの導入を止め、炭素原料ガスを導入しつつシリコン基板11の温度を第3の温度範囲の温度まで上昇させる第4の工程と、シリコン基板11の温度が第3の温度範囲の温度となったところで、シリコン原料ガス及び炭素原料ガスを導入し、炭化層12上に立方晶炭化珪素をエピタキシャル成長させる第5の工程と、を有する。

(もっと読む)

窒化ガリウム膜の形成方法、及び窒化ガリウム膜の形成装置

【課題】層状構造の窒化ガリウム膜を汎用的の高められたプロセスで選択的に形成することの可能な窒化ガリウム膜の形成方法、及び該形成方法を用いて窒化ガリウム膜を形成する装置を提供する。

【解決手段】

窒化ガリウム膜を反応性スパッタにて単結晶の基板S上に形成するときに、真空槽11内に供給されるアルゴンガス及び窒素ガスの総流量に占める窒素ガスの流量の割合を窒化ガリウム膜の成長速度が窒素供給によって律速され、且つ、窒化ガリウム膜の成長速度の極大値に対して30%以上90%以下の成長速度となる範囲とする。また、基板温度T(℃)、ガリウムのターゲット14に供給される周波数が13.56MHzである高周波電力をバイアス電力P(W/cm2)とするとき、基板温度T及びバイアス電力Pが、600≦T≦1200、0<P≦4.63、T≧0.0083P−4.7、T≦0.0084P−6.6を満たすようにする。

(もっと読む)

窒化物半導体薄膜およびその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供する。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(工程1)により制限領域内に形成されたテラス202に、工程1よりもキャリアガスに含まれる水素の組成を少なくして、トリメチルガリウム(TMG)又はトリエチルガリウム(TEG)を供給し、テラス202の上にGaNの2次元核301を1個以上100個以下発生させる(工程2)。次に、工程2よりもキャリアガスに含まれる水素の組成を多くする(工程3)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる。工程2と工程3を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長させる。

(もっと読む)

熱処理装置及び熱処理方法

【課題】基板を基板保持具に搭載して縦型熱処理炉に搬入し、熱処理を行う熱処理装置において、縦型熱処理炉からアンロードされた基板保持具に搭載された基板を速やかに降温させること。

【解決手段】前面から、当該前面に対向する後面の気流形成用の排気口63aに向って横方向の気流が形成されたローディングエリアS2内にて、熱処理炉2の下方側のアンロード位置におけるウエハボート3Aと前記排気口63aとの間に、アンロードにより高温に加熱された雰囲気を吸引排気するための熱排気用の排気口71が形成された排気ダクト7B,7Cを設ける。アンロードされた高温状態のウエハボート3A近傍の雰囲気は排気ダクト7B,7Cから排気されるので、上方側への熱拡散が抑えられ、横方向の気流がウエハボート3A及びウエハ群に供給されて、熱処理後のウエハを速やかに降温させることができる。

(もっと読む)

半導体装置の製造方法

【課題】低温で高品質な生成膜の生成を可能とし、デバイスの性能の向上を図ると共に歩留りの向上を図る半導体装置の製造方法を提供する。

【解決手段】処理室に基板を搬入する工程と、処理室及び基板を所定の温度に加熱する工程と、処理室に所定のガスを給排するガス給排工程とを含み、ガス給排工程は、シラン系のガスと水素ガスとを処理室に供給する第1の供給工程と、少なくともシラン系のガスを処理室から除去する第1の除去工程と、塩素ガスと水素ガスとを処理室に供給する第2の供給工程と、少なくとも塩素ガスを処理室から除去する第2の除去工程とを、所定回数繰返して実行させる。

(もっと読む)

半導体材料の選択堆積方法

【課題】シリコンやゲルマニウムのようなIV族半導体材料を、半導体表面上に、絶縁表面上への堆積無しに選択的に堆積する方法を提供する。

【解決手段】半導体プロセスで半導体材料の選択成長を行う方法が、第1領域11と第2領域12とを含むパターニングされた基板10を提供する工程を含み、第1領域11は露出した第1半導体材料を含み、第2領域12は露出した絶縁材料を含む。この方法は、更に、第2半導体材料の前駆体、Cl化合物とは応性しないキャリアガス、および錫テトラクロライド(SnCl4)を供給することにより、第1領域の第1半導体材料の上に第2半導体材料の膜を選択的に形成する工程を含む。錫テトラクロライドは、第2領域の絶縁材料上への第2半導体材料の堆積を阻害する。

(もっと読む)

積層基板及びその製造方法

【課題】結晶性の炭化アルミニウム層及び窒化ガリウム層を有する積層基板及びその製造方法を提供する。

【解決手段】基板1としてサファイア基板、炭化ケイ素基板または窒化アルミニウム基板の上に結晶性のGaN層10、結晶性のAlC層20を順次積層して配置した

積層基板100であって、炭化アルミニウムの結晶の成長条件としては、アルミニウムを含むガスとしてトリメチルアルミニウムと、炭素を含むガスとしてメタンを供給し、有機金属気相成長法により成長させる。成長温度としては700℃以上が好ましく、さらには1100℃以上が好ましい。

(もっと読む)

薄膜形成のための方法とシステム

【課題】第III−V族含有薄膜を形成する方法を提供する。

【解決手段】実施態様において、二成分化合物のエピタキシャル薄膜を形成するためのシステムと方法を含むエピタキシャル薄膜形成ためのシステムと方法が提供されている。本発明の実施形態の方法とシステムは、例えば、GaN、InNおよびAlN、ならびにこれらの化合物の混合合金、例えば、(In, Ga)N、(Al, Ga)N、(In, Ga, Al)Nのような直接の禁止帯半導体二元素化合物エピタキシャル薄膜形成のために用いられる。前記方法および装置は、準単分子層薄膜蒸着の急速反復を可能にする多段階蒸着プロセスおよびシステムを含む。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

InNを含む半導体層の成膜方法および気相成長装置

【課題】結晶性、電気的特性、および光学特性等に優れたInNを含む半導体層を成膜する方法を提供する。

【解決手段】本発明のInNを含む半導体層の成膜方法は、プラズマで分解された水素原子と、In金属またはInを含む化合物からなるIn源とを反応させることによってIn水素化物を形成するステップと、プラズマで窒素を分解することによって原子状窒素を形成するステップと、In水素化物と原子状窒素とを反応させることによって、基板上にInNを含む半導体層を形成するステップとを含むことを特徴とする。

(もっと読む)

炭化アルミニウム薄膜、炭化アルミニウム薄膜を形成した半導体基板及びそれらの製造方法

【課題】結晶性の炭化アルミニウム薄膜、結晶性の炭化アルミニウム薄膜を形成した半導体基板及びそれらの製造方法を提供すること。

【解決手段】本発明によると、炭化アルミニウムの結晶を含むことを特徴とする炭化アルミニウム薄膜が提供される。また、本発明によると、炭素を含むガスと、アルミニウムを含むガスとを供給し、基板上に炭化アルミニウムの結晶を成長させて、炭化アルミニウム薄膜を形成することを特徴とする炭化アルミニウム薄膜の製造方法が提供される。

(もっと読む)

ノズル取付方法

【課題】ノズルを縦型反応管に適正に取り付ける方法を提供する。

【解決手段】マニホールド209にノズル20を取り付けるに際して、保持治具10をノズル20の上下両端部に取り付け、ノズル20の水平部をマニホールド209の取付口210に処理室201側から挿入し、上下の保持治具10の前端面を処理室201の内周面に当接させることでノズル20と処理室201の内周面とのクリアランスおよび平行を自動的に保持する。ノズル20を保持治具10で位置決めした状態で、ノズル20の水平部を取付口210に設置された継手211に固定し、その後、上下の保持治具10をノズル209から取り外す。

(もっと読む)

半導体基板、半導体基板の製造方法および垂直共振器面発光レーザ

【課題】垂直共振器面発光レーザ用の半導体基板におけるp型結晶層をV/III比が小さいエピタキシャル条件で形成するとともにp型結晶層の電気抵抗を低減する。

【解決手段】垂直共振器面発光レーザ用の半導体基板であって、半導体基板はコンタクト層として機能するp型結晶層を有し、p型結晶層が、3−5族化合物半導体からなり、2×1018cm−3以上、1×1019cm−3以下の濃度の水素原子を含む半導体基板を提供する。p型結晶層として、p型GaAs層が挙げられる。p型結晶層が、p型不純物原子として炭素原子を含んでもよい。

(もっと読む)

窒化膜の形成方法

【課題】バッチ式の縦型炉を用いてプラズマアシストALD法により窒化膜を形成する際、炉底部付近でのローディング効果を抑制する。

【解決手段】反応容器102内に複数段にウエハを載置可能なボート101と、前記反応容器の側面に沿ってRF電極106で挟まれたプラズマ空間105と、該プラズマ空間から前記反応容器内の前記各段のウエハに略均等にガスを供給可能な供給口F1,F2と、を備えたバッチ式の縦型炉100を用いて、窒化すべきガスの導入、吸着、パージ、プラズマ励起された窒化ガスの導入による前記窒化すべき吸着ガスの窒化およびパージ、を1サイクルとして所定の膜厚までサイクルを繰り返すプラズマアシストALD法において、前記窒化すべきガス導入時のキャリアガス量よりも前記窒化ガス導入時のキャリアガス流量を少なくし、特に窒化ガスとしてのNH3とキャリアガスとしてのN2の流量比をNH3の50に対してN2を3以下とする。

(もっと読む)

高電子移動度トランジスタ用エピタキシャルウェハの製造方法、及び高電子移動度トランジスタ用エピタキシャルウェハ

【課題】不純物のメモリー効果を低減できる高電子移動度トランジスタ用エピタキシャルウェハの製造方法、及び高電子移動度トランジスタ用エピタキシャルウェハを提供する。

【解決手段】本発明に係る高電子移動度トランジスタ用エピタキシャルウェハの製造方法は、AlxGa1−xAs(ただし、0≦x≦0.3)からなるバッファ層と、バッファ層の上方に設けられ、Se又はTeを含むコンタクト層20とを備えた高電子移動度トランジスタ用エピタキシャルウェハの製造方法であって、600℃以上750℃以下の成長温度、20以上200以下のV/III比の成長条件下で、バッファ層の酸素濃度を2.0E16cm−3以下に制御してバッファ層を単結晶基板上に形成するバッファ層形成工程と、350℃以上500℃以下の成長温度で、コンタクト層20の表面の表面粗さRaを0.5nm以上5.0nm以下の範囲に制御してコンタクト層20を形成するコンタクト層形成工程とを備える。

(もっと読む)

酸化亜鉛系半導体の成長方法

【目的】

p型ドーパント濃度の制御性に優れ、高品質なp型ZnO系結晶の成長方法を提供する。

【解決手段】

MOCVD法により、分子構造中に酸素原子を含まない有機金属化合物と極性酸素材料とを用いてZnO系結晶層を成長する単結晶成長工程を有し、上記単結晶成長工程は、TBP(ターシャリーブチルホスフィン)を供給する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】高い結晶品質を有する量子ドットを高密度に形成しうる半導体装置の製造方法を提供する。

【解決手段】下地層10上に、自己組織化成長により量子ドット16を形成する工程と、量子ドット16を形成する工程の前又は量子ドット16を形成する工程の際に、下地層10の表面にSb又はGaSbを照射する工程と、量子ドット16の表面をAs原料ガスによりエッチングすることにより、量子ドット16の表面に析出したSbを含むInSb層18を除去する工程と、InSb層18が除去された量子ドット16上に、キャップ層22を成長する工程とを有している。

(もっと読む)

基板処理装置

【課題】処理炉内温度補正方法の作業性を向上し、コストを低減する。

【解決手段】処理室内温度補正方法実施前に、温度計測器支持機構10の位置を定義し記憶する(A1)。温度補正方法実施時、温度計測器支持機構10を格納状態から突出状態に移行させ、温度計測器支持機構10をシールキャップ219の開口させた挿入口20の真下に搬送する。温度計測器支持機構10をウエハ移載装置エレベータ125bで上昇させて温度計測器18を挿入口20に挿入する。シールキャップ219をボートエレベータ151で上昇させて、処理炉202をシールキャップ219で閉塞する(A2)。処理炉202内温度をヒータ206で上昇させる(A3)。同時に、処理炉202内温度を温度計測器18で計測する(A4)。温度補正値を算出し記憶する(A5)。均熱温度が規定値内に入るまで繰り返し(A6−7)、規定値に入ると、温度補正方法を終了する。

(もっと読む)

光半導体素子

【課題】高効率の光半導体素子を提供する。

【解決手段】実施形態によれば、n形半導体層と、p形半導体層と、n形半導体層とp形半導体層との間に設けられた機能部と、を備えた光半導体素子が提供される。機能部は、n形半導体層からp形半導体層に向かう方向に積層された複数の活性層を含む。複数の活性層の少なくとも2つは、多層積層体と、n側障壁層と、井戸層と、p側障壁層と、を含む。多層積層体は、前記方向に交互に積層された複数の厚膜層と厚膜層よりも厚さが薄い複数の薄膜層とを含む。n側障壁層は、多層積層体とp形半導体層との間に設けられる。井戸層は、n側障壁層とp形半導体層との間に設けられる。p側障壁層は、井戸層とp形半導体層との間に設けられる。

(もっと読む)

大面積CVDダイヤモンド単結晶の製造方法、及びこれによって得られた大面積CVDダイヤモンド単結晶

【課題】凹部のない大面積で高品質なCVDダイヤモンド単結晶及びこれを実現する製造方法の提供。

【解決手段】主面が{100}であるダイヤモンド単結晶基板の{100}側面同士を近接させて4枚以上配置し、該配置した単結晶基板の主面にダイヤモンドを気相合成により成長させた後、該単結晶基板を除去して1枚の大面積CVDダイヤモンド単結晶を製造する方法であって、前記ダイヤモンド単結晶基板の配置が、近接する任意の4枚の単結晶基板の、隣接する2枚の単結晶基板A1とA2とからなる単位Aと、他の2枚の単結晶基板B1とB2とからなる単位Bとにおいて、A及びBが対向する側の面がそれぞれ同一平面上にあり、かつA1とA2が対向する側面間の間隔の真中の面と、B1とB2が対向する側面間の間隔の真中の面とが、単位Aと単位Bが対向する面の方向にずれている配置であることを特徴とする大面積CVDダイヤモンド単結晶を製造する方法。

(もっと読む)

41 - 60 / 666

[ Back to top ]