Fターム[5F045BB11]の内容

気相成長(金属層を除く) (114,827) | 目的 (9,309) | 歪・反り防止 (1,345)

Fターム[5F045BB11]の下位に属するFターム

結晶性・格子整合性の向上・結晶欠陥の防止 (911)

スリップライン、クラックの発生防止 (217)

Fターム[5F045BB11]に分類される特許

81 - 100 / 217

加熱処理装置

【課題】自動搬送を行う場合、温度変化による凹凸形状の相対位置バラツキと機構停止精度等による相対位置バラツキの和が、嵌合部における隙間量を超えると搬送不能となるが、これに対し複雑な位置検出機構を用いなくても搬送不良を起こさない高温炉などの処理装置を提供する。

【解決手段】まず十分な隙間量を有する位置で浅い嵌合深さで挿入用穴部と前記挿入用突起部のみを嵌合し、次にそれらを平面方向に相対移動させて、前記挿入用穴部と前記挿入用突起部に加えて前記位置決め用穴部と前記位置決め用突起部も嵌合可能な位置で前記挿入用突起部と前記挿入用穴部との側面同士を接触させ、さらに深く挿入して前記位置決め用穴部と前記位置決め用突起部も嵌合させることで、搬送時の装置温度によらず位置決め後の突起部と穴部の相対位置を安定させることが可能で、より高精度な位置決めが可能になる。

(もっと読む)

エピタキシャル成長方法

【課題】エピタキシャル成長処理において、裏面デポジションの成長を抑えることにより、得られるエピタキシャルウェーハの平坦度を向上させるエピタキシャル成長方法を提供する。

【解決手段】エピタキシャル成長炉2内に付着したシリコン堆積物を塩化水素含有ガスによりエッチング除去するクリーニング処理工程と、クリーニング処理工程に引き続き、エピタキシャル成長炉内にシリコンソースガスを供給してサセプタ表面にグレーンサイズが0.7μm〜0.3μmのポリシリコン膜を形成するポリシリコン成膜工程とを有することを特徴とするエピタキシャル成長方法である。

(もっと読む)

III族窒化物結晶の製造方法、III族窒化物結晶基板およびIII族窒化物半導体デバイス

【課題】転位密度が低く、かつ、不純物の濃度が低いIII族窒化物結晶の製造方法、III族窒化物結晶基板およびIII族窒化物半導体デバイスを提供する。

【解決手段】本III族窒化物結晶の製造方法は、液相法により第1のIII族窒化物結晶10を成長させる工程と、第1のIII族窒化物結晶10の表面を、表面粗さRaが5nm以下かつ反りの曲率半径が2m以上になるように加工する工程と、加工がされた第1のIII族窒化物結晶10上に気相法により第2のIII族窒化物結晶20を成長させる工程と、を含む。

(もっと読む)

窒化物半導体基板

【課題】窒化物半導体基板にエピタキシャル成長する場合において、基板ホルダとの密着性を向上させ、基板面内の温度分布を均一にして、膜厚などの特性を均一にすることが可能な窒化物半導体基板を提供する。

【解決手段】基板28表面側に凹の反りを負、基板28表面側に凸の反りを正とし、基板裏面28aの一端から基板中心線L上を通り前記基板裏面28aの他端に至る線分を引き、該線分で基板28を基板厚さ方向に切断したとき、引いた前記線分上の任意の点から切断面の裏面側輪郭線までの距離の最短値のうち、最大のものを直径方向の反りHと定義した場合に、前記直径方向の反りHを基板周方向にわたって求め、その最大のものをHmaxとし、最小のものをHminとしたとき、前記直径方向の反りHが、Hmax−Hmin≦30μmとなるように規定された窒化物半導体基板28。

(もっと読む)

半導体積層構造体の製造方法

【課題】内部応力及び反りを低減させる。

【解決手段】まず、室温において、基板2の裏面上に、基板2よりも熱膨張率が低い第1の膜3を成膜する(a)。次に、高温まで加熱した後に(b)、基板2の表面2a上に、基板2よりも熱膨張率が高いバッファ層4及び第2の膜5を成膜する(c)。しかる後、半導体積層構造体1の温度が室温まで低下すると、半導体積層構造体1は基板2及びすべての膜3、4、5がほぼ反りのない平坦なものとなる(d)。

(もっと読む)

おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法

【課題】おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法。

【解決手段】本方法は、次の順序で工程:前記シリコン単結晶基板のおもて面及び裏面を同時に研磨する工程;応力補償層を前記シリコン単結晶基板の裏面上に堆積させる工程;前記シリコン単結晶基板のおもて面を研磨する工程;前記裏面上に堆積された応力補償層を有する前記シリコン単結晶基板を洗浄する工程;及びSiGeの完全に又は部分的に緩和された層を前記シリコン単結晶基板の前記おもて面上に堆積させる工程を含んでなる。

(もっと読む)

単結晶GaN基板

【課題】貫通転位密度が小さく、かつ基板表面においても転位の束が存在せず、劈開面の乱れを起こさないGaN基板の製造方法およびGaN基板を提供すること。

【解決手段】基板の上にGaN単結晶を気相成長させ、気相成長でできたGaN単結晶インゴットを成長方向と平行な面でスライス加工して基板とする。転位は成長方向に伸びるので、成長方向と平行に結晶を切ると転位延長方向と平行にスライスすることになる。スライスした基板においては、転位が表面に平行に走るので低転位密度になる。さらにこれを種結晶としてGaN成長させる。表面の転位密度が低いので、2度目に成長したGaNはさらに低転位になる。これもGaN基板とすることができる。

(もっと読む)

MOCVD装置

【課題】結晶成長中において基板の形状を計測し、かつ原料ガスの流れの乱れを少なくすることができるMOCVD装置を提供する。

【解決手段】本発明のMOCVD装置は、原料ガス38aを供給して基板33の被処理面に結晶を成長させ、基板33の被処理面に面した壁に、基板33の被処理面の中央部を望み得る窓30cを有する反応室30と、反応室30に設けられ、基板33を載置して回転(移動)させるための回転台(移動台)31と、回転台31によって回転する基板33の被処理面に、窓30cを介してレーザー光40aを垂直に照射するとともに、被処理面から反射したレーザー光40bを、窓30cを介して受光して、ドップラー効果を利用して基板33の回転速度を計測するための第1の速度計測手段40と、第1の速度計測手段40による計測結果を処理して基板33の形状情報を出力するための処理手段41とを備えている。

(もっと読む)

窒化物半導体エピタキシャル基板

【課題】デバイス活性層でのクラック発生が抑制され、かつ、転位密度の低減等の結晶性の向上を図りつつ、窒化物半導体の厚膜化に伴う反りも抑制された、製造効率に優れたバッファ構造を備えた窒化物半導体エピタキシャル基板を提供する。

【解決手段】Si基板1と、厚さ2〜10nmのAlaGa1-aN(0.9≦a≦1.0)単結晶層31および厚さ10〜30nmのAlbGa1-bN(0≦b≦0.1)単結晶層32が交互に繰り返し積層された第1の多層バッファ領域3と、厚さ2〜10nmのAlcGa1-cN(0.9≦c≦1.0)単結晶層41および厚さ200〜500nmのAldGa1-dN(0≦d≦0.1)単結晶層42が交互に繰り返し積層された第2の多層バッファ領域4と、GaN単結晶層5と、AlxGa1-xN(0<x<1)単結晶層6とを備えた構成の窒化物半導体エピタキシャル基板を作製する。

(もっと読む)

ウェーハ評価方法及びエピタキシャルウェーハ製造方法

【課題】エピタキシャル成長に関するウェーハの評価を適切に行うことのできる技術を提供する。

【解決手段】ウェーハ評価方法において、ウェーハの形状を測定する測定ステップと、エピタキシャル成長の成長条件に基づいて、エピタキシャル成長によりウェーハに付加される反り付加形状を特定する反り付加形状特定ステップと、ウェーハの上面に対して、エピタキシャル成長を行った場合の第1推定形状を特定する第1形状特定ステップと、ウェーハの下面に対して、エピタキシャル成長を行った場合のウェーハである第2推定形状を特定する第2形状特定ステップと、第1推定形状及び第2推定形状に基づいて、ウェーハのいずれの主平面に対してエピタキシャル成長を行うか評価する評価ステップとを有するようにする。

(もっと読む)

化合物半導体基板

【課題】窒化物半導体層の割れ(クラック)や結晶欠陥、反りの発生を抑制し、かつ生産性の向上が可能な化合物半導体基板を提供する。

【解決手段】化合物半導体基板1は、結晶面方位が(111)面であるシリコン単結晶基板10と、シリコン単結晶基板10上に形成され、AlxGa1−xN単結晶(0<x≦1)で構成された第1バッファ層20aおよび20bと、第1バッファ層20aおよび20b上に形成され、厚さが250nm以上350nm以下のAlyGa1−yN単結晶(0≦y<0.1)で構成された第1単層30aと、厚さが5nm以上20nm以下のAlzGa1−zN単結晶(0.9<z≦1)で構成された第2単層30bとが交互に複数積層された第2バッファ層30と、第2バッファ層30上に形成され、少なくとも1層以上の窒化物系半導体単結晶層を含む半導体素子形成領域40と、を備える。

(もっと読む)

III族窒化物半導体層の製造方法

【課題】反りの発生を低減させ、かつ製造歩留まりを向上することができるIII族窒化物半導体層の製造方法を提供する。

【解決手段】下地基板10上に、炭化チタン、炭化ジルコニウム、炭化ハフニウム、炭化バナジウムまたは炭化タンタルから選択されるいずれかの炭化物層11を形成する工程と、炭化物層11の上部にIII族窒化物半導体層12を成長させる工程と炭化物層11の上部のIII族窒化物半導体層12中で亀裂を生じさせて、下地基板10を除去し、III族窒化物半導体層12を得る工程とを含む。III族窒化物半導体層12を成長させる工程は、炭化物層11の上部にファセット構造を形成しながら、3次元成長により第一のIII族窒化物半導体層121を成長させる工程と、第一のIII族窒化物半導体層121上に2次元成長により第二のIII族窒化物半導体層122を形成する工程とを含む。

(もっと読む)

窒化物半導体用形成用基板およびその製造方法

【課題】シリコン基板上への窒化物半導体薄膜の形成時における、熱膨張係数差から生じる熱応力および多孔質シリコンの構造変化に起因したピットの問題を解消し、更に該被膜に生じる反りと応力を低減できる、窒化物半導体薄膜形成に好適な窒化物半導体薄膜形成用基板を提供。

【解決手段】シリコン単結晶基体上に、異なる多孔質構造を有するシリコン層を組み合わせ設けたものを基板とし、更に、その上にシリコンエピタキシャル膜層を設けた窒化物半導体形成用基板。

(もっと読む)

半導体装置の製造装置および半導体装置の製造方法

【課題】効率的な製造工程を提供し、製造コストを低減することができる半導体装置の製造装置および半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造装置100は、ウェハカセット2,3,4と、ウェハの洗浄および表面改質を行う装置5と、ウェハの位置合わせを行う装置6と、ウェハ表面にパッシベーション膜となる材料を射出する装置7と、パッシベーション膜の外観検査を行う装置8と、パッシベーション膜に熱処理を行う装置9と、処理順にウェハを各装置に搬送する装置10を備えている。製造装置100では、インクジェット技術を用いて、洗浄後のウェハ表面に、選択的にパッシベーション膜のパターンを形成する。次いで、パッシベーション膜のパターンが、所望のパターン条件を有しているか否かを検査する。パッシベーション膜が所望のパターンで形成されている場合に、パッシベーション膜を硬化および焼成する熱処理を行う。

(もっと読む)

窒化物半導体発光素子とその製造方法

【課題】窒化物半導体発光素子のクラックの発生を防ぎ、かつ基板の掘り込み領域以外の領域上における窒化物半導体層の組成変動を抑制して、高い歩留まりで窒化物半導体発光素子を得る。

【解決手段】窒化物半導体発光素子は、掘り込み領域(16)が形成された主面を有する窒化物半導体基板(10a)と、掘り込み領域上に形成された結晶成長抑制膜(10b)と、結晶成長抑制膜(10b)および基板(10a)の主面を覆うように堆積された複数の窒化物半導体層(11)を含むことを特徴としている。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】本発明は、無極性面または半極性面を有する窒化物半導体基板に、歩留まりの向上等の目的で形成されたの掘り込み領域が、窒化物半導体薄膜の成長時に埋まってしまうことを抑制することを目的し、さらに、Al組成の変動を抑制することを目的とする。

【解決手段】本発明は、無極性面または半極性面を有する窒化物半導体基板に掘り込み領域を形成し、該窒化物半導体基板上に、n型窒化物半導体薄膜、活性層およびAlを含むp型窒化物半導体薄膜を含む窒化物半導体薄膜を形成する窒化物半導体発光素子の製造方法であって、上記p型窒化物半導体薄膜を700℃以上900℃未満の温度で成膜することを特徴とする、窒化物半導体発光素子の製造方法である。

(もっと読む)

発光ダイオード用エピタキシャルウェーハ

【課題】発光波長655nm以上の、高出力・高効率のLEDを量産可能なエピタキシャルウェーハを提供する。

【解決手段】GaAs基板1と、GaAs基板1上に設けられた発光部2と、発光部2上に設けられた歪調整層3とを備え、発光部2は、組成式(AlXGa1−X)YIn1−YP(0≦X≦0.1、0.37≦Y≦0.46)からなる歪発光層7を有し、歪調整層3は、発光波長に対して透明であると共にGaAs基板1の格子定数よりも小さい格子定数を有することを特徴とする発光ダイオード用エピタキシャルウェーハ10を採用する。

(もっと読む)

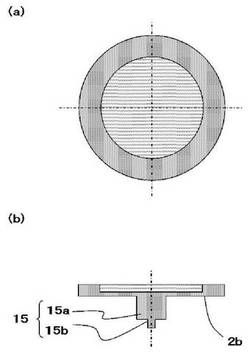

基板の熱処理装置

【課題】 ガラス基板等の基板全体を処理温度まで迅速に加熱することができる基板の熱処理装置を提供する。

【解決手段】 熱処理炉2の炉口6からプロセスチューブ4内に搬入・搬出されるボート7に保持されたガラス基板Wの中央部と、プロセスチューブ4の外側に配置されたヒータ5による輻射熱を断熱する遮熱板13aとの間に、輻射熱を吸収する吸熱フィン14を配置する。

(もっと読む)

III−V族窒化物系半導体基板

【課題】基板上に化合物半導体層を平坦でかつ不純物分布が均一になるように成長させることができるIII−V族窒化物系半導体基板を提供する。

【解決手段】自立したIII−V族窒化物系半導体基板の表面の任意の位置においてフォトルミネッセンスを測定してそのバンド端ピークの発光強度をN1とし、前記測定位置に対応する同一基板上の裏面側のバンド端ピークの発光強度をN2としたときに、その強度比α=N1/N2が0.01≦α≦0.98となるときに良品歩留のIII−V族窒化物系半導体基板とする。

(もっと読む)

電子デバイス用エピタキシャル基板およびその製造方法

【課題】反り形状を適正に制御した、横方向を主電流導通方向とする電子デバイス用エピタキシャル基板およびその製造方法を提供する。

【解決手段】Si単結晶基板と、該Si単結晶基板上に複数層のIII族窒化物層をエピタキシャル成長させて形成したIII族窒化物積層体とを具え、横方向を主電流導通方向とする電子デバイス用エピタキシャル基板であって、前記Si単結晶基板と前記III族窒化物積層体との間に、絶縁層としてのバッファをさらに具え、前記バッファは、1×1018/cm3以上のCを含む超格子多層構造からなる積層体を有し、前記Si単結晶基板はp型基板であって、かつ比抵抗値が0.01Ω・cm以下であることを特徴とする。

(もっと読む)

81 - 100 / 217

[ Back to top ]