Fターム[5F045DA52]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の形状、構造 (2,125) | 多層成長層 (2,091)

Fターム[5F045DA52]の下位に属するFターム

バッファ層・中間層・遷移層を有するもの (1,084)

超格子(歪超格子、変調ドープ超格子を含む) (99)

量子井戸 (345)

量子細線・量子箱 (31)

Fターム[5F045DA52]に分類される特許

161 - 180 / 532

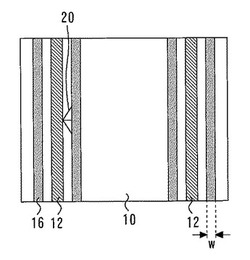

半導体装置の製造方法

【課題】窒化物半導体層の表面平坦性を向上させることができる半導体装置の製造方法を得る。

【解決手段】まず、低転位領域10と、低転位領域10よりも転位密度が高い高転位領域12とを有するGaN基板14を準備する。次に、高転位領域12を覆わずに高転位領域12を囲むように低転位領域10上に絶縁膜16を形成する。次に、GaN基板14上に窒化物半導体層18を形成する。これにより、高転位領域12上で発生した異常成長が低転位領域10に伝播するのを防ぎつつ、原料拡散により絶縁膜16の近傍で窒化物半導体層18の厚みが増大するのを防ぐことができる。この結果、窒化物半導体層18の表面平坦性を向上させることができ、半導体装置の歩留まりを向上できる。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

炭素/トンネル障壁/炭素・ダイオード

炭素/トンネル障壁/炭素・ダイオード及び炭素/トンネル障壁/炭素・ダイオードの形成方法を開示する。炭素/トンネル障壁/炭素はメモリアレイ内でステアリング素子として用いられてもよい。メモリアレイ内の各メモリセルは可逆的抵抗性スイッチング素子、及びステアリング素子として炭素/トンネル障壁/炭素・ダイオードを含んでいてもよい。トンネル障壁は半導体又は絶縁体を含んでいてもよい。従って、ダイオードは炭素/半導体/炭素・ダイオードであってもよい。ダイオード内の半導体は真性であってもよいし、ドープされていてもよい。ダイオードが平衡状態にある場合は、半導体が空乏化されることがある。例えば、空乏領域が半導体領域の一端から他端まで延びるように、半導体が低濃度にドープされてもよい。ダイオードは炭素/絶縁体/炭素・ダイオードであってもよい。 (もっと読む)

発光ダイオード及びその製造方法

信頼性のある発光ダイオード及びその製造方法が開示される。本発明の一態様による発光ダイオードは、シリコンがドープされたn型コンタクト層と、p型コンタクト層と、n型コンタクト層とp型コンタクト層との間に介在する活性領域と、n型コンタクト層と活性領域との間に介在する超格子層と、超格子層とn型コンタクト層との間に介在する非ドープ中間層と、非ドープ層と超格子層との間に介在する電子補強層と、を備える。超格子層は、活性領域に最も近い最終層にのみ意図的にシリコンがドープされ、最終層のシリコンドーピング濃度は、n型コンタクト層のシリコンドーピング濃度よりも高い。活性領域に近く位置する超格子層の殆ど全ての層にシリコンを意図的にドープしていないので、漏れ電流を減少させることができ、活性領域に最も近い最終層に高濃度のシリコンをドープすることにより、接合特性が悪くなることを防ぎ、静電放電特性を改善できる。  (もっと読む)

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaN系の良質な半導体結晶層を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、窒素原子を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

ガリウム窒化物又は他の窒化物ベースの半導体デバイスの裏側応力補償

半導体基板(102)の第1の側の上に応力補償層(104)を形成すること(302)と、前記基板の第2の側の上にIII族窒化物層(108a、108b、110、112)を形成すること(304)を含む方法。III族窒化物層により前記基板上につくられる応力が、前記応力補償層により前記基板上につくられる応力によって少なくとも部分的に低減される(306)。前記応力補償層を形成することが、非晶質又は微結晶材料から応力補償層を形成することを含み得る。また、この方法は、前記基板の前記第2の側の上の一つ又は複数の層(106〜114)の後続の形成の間、前記非晶質又は微結晶材料を結晶化することを含み得る。前記非晶質又は微結晶材料の結晶化は、前記III族窒化物層の後続の形成の間及び/又はアニールプロセスの間に成され得る。前記非晶質又は微結晶材料は、前記基板上につくる応力が全くないか又は量が小さく、前記結晶化した材料が前記基板上に一層大きな応力をつくり得る。

(もっと読む)

(もっと読む)

化合物半導体基板とその製造方法

【課題】AlGaInP化合物半導体の成長温度を高くすることなく、低い酸素原子濃度を有し、表面欠陥の小突起が発生しにくいAlGaInP化合物半導体の製造方法、およびそれにより得られるAlGaInP化合物半導体基板を提供する。

【解決手段】筐体の内部に配置された反応炉の内部で化合物半導体基板を製造する方法であって、前記筐体の内部を酸素濃度が45ppm以下の雰囲気に保ったまま、ベース基板を筐体の内部であって反応炉の外部から、反応炉の内部に移動し、前記ベース基板を前記反応炉の内部に配置する段階(1)と、前記反応炉の内部に配置されたベース基板の上に化合物半導体を700℃以下でエピタキシャル成長させる段階(2)とを含む化合物半導体基板の製造方法。

(もっと読む)

窒化物半導体素子の製造方法

本発明は、窒化物半導体素子の製造方法に関する。本発明の窒化物半導体素子の製造方法は、第1支持基板上に窒化ガリウムエピ層を形成する段階と、前記窒化ガリウムエピ層上に第2支持基板を形成する段階と、前記第1支持基板を除いた残りの領域の表面にパッシベーション層を形成する段階と、前記パッシベーション層をマスクとして前記第1支持基板をエッチングする段階と、前記パッシベーション層を除去して前記第2支持基板および前記窒化ガリウムエピ層を露出させる段階とを含む。 (もっと読む)

注入効率が向上したLED

発光素子と該発光素子を作製する方法とを開示する。発光素子は、p型半導体層とn型半導体層との間に挟装された活性層を含む。活性層は、内部で、p型半導体層からの正孔がn型半導体層からの電子と結合するときに光を放出する。活性層は、複数の副層を含み、かつ複数の副層の側面がp型半導体材料と接触する複数のピットを有し、それにより、p型半導体材料からの正孔が、露出した側面を通ってそれらの副層内に、別の副層を通過することなく注入される。n型半導体層における転位を利用することと、部分的に製作された素子を取り除くことなく、半導体層を堆積させるために用いたものと同じチャンバー内で、エッチング雰囲気を用いて活性層をエッチングすることとにより、ピットを形成することができる。 (もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】エピタキシャル成長により形成された結晶膜の成長面内における物性値を均一な値に近づける。

【解決手段】第1化合物半導体および第2化合物半導体を積層した積層半導体を含み、前記第1化合物半導体の所定物性値が第1面内分布を有し、前記第2化合物半導体の前記所定物性値が前記第1面内分布とは異なる第2面内分布を有し、前記積層半導体における前記所定物性値の面内分布の幅が、前記第1面内分布の幅または前記第2面内分布の幅より小さい半導体基板を提供する。

(もっと読む)

フォトダイオードおよびその製造方法

【課題】GaN等の窒化物半導体薄膜を作製する基板として、非単結晶基板であるグラファイトを基板として使用するとGaN薄膜が多結晶となり結晶中の欠陥が多くなる為、フォトダイオードに使用することが出来なかった。

【解決手段】グラファイト基板上にアモルファスカーボン層を設け、アモルファスカーボン層上にMOCVD法によってAlNのc軸配向膜を成長させた後、AlN層上にGaNの低温成長バッファ層を形成し、低温成長バッファ層上にn型GaN層を形成し、n型GaN層上にInxGa1-xNあるいはAlyGa1-yNからなる光吸収層を形成し、光吸収層上にp型GaN層を形成し、p型GaN層上にp型GaNコンタクト層を形成することが可能となり、グラファイト基板上に直接フォトダイオードを作製することで低コストで優れた特性を有するフォトダイオードを実現できる。

(もっと読む)

III族窒化物半導体発光素子を作製する方法、III族窒化物半導体素子のための電極を形成する方法、及びIII族窒化物半導体素子

【課題】III族窒化物の露出エリアを絶縁膜の開口に対して良好な位置制御性で形成できる、III族窒化物半導体発光素子を作製する方法を提供する。

【解決手段】コンタクト層27及びクラッド層25を含むIII族窒化物半導体領域29をマスク35aを用いてエッチングして、III族窒化物領域33c及びエピタキシャル領域29bを形成する。次いで、マスク35a、パターン形成されたIII族窒化物リフトオフ層31a及びパターン形成されたIII族窒化物半導体領域33c上に絶縁膜39を成長する。絶縁膜39は、マスク35a上に成膜される第1の部分39aと、パターン形成されたIII族窒化物半導体領域33c上に成膜される第2の部分39bとを含む。引き続き、パターン形成されたIII族窒化物リフトオフ層31aを絶縁膜39に対してエッチャントを用いて選択的に除去して、リフトオフ法により、開口39cを有する絶縁膜39bを形成する。

(もっと読む)

多段エピタキシャル方式による超接合半導体装置の製造方法

【課題】アライメントマーカーの形成後に行うシリコンエピタキシャルの成長速度を、通常の条件より遅くすることなく、アライメントマーカーのパターン形状精度の低下を防ぎ、超接合半導体装置を低オン抵抗にするために用いられる低抵抗砒素ドープシリコン基板からのオートドーピングを防止する多段エピタキシャル方式による超接合半導体装置の製造方法を提供すること。

【解決手段】低抵抗砒素ドープシリコン基板に多段エピタキシャル方式によるエピタキシャル成長とイオン注入を繰り返し実施する際にパターニングに用いられるアライメントマーカーを、前記エピタキシャル成長面とは反対側の裏面に設けた酸化膜の膜厚を選択的に減厚して形成した段差からなる凸部又は凹部として形成する。

(もっと読む)

光電変換装置及びその製造方法

【課題】i層に微結晶シリコンゲルマニウムを用いたpin型光電変換層を備えた光電変換装置及びその製造方法において、i層のゲルマニウム濃度の増加に伴う発電特性の低下を抑制する。

【解決手段】p型シリコン系半導体の層を製膜する工程、i型シリコン系半導体の層を製膜する工程、及びn型シリコン系半導体の層を製膜する工程によりpin接合を形成して光電変換層を形成する光電変換装置の製造方法であって、i型シリコン系半導体の層を製膜する工程が、微結晶シリコンゲルマニウムの層を100℃以上160℃以下の製膜温度でプラズマCVD法により製膜する工程である。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】しきい値電圧の経時変化およびホットキャリア劣化が可及的に小さく、かつオン特性の低下が可及的に小さい薄膜トランジスタおよびその製造方法を提供する。

【解決手段】ゲート電極32上に、ゲート絶縁膜36として、第1ゲート絶縁膜50と、第2ゲート絶縁膜51とを形成する。第1ゲート絶縁膜50を窒化シリコン膜で形成し、第2ゲート絶縁膜51を酸化シリコン膜で形成し、第2ゲート絶縁膜51の表面部にAr含有層52を形成する。Ar含有層52に接するように、微結晶シリコン膜62を形成し、さらにi型非晶質シリコン膜63およびN型非晶質シリコン膜61を形成して、活性層37を形成する。これによって、高密度に均一に結晶を成長させることができるので、均一でボイドの少ない微結晶シリコン膜62を形成することができる。

(もっと読む)

SiC結晶成長層の製造方法およびバイポーラ型半導体素子

【課題】層厚さが厚くてもSiC結晶中にある炭素空孔を低減できるSiC結晶成長層の製造方法を提供する。

【解決手段】SiC結晶成長層としてのドリフト層23を成長させる工程内に、シリコン原料ガスであるシランと炭素原料ガスであるプロパンのうちのプロパンのみを結晶成長表面に供給する第2の期間を設けている。このことで、結晶成長表面の炭素の過飽和度を上げ、成長途中の表面に過剰な格子間炭素を発生させる。これにより、成長後のSiC結晶成長層としてのドリフト層23の表面から離れている比較的深い箇所での炭素空孔を減少させることができる。

(もっと読む)

窒化物半導体デバイス

【課題】 ウエハ−プロセスで基板の上に製造された素子単位をチップ分離する際に研磨、切断などの工程を減らすことができ、基板を繰り返し使用できる窒化物半導体デバイス作製方法によって作製したデバイスを提供する。

【解決手段】 閉曲線をなす結晶成長速度の遅い欠陥の集合した欠陥集合領域Hと結晶成長速度の速い低欠陥の領域ZYの位置が予め決まっている窒化物半導体欠陥位置制御基板Sを用い、低欠陥領域ZYにデバイスの内部が、欠陥集合領域Hに境界線が来るように窒化ガリウム基板の上に窒化物半導体層(上層部B)をエピタキシャル成長させ、レーザ照射或いは機械的手段で欠陥位置制御基板Sと成長層(上層部B)を上下方向横方向に同時分離し、基板は繰り返し使用する。作製されたデバイスは端面が成長によるファセットで形成されている。

(もっと読む)

化合物半導体エピタキシャルウェハ及びその製造方法、並びにHEMT素子

【課題】化合物半導体エピタキシャルウェハ外周部より得られたHEMT素子であってもリーク電流の急激な増加がなく、良好な耐圧を持つHEMT素子が得られる化合物半導体エピタキシャルウェハ及びその製造方法、並びにこのような化合物半導体エピタキシャルウェハを用いて得られるHEMT素子を提供する。

【解決手段】基板1上に、バッファ層3と、下部電子供給層4と、電子走行層5と、上部電子供給層6と、を有する化合物半導体エピタキシャルウェハ10において、前記バッファ層3はAlGaAsからなり、前記下部電子供給層4及び前記上部電子供給層6はAlGaAsからなり、前記下部電子供給層4及び前記上部電子供給層6のAl組成が0.2

0以上0.27以下であり、かつ前記バッファ層3のAl組成が前記下部電子供給層4の

Al組成より小さい。

(もっと読む)

化合物半導体装置

【課題】電流コラプスを低減させてRF特性を改善し、携帯電話基地局用アンプに必要とされる耐圧を得ることを可能とする。

【解決手段】 AlGaN層3を成長形成するに際して、i−GaN層2上にノンドープでAl組成率が15%程度のAlGaN層(i−AlGaN層)11を膜厚3nm程度に成長し、更にSiを濃度2×1018/cm3程度にドープしたAl組成率が15%程度のAlGaN層(n−AlGaN層)12を膜厚17nm程度に成長し、これら2層構造からなるAlGaN層3を形成する。

(もっと読む)

ZnO系化合物半導体の製造方法及び半導体発光素子

【課題】 安定したp型ZnO系半導体結晶を得ることが可能なZnO系化合物半導体の製造方法を提供する。

【解決手段】 ZnO系化合物半導体の製造方法は、単結晶表面を有する基板を準備する工程と、亜鉛ビームと、酸素を含むガスをラジカル化した酸素ラジカルビームと、N2ガスとO2ガスとを混合したガスをラジカル化した窒素ラジカルビームとを、前記基板上に同時に照射して、窒素添加p型ZnO系化合物半導体を結晶成長する工程とを有し、前記N2ガスとO2ガスとを混合したガスの混合比O2/N2が、0より大きく1以下である。

(もっと読む)

161 - 180 / 532

[ Back to top ]