Fターム[5F045DA52]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の形状、構造 (2,125) | 多層成長層 (2,091)

Fターム[5F045DA52]の下位に属するFターム

バッファ層・中間層・遷移層を有するもの (1,084)

超格子(歪超格子、変調ドープ超格子を含む) (99)

量子井戸 (345)

量子細線・量子箱 (31)

Fターム[5F045DA52]に分類される特許

81 - 100 / 532

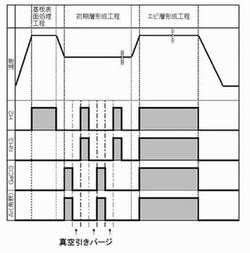

基板の製造方法、半導体デイバスの製造方法及び基板処理装置

【課題】一度に処理する基板の枚数を増大させ、GaNのエピタキシャル膜の生産性を向上させることができる膜の形成方法及び基板処理装置を提供する。

【解決手段】基板を処理室内に搬入する搬入工程と、前記処理室内にガリウム塩化物ガスを供給する第1ステップと、前記処理室から前記ガリウム塩化物ガスをパージする第1パージステップと、前記第1パージステップの後に前記処理室内にアンモニアガスを供給する第2ステップと、前記処理室から前記アンモニアガスをパージする第2パージステップとを有する初期膜形成工程と、前記初期膜形成工程の後に、前記処理室内に前記ガリウム塩化物ガスと前記アンモニアガスを同時に供給し、エピタキシャル膜を形成するエピ膜形成工程とによりGaN膜を形成する。

(もっと読む)

裏面照射型固体撮像素子用エピタキシャル基板およびその製造方法

【課題】裏面照射型固体撮像素子をより高い歩留まりで製造することが可能なエピタキシャル基板およびその製造方法を提供する

【解決手段】本発明の裏面照射型固体撮像素子用エピタキシャル基板100は、炭素、または、炭素および窒素が添加され、抵抗率が100Ω・cm未満であるp型シリコン基板1と、該p型シリコン基板上のp型第1エピタキシャル層2と、該第1エピタキシャル層上のp型またはn型第2エピタキシャル層3と、を有し、前記第1エピタキシャル層2は、p型不純物のピーク濃度が2.7×1017atoms/cm3以上1.1×1019atoms/cm3未満であることを特徴とする。

(もっと読む)

表面波プラズマCVD装置および成膜方法

【課題】1台の表面波プラズマCDV装置を用いて、組成および厚さの異なる薄膜を基板に連続成膜し、高スループットで超構造膜を形成する。

【解決手段】本発明は、共通の真空室内において基板に複数の薄膜を成膜する表面波プラズマCVD装置であって、この基板に成膜を行う複数のプラズマ生成ユニットと、各々のプラズマ生成ユニットに設けられた、プラズマ生成ガスを放出するプラズマ生成ガス放出口と成膜ガスを放出する成膜ガス放出口と、これら複数のプラズマ生成ユニットで成膜を行う成膜領域を真空室内で互いに隔てる隔壁と、各々のプラズマ生成ユニットの成膜領域の間で基板を移動可能に戴置可能とする移動手段とを備える。

(もっと読む)

酸化亜鉛系半導体の成長方法

【目的】

p型ドーパント濃度の制御性に優れ、高品質なp型ZnO系結晶の成長方法を提供する。

【解決手段】

MOCVD法により、分子構造中に酸素原子を含まない有機金属化合物と極性酸素材料とを用いてZnO系結晶層を成長する単結晶成長工程を有し、上記単結晶成長工程は、TBP(ターシャリーブチルホスフィン)を供給する工程を有する。

(もっと読む)

ZnO系半導体層の製造方法及びZnO系半導体発光素子の製造方法

【課題】ZnO系半導体層の新規な製造方法を提供する。

【解決手段】(a)基板上方に、(MgxZn1−x)3N2(0≦x≦0.6)単結晶膜を成長させる工程と、(b)前記の(MgxZn1−x)3N2(0≦x≦0.6)単結晶膜を、400℃以下で、活性酸素により酸化して、MgyZn1−yO(0≦y≦0.6)単結晶膜を形成する工程と、(c)工程(a)及び(b)を繰り返して、MgyZn1−yO(0≦y≦0.6)単結晶膜を積層する工程とを有するZnO系半導体層の製造方法とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を容易に実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1上方に形成されたAlGaN層3と、AlGaN層3上に形成されたAlGaN層4と、AlGaN層4上に形成された電子走行層5と、電子走行層5上方に形成された電子供給層6と、が設けられている。AlGaN層3の組成をAlx1Ga1-x1N、AlGaN層4の組成をAlx2Ga1-x2Nと表すと、「0≦x1<x2≦1」の関係が成り立つ。AlGaN層4の上面には、AlGaN層4の下面に存在する正の電荷よりも多くの負の電荷が存在している。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

結晶性半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性半導体の核生成を均一にする。

【解決手段】ガス管から導入された成膜ガスを拡散する第2のガス拡散室と、前記第2のガス拡散室と分散板を隔てて設けられ、該分散板のガス孔から成膜ガスが導入される第1のガス拡散室と、を介して、前記第1のガス拡散室とシャワー板を隔てて設けられた処理室内に該シャワー板のガス孔から成膜ガスを供給し、前記成膜ガスを導入することによって前記処理室内の圧力を2000Pa以上100000Pa以下とし、前記処理室内に電界を生じさせる一対の電極のうち、一方の電極面から電界強度が均一な高周波電力を供給することでグロー放電プラズマを生成させ、前記対向する電極の他方に配された基板上に結晶核を生じさせ、その後、該結晶核を成長させて結晶性半導体膜を作製する。

(もっと読む)

シリコン発光素子に用いる活性層およびその活性層の製造方法

【課題】 基板の面内方向のキャリア拡散と基板垂直方向のキャリア注入を高効率に行うことのできる、シリコン発光素子用の活性層および該活性層の製造方法の提供を目的とする。

【解決手段】 シリコン発光素子に用いる活性層であり、シリコン化合物からなる第1の層と、該第1の層よりもバンドギャップが大きいシリコン化合物からなる第2の層とが基板上に交互に積層された多層膜構造を有する。また、複数のシリコンナノ粒子が多層膜構造の中に設けられている。第1の層に含まれるシリコン原子の量は、第2の層に含まれるシリコン原子の量よりも多く、複数のシリコンナノ粒子のうちの少なくとも一つは、前記第1の層と前記第2の層との境界面のうち少なくとも一つの面を越えて存在する。

(もっと読む)

基板上に堆積された窒化ガリウムフィルムにおける応力の制御方法

【課題】シリコンおよび炭化ケイ素基板上に堆積されたGaNフィルムにおける応力の制御方法、およびこれによって生成されたGaNフィルムを提供する。

【解決手段】典型的な方法は、基板を供給すること、および供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上にグレーデッド窒化ガリウム層を堆積させることを含む。典型的な半導体フィルムは、基板と、供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上に堆積されたグレーデッド窒化ガリウム層とを含む。

(もっと読む)

半導体装置

【課題】化合物半導体上のp型チャネルFETにおいてオン抵抗を低くすることの可能な半導体装置を提供する。

【解決手段】化合物半導体からなる基板10上に、n型チャネルFET領域2とp型チャネルFET領域3とが併設されている。p型チャネルFET領域3において、チャネル層16の下面に接するバッファ層15が、チャネル層16よりも広いバンドギャップを有する第2バッファ層15Bだけで構成された単層構造となっている。さらに、第2バッファ層15Bは、チャネル層16と電子走行層13との間に設けられている。

(もっと読む)

発光素子用エピタキシャルウェハ、及び発光素子

【課題】信頼性を向上させた発光素子用エピタキシャルウェハ、及び発光素子を提供する。

【解決手段】発光素子用エピタキシャルウェハは、n型基板1上に、少なくともP(燐)系結晶のn型クラッド層3、AlxGa(1−x)As、又はGaAsなどのAs(砒素)系結晶で形成した量子井戸構造を有する発光層5、及びp型クラッド層7が順次積層された化合物半導体と、n型クラッド層3と発光層5との間に、発光層5を構成するAlxGa(1−x)As層とは異なるAlxGa(1−x)As層4とを有している。

(もっと読む)

太陽電池の薄膜蒸着装置、方法及びシステム

【課題】太陽電池の薄膜蒸着装置、システム、それを利用した太陽電池の製造方法及び異種接合の太陽電池の製造方法、並びにこれによって製造された異種接合の太陽電池を提供する。

【解決手段】太陽電池の薄膜蒸着装置は、基板Wを境界として区分される複数個の単位チャンバー110a,110bと、複数個の単位チャンバーに蒸着ガスG1,G2を独立的に注入させるための蒸着ガス注入部120a,120bと、前記単位チャンバー内にそれぞれ備えられ、前記注入された蒸着ガスを分解するための分解手段130a,130bと、を備え、前記基板の両面それぞれは、前記複数個の単位チャンバーに露出され、太陽電池の薄膜蒸着装置及びそれを利用した製造方法は、基板の回転なしに固定された状態で基板の両面蒸着を可能にする。したがって、一面に対して一層のみが積層される従来の技術に比べて、要求される設備の数が画期的に減ることができる。

(もっと読む)

光電素子及びその製造方法

【課題】本発明は光電素子及びその製造方法を提供する。

【解決手段】本発明による光電素子であって、表面及び表面と垂直する法線方向を有する基板と、基板の表面に位置して表面と接触する第一半導体層と、第一半導体層と基板の表面の間に位置する少なくとも一つの空洞構造とを有し、少なくとも一つの空洞構造は幅と高さを有し、幅は空洞構造における表面に平行する方向の最大寸法であり、高さは空洞構造における法線方向に平行する方向の最大寸法であり、高さは幅より小さい。

(もっと読む)

半導体発光素子の製造方法及び半導体結晶成長装置

【課題】基板表面内で半導体層の組成が均一な半導体発光素子を提供する。

【解決手段】半導体発光素子の製造方法は、加熱手段の上に配置されたトレイ1の、前記加熱手段とは反対側の表面上にある基板搭載部3に搭載された基板4上に、III族元素とV族元素とからなる化合物半導体の積層構造を有機金属気相成長法により成長する工程を含む。前記化合物半導体の積層構造を構成する少なくとも1つのIII族元素と、前記化合物半導体層の積層構造を構成する少なくとも1つのV族元素と、を有する化合物半導体膜2が、前記積層構造の成長前に予め前記基板搭載部3の表面上に形成されている。前記基板4が、前記化合物半導体膜2を介して前記基板搭載部3に搭載されて、前記積層構造が前記基板4上に成長される。

(もっと読む)

III族窒化物半導体光素子、III族窒化物半導体光素子を形成する方法、III族窒化物半導体膜を成長する方法及びエピタキシャル基板

【課題】p型III族窒化物半導体の電気特性を向上できるIII族窒化物半導体光素子を提供する。

【解決手段】窒化ガリウム系半導体領域15及び窒化ガリウム系半導体領域19は、基板13の主面13a上に設けられる。窒化ガリウム系半導体領域19は、p型ドーパントとしてマグネシウムを含むIII族窒化物半導体膜21を有しており、III族窒化物半導体膜21は、III族構成元素としてアルミニウムを含む。III族窒化物半導体膜21の酸素濃度は、1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の酸素濃度は、1.5×1018cm−3以下の範囲にある。また、III族窒化物半導体膜21の水素濃度は1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の水素濃度は1.5×1018cm−3以下の範囲にある。

(もっと読む)

へテロ接合トランジスタ及びその製造方法

【課題】チャネル層中のキャリア濃度を増すため、高いアルミニウム含有率を有した厚いAlGaN層は、成長中か冷却後にひびが入る傾向があり、これによってデバイスが破壊される。

【解決手段】基板上の第1のIII族窒化物層は第1の歪みを有する。GaN層のような第2のIII族窒化物層が、第1のIII族窒化物層上に設けられている。第2のIII族窒化物層は、第1のIII族窒化物層のバンドギャップよりも小さなバンドギャップを有し、かつ第1の歪みの大きさよりも大きい第2の歪みを有する。AlGaN層又はAlN層のような第3のIII族窒化物層がGaN層上に設けられている。第3のIII族窒化物層は、第2のIII族窒化物層のバンドギャップよりも大きなバンドギャップを有し、かつ第2の歪みと逆の歪みの型の第3の歪みを有する。ソースコンタクトとドレインコンタクトとゲートコンタクトを第3のIII族窒化物層上に設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

窒化化合物半導体構造のエピタキシャル成長

【課題】窒化化合物半導体構造を製造する装置及び方法を提供する。

【解決手段】III族及び窒素の前駆物質が、第1の処理チャンバに流入されて、熱化学気相堆積プロセスを用いて、基板上に第1の層が堆積される。該基板は、該第1の処理チャンバから第2の処理チャンバへ移送される。II族及び窒素の前駆物質が、該第2の処理チャンバに流入されて、熱化学気相堆積プロセスを用いて該第1の層を覆って第2の層が堆積される。該第1及び第2のIII族前駆物質は、異なるIII族元素を有する。

(もっと読む)

発光素子

【課題】光取り出し効率を向上させることのできる発光素子を提供する。

【解決手段】発光素子1は、第1半導体層と、第2半導体層と、第1半導体層と第2半導体層とに挟まれる発光層とを有する半導体積層構造10と、半導体積層構造10の一方の面上に設けられ、線状表面電極部を有する表面電極50と、半導体積層構造10の表面電極50が設けられる側の反対の面側に設けられ、光を反射する反射層32と、半導体積層構造10と反射層32との間に設けられる誘電体層と、半導体積層構造10と反射層32とを電気的に接続し、線状界面電極部を有する界面電極40とを備え、線状表面電極部と線状界面電極部とがそれぞれ、平面視にて予め定められた方向に沿って延び、半導体積層構造10が、半導体積層構造10の反射層32の反対側の表面に、予め定められた方向とは異なる方向に沿って設けられる溝80を有する。

(もっと読む)

81 - 100 / 532

[ Back to top ]