Fターム[5F045DA52]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の形状、構造 (2,125) | 多層成長層 (2,091)

Fターム[5F045DA52]の下位に属するFターム

バッファ層・中間層・遷移層を有するもの (1,084)

超格子(歪超格子、変調ドープ超格子を含む) (99)

量子井戸 (345)

量子細線・量子箱 (31)

Fターム[5F045DA52]に分類される特許

21 - 40 / 532

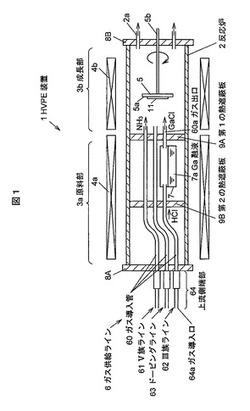

金属塩化物ガス発生装置、ハイドライド気相成長装置、及び窒化物半導体テンプレート

【課題】意図しない不純物の混入を抑制した金属塩化物ガス発生装置、ハイドライド気相成長装置、及び窒化物半導体テンプレートを提供する。

【解決手段】金属塩化物ガス発生装置としてのHVPE装置1は、Ga(金属)7aを収容するタンク(収容部)7を上流側に有し、成長用の基板11が配置される成長部3bを下流側に有する筒状の反応炉2と、ガス導入口64aを有する上流側端部64からタンク7を経由して成長部3bに至るように配置され、上流側端部64からガスを導入してタンク7に供給し、ガスとタンク7内のGaとが反応して生成された金属塩化物ガスを成長部3bに供給する透光性のガス導入管60と、反応炉2内に配置され、ガス導入管60の上流側端部64を成長部3bから熱的に遮断する熱遮蔽板9A、9Bとを備え、ガス導入管60は、上流側端部64と熱遮蔽板9Bとの間で屈曲された構造を有する。

(もっと読む)

表示装置およびその製造方法

【課題】微結晶シリコンを用いたボトムゲート型の薄膜トランジスタのオン電流に対するオフ電流の割合を減少させること。

【解決手段】表示装置に含まれる薄膜トランジスタは、ゲート電極が設けられた導電層と、前記導電層の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上面に接するとともに前記ゲート電極の上方に設けられ、微結晶シリコンを含む第1の半導体膜と、前記第1の半導体膜の上面に接する第2の半導体膜と、前記第2の半導体膜に電気的に接続される第1の電極と、前記第2の半導体膜に電気的に接続される第2の電極と、を含む。前記第1の半導体膜における水素濃度は、前記ゲート絶縁層との界面と前記第2の半導体膜との界面との中間で最小となり、前記第1の半導体膜と前記第2の半導体膜との境界における酸素濃度は、前記第1の半導体膜の中央および前記第2の半導体膜の中央のうち少なくとも一方の酸素濃度以下である。

(もっと読む)

成膜方法及び記憶媒体

【課題】プラズマCVD法を用いて、例えば太陽電池の発電層となるシリコン膜を成膜するにあたって、シリコン膜の結晶性を制御することができる成膜方法を提供すること。

【解決手段】水素ガスとモノシランガスとを予め混合し、この混合ガスをプラズマ化して、基板S上にシリコン膜F1を成膜する第1の工程(プリミックス)と、水素ガスとモノシランガスとを別々に供給してプラズマ化し、シリコン膜F2を成膜する第2の工程(ポストミックス)とを組み合わせる。組み合わせの例としては、基板S上にプリミックスによりシリコン膜F1を成膜しそのシリコン膜F1上にポストミックスによりシリコン膜F2を成膜する方法、基板S上にシリコン膜F1及びF2を交互に複数回成膜する方法などが挙げられる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

化合物半導体基板

【課題】化合物半導体層全体の膜厚を抑制しつつ、半導体素子の高い性能と信頼性を両立することのできる化合物半導体基板を提供する。

【解決手段】シリコン単結晶の基板12と、基板上に形成される化合物半導体の第1の半導体層16と、第1の半導体層上に形成され、第1の半導体層よりもバンドギャップエネルギーの大きい、化合物半導体の障壁層18と、障壁層上に形成され、障壁層よりもバンドギャップエネルギーの小さい化合物半導体の第2の半導体層20と、第2の半導体層上に形成され、第2の半導体層よりもバンドギャップエネルギーの大きい化合物半導体の第3の半導体層22とを有することを特徴とする化合物半導体基板。

(もっと読む)

半導体基板および電子デバイス

【課題】窒化物半導体からなる活性層にn型不純物原子をドーピングした場合であっても、活性層に発生する転位を減少することができる技術、あるいは、活性層の結晶破壊を抑制することができる技術を提供する。

【解決手段】ベース基板と、第1結晶層と第2結晶層とが交互に複数積層された積層構造体と、第3結晶層とを有し、前記ベース基板、前記積層構造体および前記第3結晶層が、前記ベース基板、前記積層構造体、前記第3結晶層の順に位置し、前記第1結晶層が、AlxGa1−xN、(但し0≦x≦1)からなり、前記第2結晶層が、AlyGa1−yN、(但し0≦y≦1、x≠y)からなり、前記第3結晶層が、AlzGa1−zN、(但し0≦z≦1)からなり、前記第1結晶層、前記第2結晶層および前記第3結晶層にシリコン原子を含む半導体基板を提供する。

(もっと読む)

窒化ガリウム整流素子

【課題】経時劣化が少なく、低損失(バリガ性能指数が1.5GW/cm2以上)の窒化ガリウム整流素子を提供する。

【解決手段】窒化ガリウム整流素子1は、pn接合を形成するp型窒化ガリウム系半導体層及びn型窒化ガリウム系半導体層を備え、前記p型窒化ガリウム系半導体層のキャリアトラップ準位密度が1×1018cm-3以下、又は前記n型窒化ガリウム系半導体層のキャリアトラップ準位密度が1×1016cm-3以下である。

(もっと読む)

シリコン膜の形成方法およびその形成装置

【課題】ボイドやシームの発生を抑制することができるシリコン膜の形成方法およびその形成装置を提供する。

【解決手段】シリコン膜の形成方法は、第1成膜工程と、エッチング工程と、ドープ工程と第2成膜工程とを備えている。第1成膜工程では、被処理体の溝を埋め込むように不純物でドープされていないノンドープシリコン膜を成膜する。エッチング工程では、第1成膜工程で成膜されたノンドープシリコン膜をエッチングする。ドープ工程では、エッチング工程でエッチングされたノンドープシリコン膜を不純物でドープする。第2成膜工程では、ドープ工程でドープされたシリコン膜を埋め込むように、不純物がドープされたシリコン膜を成膜する。

(もっと読む)

プラズマCVD装置を用いた半導体装置の製造方法

【課題】プラズマCVD装置を用いた半導体装置の製造方法に関し、製膜室のクリーニング後に、仮製膜を行った際に堆積する膜の剥離を防ぎ、半導体薄膜中に堆積膜が混入することを防ぐ方法を提供する。

【解決手段】プラズマCVD装置を用いた半導体装置の製造方法においては、仮製膜の際に結晶質シリコン薄膜を用いている。仮製膜の際に、結晶質シリコン薄膜を用いることで、堆積膜が半導体薄膜の膜中に取り込まれることを防ぐことが可能となった。

(もっと読む)

トランジスタ用半導体基板、トランジスタ及びトランジスタ用半導体基板の製造方法

【課題】リーク電流が小さく、かつ、ノーマリオフ動作をするデバイスに適した半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられた、IIIa族元素を含む窒化物の第1結晶からなる第1エピタキシャル結晶層と、第1エピタキシャル結晶層上に設けられ、第1結晶よりも大きなバンドギャップを有し、かつ、IIIa族元素及びIIIa族元素の一部を置換したIIIb族元素を含む窒化物の第2結晶からなる第2エピタキシャル結晶層とを備える半導体基板を提供する。上記の半導体基板において、第2エピタキシャル結晶層は、第1エピタキシャル結晶層に格子整合又は疑格子整合してもよい。

(もっと読む)

半導体装置の製造方法

【課題】高周波数動作が可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、成長炉内に配置した基板10上に、GaN電子走行層16を成長する工程と、成長炉に導入する混合ガス中の窒素原料ガスの分圧比を0.15以上0.35以下として、GaN電子走行層16上に、InAlN電子供給層18を成長する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体エピ薄膜の成長方法及びこれを用いた半導体発光素子の製造方法

【課題】反応ガスを供給するノズルが詰まる現象を緩和して工程効率及び生産性を向上させた半導体エピ薄膜の成長方法及びこれを用いた半導体発光素子の製造方法を提供する。

【解決手段】本発明の半導体エピ薄膜の成長方法は、ウェハーホルダーに積載された複数のウェハーを反応チャンバの内部に配置する段階と、ウェハーの積載方向に沿って延長されて備えられたガス供給部を通じて塩素系有機金属化合物を含む反応ガスをウェハーに噴射し、各ウェハーの表面に半導体エピ薄膜を成長させる段階と、を有する。

(もっと読む)

窒化物半導体基板の製造方法

【課題】低転位であり、特に、窒化物半導体基板に内在する応力を抑制させて、反りの少ない窒化物半導体基板の製造方法を提供することを目的とする。

【解決手段】サファイア基板の(0001)面上に、第1の窒化物半導体パターンを形成し、該第1の窒化物半導体パターンを成長核として第2の窒化物半導体層を成長させ、少なくとも前記サファイア基板を除去することを含む窒化物半導体基板の製造方法であって、第1の窒化物半導体パターンは、平面形状が三角形の複数の枠体によって形成され、該枠体の頂点のみを、隣接する枠体と共有するように規則的に配置されて構成される窒化物半導体基板の製造方法。

(もっと読む)

p型化合物半導体層の形成方法

【課題】p型化合物半導体層の形成の際に、p型不純物と水素の結合を遮断するp型化合物半導体層の形成方法を、提供する。

【解決手段】

p型化合物半導体層の形成方法が開示される。この方法では、反応チェンバ内に、III族元素のソースガス、p型不純物のソースガス、及び水素を含有する窒素のソースガスを供給し、p型化合物半導体層を成長させる。また、p型化合物半導体層の成長が完了した後、III族元素のソースガス及びp型不純物のソースガスの供給を中断し、基板の温度が400〜900℃である間に、水素を含有する窒素のソースガスの供給を中断及び排出し、冷却ガスで常温まで冷却させる。これにより、基板の温度を冷却させる過程で、p型化合物半導体層に含まれたp型不純物に水素が結合することを防ぐことができる。

(もっと読む)

薄膜光電変換装置

【課題】結晶質シリコン光電変換層を含む薄膜光電変換装置の開放電圧、短絡電流密度を増加して光電変換効率を改善した薄膜光電変換装置を提供する。

【解決手段】結晶質シリコン光電変換ユニット4の一導電型層41と光電変換層42との間に、実質的に真性なシリコン複合層からなる界面層44を配置し、実質的に真性なシリコン複合層からなる界面層44は非晶質酸素化シリコン母相中に結晶シリコン相が分散している層で形成されている。

(もっと読む)

III族窒化物半導体発光素子の製造方法

【課題】III 族窒化物半導体発光素子において、光取り出し効率を向上させること。

【解決手段】発光層14上に、MOCVD法によってp−AlGaNからなるpクラッド層15を形成する。圧力30kPa、Mg濃度は1.5×1020/cm3 とする。これにより、III 族元素極性の結晶に窒素極性の領域が多数生じ、pクラッド層15の表面は六角柱状の凹凸形状となる。次に、pクラッド層15上に、MOCVD法によって凹凸形状に沿って膜状にGaNからなるpコンタクト層16を形成する。

(もっと読む)

化合物半導体結晶の製造方法

【課題】複雑な作製工程を必要とせずに、均一に高品質な結晶が形成できるようにする。

【解決手段】まず、III−V族化合物半導体の単結晶からなる基板101の主表面におけるテラスの幅を、主表面の(100)面からの傾斜角度により制御する。この制御では、後述する第3工程で形成する第2半導体層103の第2原子間隔と、基板101の主表面における第1原子間隔と、自然数Nとを用いて表されるN×第1原子間隔≒(N−1)×第2原子間隔の関係が成立する条件で、テラスの幅がN×第1原子間隔となる状態に基板101の主表面を傾斜させる。なお、第2原子間隔は、第1原子間隔と同じ方向の、第2半導体層103を構成する原子の間隔である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】シリコン基板上に形成される、低転位密度で結晶品質が優れた窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、下地層と、機能層と、を備えた窒化物半導体層が提供される。下地層は、シリコン基板の上に形成されたAl含有窒化物半導体層の上に形成され、不純物濃度が低く、GaNを含む。機能層は、下地層の上に設けられる。機能層は、下地層の不純物濃度よりも高い不純物濃度を有し第1導電形のGaNを含む第1半導体層を含む。Al含有窒化物半導体層は、多層構造体を含む。多層構造体は、Alを含む窒化物半導体を含む複数の第2層と、複数の第2層の間に設けられ第2層におけるAl組成比よりも低いAl組成比を有する窒化物半導体を含む第1層と、を含む。下地層の厚さは、第1層の厚さよりも厚く、第1半導体層の厚さよりも薄い。

(もっと読む)

プラズマCVD装置

【課題】プラズマCVD装置の電極面積が大きくなると、表面定在波の影響が顕著に現れ

るようになり、ガラス基板に形成される薄膜の膜質や厚さの面内均一性が損なわれるとい

ったことが問題となる。

【解決手段】反応室内にグロー放電プラズマを生成する電極に周波数の異なる二以上の高

周波電力を供給する。周波数の異なる高周波電力を供給してグロー放電プラズマを生成し

、半導体若しくは絶縁体の薄膜を形成する。好ましくは周波数の異なる高周波電力を供給

する場合と、一の周波数の高周波電力を供給する場合とを自在に切替える。周波数の異な

る(波長が異なる)高周波電力をプラズマCVD装置の電極に重畳印加することで、プラ

ズマの高密度化と、プラズマの表面定在波効果が生じないように均一化を図る。

(もっと読む)

21 - 40 / 532

[ Back to top ]