Fターム[5F046EA11]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマーク (981) | 断面形状、断面構造、材質 (301)

Fターム[5F046EA11]の下位に属するFターム

マークが凹部 (81)

マークが凸部 (40)

マーク表面材質 (106)

複数の積層した材質層からなるもの (42)

マークが結晶面で構成されているもの (10)

貫通穴 (4)

Fターム[5F046EA11]に分類される特許

1 - 18 / 18

半導体装置の製造方法

【課題】追加工程なしに、厚い酸化膜の段差を緩和してマスクアライメントのアライメント精度を高くすることのできる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1上にドリフト層を、エピタキシャル成長とパターンアライメントによる選択的イオン注入とにより並列pn層として形成し、該並列pn層を所要の厚さとするために前記エピタキシャル成長とイオン注入とを所定の繰り返し回数行って積層する際に、エピタキシャル層の表面に形成する凹状のアライメントマーク3と同時に周縁耐圧構造部に耐圧部凹部4を形成した後、最終段のエピタキシャル層2fの表面に転写された前記耐圧部凹部4の深さを埋めるフィールド酸化膜5aを形成する工程を有する半導体装置の製造方法とする。

(もっと読む)

テンプレート、テンプレートの形成方法及び半導体装置の製造方法

【課題】ウェハとテンプレートとの位置合わせの精度を向上する。

【解決手段】本実施形態のテンプレートは、基板10上に設けられ、ウェハに転写されるパターンに対応するパターン部11と、基板10上に設けられ、ウェハとの位置合わせに用いられ、基板10の屈折率より高い屈折率を有するアライメントマーク部11と、を含む。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】製造工程が増加したり複雑化したりすることなく、SiC半導体基板とマスクとの位置合わせを高精度に行うことができるSiC半導体装置の製造方法を提供する。

【解決手段】アライメントマーク形成領域R1に、開口部の形状が、オフ方向に対して対称であり、かつオフ方向の最も下流側に位置する部分に頂点を有する多角形状とされており、アライメントマークとなるトレンチ12を形成するトレンチ形成工程と、トレンチ形成工程を行った後、SiC半導体基板10に対して、エピタキシャル層13を成長させるエピタキシャル層成長工程、または熱処理する熱処理工程の少なくともいずれか一方を行う工程と、エピタキシャル層成長工程または熱処理工程の少なくともいずれか一方の工程を行った後、アライメントマークを基準としたマスク合わせによってSiC半導体基板10にマスクを配置する工程と、を含むSiC半導体装置の製造方法とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】透過膜に覆われた状態でも画像認識精度の低下を抑制し得るアライメントマークを備えた半導体装置、および半導体装置の製造方法を得る。

【解決手段】アライメントマーク11のマーク本体領域15にストライプ状の周期構造を形成する。その周期構造により、位置合わせのための撮像時の照射光の反射が大幅に抑制され、マーク本体領域15の輝度が低くなる。一方、マーク本体領域15の周囲のベース領域17は、反射性に優れ、輝度が高くなる。その結果、コントラストが良好になり、画像認識精度が向上する。さらに、マーク本体領域15での照射光の反射が大幅に抑制されるため、アライメントマーク11を光透過性の膜が覆っている場合でも、薄膜による干渉等によってコントラストが低下しにくくなっており、画像認識精度の低下を抑制し得る。

(もっと読む)

アライメント測定構成、アライメント測定方法、デバイス製造方法及びリソグラフィ装置

【課題】マークごとの変化の影響が低減されたアライメント構成及びアライメント方法を提供する。

【解決手段】アライメント測定構成は、光源、光学システム及び検出器を含む。光源は、複数の波長範囲を含む放射ビームを生成する。光学システムは、放射ビームを受光し、アライメントビームを生成し、アライメントビームをオブジェクト上に位置するマークに誘導し、そのマークから戻るアライメント放射を受光し、受光した放射を伝送する。検出器は、アライメント放射を受光し、アライメントマークの画像を検出し、各々が波長範囲の1つに関連付けられた複数のアライメント信号rを出力する。プロセッサは、検出器と通信し、アライメント信号を受信し、アライメント信号の信号品質を決定し、アライメント信号の整列位置を決定し、信号品質、整列位置、及び整列位置を波長範囲とマーク深さ及びマーク非対称性を含むマーク特性とに関連付けるモデルに基づいてアライメントマークの位置を計算する。

(もっと読む)

半導体装置及びアライメントマークの検出方法

【課題】アライメントマークを形成する膜が薄くなると、マーク本体部とマーク周辺部からのアライメント光の反射率の差が小さくなり、十分なコントラストが得られないことが多くなった。

【解決手段】アライメントパターンを形成するマーク本体部と、マーク周辺部のいずれかに、二次元的な形状を有する回折格子を構成する凹凸を設けることにより、回折格子からの回折光と、非回折光とを利用して、光強度コントラストを大きくすることができる。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わる半導体装置は、ウェハ1内に設けられる第1及び第2半導体チップエリア21,22と、第1及び第2半導体チップエリア21,22内の各々に設けられ、トランジスタが形成される第1素子領域51,52と、第1及び第2半導体チップ51,52間に設けられるダイシングエリア3Aと、ダイシングエリア3A内に設けられ、アライメントマークが形成されるアライメント領域35と、第1素子領域51,52とアライメント領域35との間に設けられ、ウェハ1表面に対して垂直方向に突出した凸部91,92を有する凸部形成領域71,72とを具備し、凸部91,92の上端は、ウェハ1表面より高い位置にあり、トランジスタのゲート電極12上端よりも低い位置にある。

(もっと読む)

アライメントマーク及びアライメント方法

【課題】1mm2以下の小さいチップが多数配置されたウェハのアライメントを容易且つ正確に行えるようにする。

【解決手段】アライメントマーク1は、ウェハに対するパターン転写に用いられるレチクル5のスクライブライン領域3に、素子構成要素のパターンを密集して配置することにより構成されている。アライメントマーク1とその周囲環境との間において十分なコントラストを確保できるため、検査・測定設備がアライメントマーク1をユニークマークとして容易に認識することができるので、アライメントマーク認識不良を防止してウェハのアライメントを正確に実施することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】SiC基板1にデバイスを形成するための第1のトレンチ2およびアライメントマークとして利用するための第2のトレンチ4を形成し、第1のトレンチ2内および第2のトレンチ4内にエピタキシャル層6を成長させた際にもアライメントマークとして利用することができるようにするSiC半導体装置の製造方法を提供する。

【解決手段】第1のトレンチ2の立体角が第2のトレンチ4の立体角より大きくなるように第1のトレンチ2および第2のトレンチを形成する。これにより、エピタキシャル層6を成長させた際に、第1のトレンチ2の底部の成長レートを第2のトレンチ4の底部の成長レートより大きくすることができる。このため、SiC基板1の表面を平坦化した際に、第2のトレンチ4が形成されていた部分に表面が凹まされた凹部7が形成されている状態にすることができ、この凹部7をアライメントマークとして利用することができる。

(もっと読む)

マーク位置検出方法および装置

【課題】露光装置において、デバイス製造現場で発生するWISを高精度に補正するアライメント方法を提供する。

【解決手段】マーク信号の特徴を定量的に表した複数のマーク特徴量を算出し、各マーク特徴量からWIS予測量を算出してアライメント結果を補正する。各マーク特徴量からWIS予測量を算出するための変換係数は、デバイス製造現場で実施する重ね合わせ検査の結果を露光装置へ入力することで更新する。これにより、デバイス製造プロセスが変化するような状況においても、WISを除去した高精度なアライメントを行うことが可能となる。また、各ショットのマーク特徴量を統計計算して「マーク特徴量のショット配列成分」を算出し、重ね合わせ検査の結果より更新した「各ショット配列成分の変換係数」を用いて、「ショット配列補正値のWIS予測量」を算出し、アライメント時のショット配列補正値を補正する。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜表面のCMPのアライメントマークへの影響を排除し、アライメントマークの検出を精度良く確実に行うことができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、素子分離絶縁膜3上に位置するアライメントマーク部31内のゲート積層膜35を選択的に除去する工程と、周囲がゲート積層膜35で囲まれたアライメントマーク部31内にアライメントマーク32を形成する工程と、半導体基板2の上面に第1の層間絶縁膜15を形成する工程と、アライメントマーク部31内の第1の層間絶縁膜15を選択的に除去する工程と、アライメントマーク32周囲の素子分離絶縁膜3を除去もしくは薄膜化する工程と、アライメントマーク32を用いてフォトリソグラフィーのアライメントを行い、第1の層間絶縁膜15上にパターンを形成する工程と、を有する。

(もっと読む)

アライメントマークおよび位置計測方法

【課題】時間を要せずに高精度に位置座標を測定することが可能となるアライメントマークおよび位置測定方法を提供することを目的とする。

【解決手段】本発明のアライメントマークは、高さまたは深さ方向のいずれかに左右対称の順テーパ状の斜面を備えたことを特徴とすることにより、フォーカスレンズのフォーカシングの移動範囲がアライメントマークのトップとボトムの間にあれば、輝度プロファイルの変化が最大となる点と、最小となる点とを検出でき、そこからアライメントマークの中心位置を測定することが出来る。このため、フォーカスレンズの位置を高精度に制御したり、高度な画像処理機能を必要としたりせず、高速かつ簡便にアライメントを行うことが出来る。

(もっと読む)

基準パターン抽出方法、位置決め方法及び装置、並びに露光装置

【課題】埃等の不着の無い部分から基準パターンの抽出を行えるようにする。

【解決手段】実質的に同一の加工が施された複数の所定領域を有する物体上の該所定領域内に任意に設定される該所定領域よりも小さい面積を有する被計測領域内でユニークな信号特徴を有する基準パターンを抽出する基準パターン抽出方法である。前記複数の所定領域のうち任意に選択される第1所定領域内で、前記被計測領域の信号情報を計測する工程(S12)と、この工程で計測された信号情報に基づいて、前記被計測領域内でユニークな信号特徴を有する候補パターンを抽出する工程(S17)と、前記複数の所定領域のうちの前記第1所定領域とは異なる第2所定領域内で、前記被計測領域を計測する工程S22と、この工程で計測された信号情報に基づいて、前記候補パターンに対応する比較パターンを抽出する工程S23と、前記比較パターンに基づいて、前記候補パターンの前記基準パターンとしての適性を判断する工程S25とを備えている。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】 FRAMの強誘電体容量素子を形成する際に強誘電体を酸素雰囲気中で熱処理しても位置合わせマークの溝に埋設するW膜の酸化を防止することができる

【解決手段】 強誘電体容量をメモリとして用いた半導体装置の製造に際して、溝状に掘って形成した位置合わせマーク1に埋設したW膜2が酸化することを防止した半導体装置の製造方法において、該強誘電体容量を形成する前に、該W膜2をP−SiN(SiON)からなる酸化防止膜3によって覆い、次いで、該酸化防止膜3に熱処理を行って予め熱収縮させるように構成する。

(もっと読む)

位置合わせ装置、露光装置及びデバイス製造方法

【課題】 EUV光を使用した場合であっても高いスループットを維持するとともに高精度な位置合わせが可能な位置合わせ装置を提供する。

【解決手段】 1nm以上50nm以下の波長の光を使用して照明される露光パターンを有するマスクを保持するマスクステージと、被露光体を保持するウェハステージとを位置合わせする位置合わせ装置であって、前記マスクまたは前記マスクステージに形成されるとともに位置合わせに使用される第1の基準パターンと相似する第2の基準パターンが形成された基板と、前記基板を反射若しくは透過した光を検出する検出部とを有し、前記基板及び前記検出部は、中空の筐体を形成し、当該中空の筐体の内部にガスを導入したことを特徴とする位置合わせ装置を提供する。

(もっと読む)

マーク計測方法及び装置、露光方法及び装置、並びに露光システム

【課題】 スキャタロメトリを用いて、アライメントを高精度にかつ効率的に行う。

【解決手段】 ロットの先頭ウエハ上のウエハマークからの所定次数の回折光の強度を波長別に検出するステップ102と、その検出結果に基づいてスキャタロメトリ解析によってそのウエハマークの断面形状を求め、この断面形状からそのウエハマークの位置のオフセットを求めるステップ103と、そのウエハ又は2枚目以降のウエハ上のウエハマークの位置をアライメントセンサを用いて計測するステップ104と、この計測値をそのステップ103で求められたオフセットを用いて補正し、この補正された結果に基づいてそのウエハのアライメントを行うステップ105とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 少ない工程でアライメントマークとして利用できる段差を形成することが出来る、半導体装置の製造方法を提供する。

【解決手段】 基板の表面又は基板上に形成した第1の膜の表面に、複数の凹部を形成する第1の工程と、凹部の内部に選択的に第2の膜を形成する第2の工程と、少なくとも1つの凹部及びその近傍を含む第1の領域に局所的エッチングを行って、第1の領域内の第2の膜の表面とその近傍との間に段差を形成する第3の工程とを備える。段差が形成された位置をアライメントマークとして利用する。

(もっと読む)

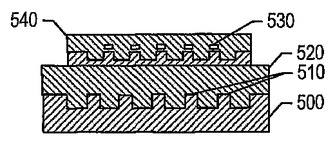

位置合わせマークを有するインプリント・リソグラフィ・テンプレート

本発明の一実施形態は、インプリント・テンプレートのバルク材料に埋め込まれた位置合わせマークを備える、インプリント・リソグラフィのためのインプリント・テンプレートである。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]