Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

21 - 40 / 480

半導体装置及びその製造方法

【課題】ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにする。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

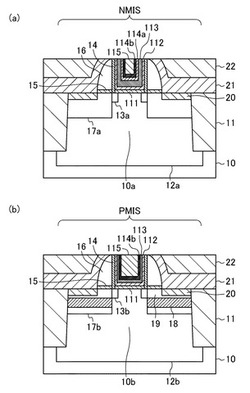

半導体装置及びその製造方法

【課題】さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現する。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート絶縁膜30は、ソース領域51とドレイン領域52との間の領域の上に設けられる。ゲート電極40は、ゲート絶縁膜30の上に設けられる。空乏層42は、P型半導体層41とP型半導体層41の下層(ゲート絶縁膜30)との接合面に生じる。温度が変化すると、ゲート電極40内部の空乏層42の領域が変化し、チャネル形成に対するゲート電圧の影響が変化するので、閾値電圧は通常のMOSトランジスタの場合よりも変化する。このことを利用し、MOSトランジスタが所望の温度特性を有するよう制御されるので、温度補正回路が不要になる。よって、回路規模が小さくなる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

表示装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

21 - 40 / 480

[ Back to top ]