Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

221 - 240 / 480

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

半導体装置の製造方法

【課題】 製造プロセスが比較的容易で、かつMOSFETの特性のばらつきを抑えることができる半導体装置の製造方法を提供する。

【解決手段】 Si基板1上に、界面酸化膜5,5a、ゲート絶縁膜6、金属ゲート電極7およびポリシリコンゲート電極8を順次形成してパターニングし、側面にシリコン酸化膜10を形成し、さらにサイドウォール17を形成する。サイドウォール17をマスクとしてSiGe−p型S/D18a、n型S/D20およびp型S/D21を形成した後、サイドウォール17を除去し、露出したシリコン酸化膜10をマスクとして、エクステンション層12,14,25,27およびハロー層13,15,26,28を形成する。さらにシリコン酸化膜10を介して、金属ゲート電極7などの側面にサイドウォール33を形成した後、サイドウォール33をマスクとして、金属シリサイド35を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のシリサイド層と第2のシリサイド層間が断線することを防止すると共に、表面に高抵抗シリサイド層の形成されていない第1,第2のシリサイド層を実現する。

【解決手段】第1のゲート電極14a上に形成された第1のシリサイド層20a1を有する第1のMISトランジスタNTrと、第2のゲート電極14b上に形成された第2のシリサイド層22b1を有する第2のMISトランジスタPTrとを備え、第1のゲート電極14aと第2のゲート電極14bとは、半導体基板10上に一体化形成されており、第1のシリサイド層20a1と第2のシリサイド層22b1とは、第1のシリサイド層20a1及び第2のシリサイド層22b1よりも膜厚が厚い第3のシリサイド層23を挟んで接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】抵抗素子の膜厚が薄くても、抵抗素子と上層配線と接続する為のコンタクトホールを形成する際に、コンタクトホールが抵抗素子を突き抜けてしまうことを防止する半導体装置及びその製造方法を提供する。

【解決手段】基板上にゲート絶縁膜4を形成し、ゲート絶縁膜4上に第1の金属膜5、および第2の金属膜6を含む積層膜を形成し、ゲート電極形成領域及び抵抗素子部形成領域に前記積層膜が残るように、パターニングを行う。その後、ゲート電極形成領域及び前記抵抗素子部形成領域に、コンタクトホール形成領域を設定し、コンタクトホール形成予定領域を保護した状態で、抵抗素子形成予定領域の前記第2の金属膜6を除去し、その後に前記積層膜を覆うように層間膜9を形成し、コンタクトホール形成予定領域に形成された前記層間膜9を除去し、前記第2の金属膜6に達するコンタクトホールを形成する工程とを具備する。

(もっと読む)

半導体装置、およびその製造方法

【課題】良好な形状のキャップ層を形成して、容易に適した仕事関数に制御することができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、high−k膜2および第1のゲート電極膜3が積層したゲートパターンが形成されるとともに、ゲートパターンをマスクとして、第1導電型および第2導電型のソース・ドレイン領域12を形成する。次に、ゲートパターンの周囲を含む全面に層間絶縁膜14を形成する。次に、第1導電型のMISFET形成領域8の第1のゲート電極膜を除去して溝部20aを形成する。次に、溝部20aの底面および側面を含む全面に積層するようにキャップ層15を形成する。次に、溝部20aを埋め込むように第2のゲート電極膜16を形成する。次に、第2導電型のMISFET形成領域9の第1のゲート電極膜3の表面が露出するように除去しキャップ層15を拡散する。

(もっと読む)

半導体装置とその製造方法

【課題】接合深さが深くなるが抑制され、低抵抗化された低濃度不純物領域を備えた半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、第1のゲート電極103a、第1の不純物を含む第1の不純物領域106a、並びに第1のゲート電極の側面上に形成された第1の内側サイドウォールスペーサ107a及び第1の外側サイドウォールスペーサ109aを有する内部トランジスタと、第2のゲート電極103b、第1の不純物と同一導電型の第2の不純物を含む第2の不純物領域106b、並びに第2のゲート電極103bの側面上に形成された第2の内側サイドウォールスペーサ107b及び第2の外側サイドウォールスペーサ109bを有する入出力トランジスタとを備えている。第2の内側サイドウォールスペーサ107bは、第2の外側サイドウォールスペーサ109bとの界面領域に第2の不純物を含有している。

(もっと読む)

CMISトランジスタの製造方法

【課題】本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供する。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

(もっと読む)

半導体装置の製造方法

【課題】生産性を損なうことなく、MISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1の主面s1のNMIS領域RNには素子用pウェルpwを、PMIS領域RPには素子用nウェルnwを形成した後、主面s1に順に形成したゲート絶縁膜GIおよび第1多結晶シリコン膜E1aを透過させるようにしてアクセプタとなる不純物イオンを注入して、チャネル領域CHの不純物濃度を調整する。その後、第1多結晶シリコン膜E1aおよびその上に形成した第2多結晶シリコン膜のうち、NMIS領域RNにはドナー不純物を、PMIS領域RPにはアクセプタ不純物を注入した後、これらを加工して、n型のゲート電極とp型のゲート電極とを形成する。ゲート絶縁膜GIは、シリコン基板1の主面を酸化した後、炉体内において一酸化二窒素雰囲気中で熱処理を施すようにして形成する。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することを可能にする。

【解決手段】配列された複数の素子形成領域AR1を含むp型半導体層103における隣り合う素子形成領域AR1間に平行な2つの溝TRを形成し、個片化時には2つの溝TRの間に形成された凸部120を切断する。この構成により、スクライブ領域SR全体に溝TRを形成する必要が無くなるため、溝TRの幅を例えばダイシングブレードの厚さやレーザスポットの径よりも小さくすることが可能となる。この結果、微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することが可能となる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

(もっと読む)

半導体装置

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

半導体装置

【課題】メタルをゲート電極材料に用いたCMIS素子の閾値を低減する。

【解決手段】p型MISトランジスタQpのゲート絶縁膜5上に設けられたp型ゲート電極7は、順に、カチオン比でAlが10%以上50%以下のTiAlNから構成される第1金属膜30と、TiNから構成され、膜厚が5nm以下の第2金属膜31と、Siを主成分として含有する導電体膜32とが積層された構造を有している。また、n型MISトランジスタQnのゲート絶縁膜5上に設けられたn型ゲート電極6は、順に、第2金属膜31と、導電体膜32とが積層された構造を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の信頼性および半導体装置の性能を確保可能である半導体装置の製造方法および半導体装置を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、Si基板100上にゲート絶縁膜103を形成するゲート絶縁膜形成工程と、ゲート絶縁膜103上に第1の金属膜を形成する第1の金属膜形成工程と、第1の金属膜上に金属電極104を構成する第2の金属膜を形成する第2の金属膜形成工程と、熱処理を行なってゲート絶縁膜103と第1の金属膜との間にゲート絶縁膜103と第1の金属膜との反応膜118を形成する反応膜形成工程とを行なって、第1の金属膜形成工程時のゲート絶縁膜103の損傷を回復させている。

(もっと読む)

単結晶半導体膜の結晶性評価方法及び半導体基板の作製方法

【課題】良好な結晶性を有し高性能な半導体素子を形成することを可能とする半導体基板を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定し、単結晶半導体層にレーザ光を照射し、単結晶半導体層を部分溶融状態として再結晶化し、結晶欠陥を修復する。再結晶化後の単結晶半導体層は深さ方向の濃度分布において、炭素濃度が極大を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用い、PMOS、NMOSに適したしきい値電圧を有するCMOSFETを実現する。

【解決手段】 潮解性のあるランタン酸化膜をキャップ膜として用いずに、ハフニウムを含有する絶縁膜111を形成する前にシリコン酸化膜104上にランタンを含有する絶縁膜を形成して、ハフニウムを含有する絶縁膜111で保護するとともに、エッチングによりダメージを受けたPMOS領域にSiGe層108をエピタキシャル成長させることによって、PMOS、NMOSそれぞれに適したしきい値電圧を有する構造を形成する。

(もっと読む)

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

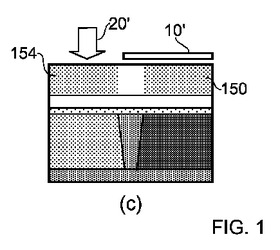

半導体デバイスの製造方法および半導体デバイス

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い単結晶半導体層及び半導体装置を、少ない作製工程で得ることを課題とする。

【解決手段】絶縁膜が形成された単結晶半導体基板に、イオンビームを照射し、前記単結晶半導体基板中に損傷領域を形成し、液状ガラスよりも密度の高い液体上に、前記液状ガラスを浮かべて板状にし、前記板状の液状ガラス上に、前記損傷領域が形成された単結晶半導体基板を、前記絶縁膜と前記液状ガラスが向き合うように配置し、前記板状の液状ガラスと前記単結晶半導体基板を徐冷することにより、前記板状の液状ガラスからガラス基板を形成すると同時に、前記ガラス基板と前記単結晶半導体基板を接合させ、前記損傷領域に沿って、前記単結晶半導体基板から単結晶半導体層を分離する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造のデュアル・メタルゲートを有する半導体装置において高集積化を進展させつつ、PN境界部配線の断線や高抵抗化等の問題を防止できる半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極122aは、第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタのゲート電極122bは、第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第3の金属含有導電膜113は、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されている。

(もっと読む)

221 - 240 / 480

[ Back to top ]